Sytuację, gdy do zaprogramowania ISP trzech układów potrzebne były trzy różne programatory, można było uznać za naturalną na początku wdrażania standardów ISP (15 lat temu), lecz teraz jest to kompletny anachronizm. Dotychczasowa sytuacja jest tym bardziej absurdalna, że dzięki powszechnemu stosowaniu uniwersalnych języków opisu sprzętu (HDL) do realizacji projektów na układach PLD, korzystanie z układów pochodzących od różnych producentów (choćby z powodu fluktuacji ich cen) jest rzeczą zupełnie naturalną. W związku z tym proponujemy wykonanie uniwersalnego programatora, za pomocą którego można programować w systemie układy CPLD/FPGA firm: Altera, Atmel, Lattice i Xilinx oraz mikrokontrolery AVR.

Możliwości prezentowanego programatora

|

ISP vs JTAG vs SPI

Na początek drobne wyjaśnienie pojęć, które dość często są mylone, a których rozróżnienie jest dość istotne.

AVR-y jako pierwsze z grupy mikrokontrolerów popularnych wyposażono w możliwość programowania w systemie. Atmel wykorzystał do tego celu interfejs SPI (Serial Peripherial Interface), który w specyficznych warunkach spełnia rolę interfejsu wejściowego dla wbudowanego w mikrokontrolery programatora pamięci Flash. Dane są wprowadzane i odczytywane szeregowo w sposób synchroniczny.

Co to znaczy ISP?Mianem ISP (od angielskiego In System Programmable) jest określany sposób programowania pamięci Flash/EEPROM wbudowanej w układy scalone (przede wszystkim mikrokontrolery, PLD i pamięci nieulotne) po ich zamontowaniu w urządzeniu. Programowanie ISP odbywa się zazwyczaj poprzez interfejs SPI, JTAG lub RS232. |

Nieco inaczej wygląda sytuacja w przypadku układów PLD, które w większości przypadków wyposażono w interfejs JTAG (zgodny z jedną z norm: IEEE1149 lub IEEE1532) – jak ma to miejsce w większości układów CPLD, lub synchroniczny interfejs szeregowy służący do konfiguracji układów FPGA. Zarówno w przypadku klasycznego JTAG-a jak i interfejsów przystosowanych do konfigurowania układów FPGA istnieje możliwość programowania/konfigurowania pojedynczego układu lub wielu układów połączonych w tzw. łańcuch JTAG (rys. 1).

Rys. 1. Przykładowa ścieżka JTAG z kilkoma układami

Niezależnie od rodzaju interfejsu zastosowanego do programowania (JTAG/SPI, czasami także RS232), programowanie/konfigurowanie pamięci układu zamontowanego w urządzeniu jest nazywane ISP od In System Programmable. Programator prezentowany w artykule emuluje interfejsy: JTAG, SPI oraz natywne tryby konfiguracji FPGA najpopularniejszych rodzin układów PLD i mikrokontrolerów AVR, pozwalając programować te układy w systemie (ISP).

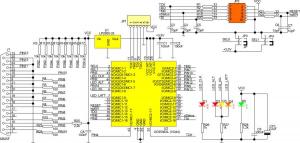

Rys. 2. Schemat elektryczny programatora

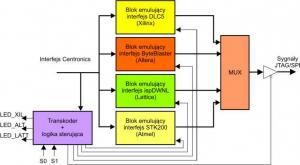

Schemat elektryczny programatora pokazano na rys. 2. Jego budowa jest bardzo prosta dzięki zastosowaniu układu programowalnego firmy Xilinx (U2), w którym zintegrowano wszystkie bloki funkcjonalne emulowanych interfejsów. Projekt przygotowano w języku VHDL, dzięki czemu można go zmodyfikować adekwatnie do własnych potrzeb, na przykład dodając opisy HDL kolejnych interfejsów ISP. Na rys. 3 pokazano uproszczony schemat blokowy projektu zaimplementowanego w układzie U2.

Rys. 3. Schemat blokowy projektu zaimplementowanego w układzie U2

Układ U2 należy do rodziny XC9500XL produkowanej przez firmę Xilinx. Jest on przystosowany do zasilania napięciem 3,3 V, ale wszystkie jego linie wejściowe są przystosowane do współpracy z układami cyfrowymi zasilanymi napięciem 5 V, a poziomy napięć na liniach wyjściowych są zgodne ze standardem TTL. Napięcie zasilające jest stabilizowane przez układ U1 (stabilizator LDO – Low Drop Out), na wejście którego jest podawane napięcie +5 V z urządzenia, w którym znajduje się programowany układ. Napięcie zasilające na wejściu stabilizatora nie może być niższe niż ok. 3,7 V, ponieważ nie będzie on pracował poprawnie.

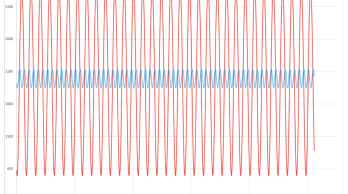

Jumpery JP3 i JP4 służą do ustalenia tryby pracy programatora. Wybór użytkownika jest sygnalizowany za pomocą trzech diod LED (D2, D3 i D4), przy czym w trybie STK200 świecą jednocześnie diody D2 (LED_ALT) i D4 (LED_LATT). Dioda D1 służy do monitorowania sygnałów zegarowych każdego z interfejsów, a dioda D5 sygnalizuje dołączenie zasilania do złącza JP2. Złącze to służy do dołączenia programatora do programowanego układu, a wyprowadzenie sygnałów na nim jest zgodne z ByteBlasterem, ByteBlasterem MV oraz interfejsem ispDOWNLOAD.