„Bałagan” napięciowy zaczął poważnie dotykać także układy wyposażone w interfejsy I2C i SMbus. Proste urządzenie prezentowane w artykule, problem ten eliminuje począwszy od napięcia zasilającego o wartości 1,0 VDC.

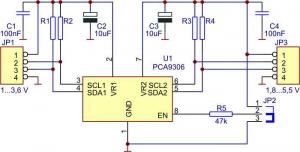

Schemat elektryczny proponowanego rozwiązania pokazano na rys. 1. Skuteczność i prostota tego rozwiązania wynika z zastosowania wyspecjalizowanego układu scalonego produkowanego przez firmę NXP – PCA9306.

Rys. 1. Schemat elektryczny translatora napięciowego

Zgodnie z notą katalogową tego układu, zakres poprawnych wartości napięć zasilających jest dość duży, ale producent zaleca utrzymanie co najmniej 1-woltowej różnicy napięć pomiędzy stroną „niskonapięciową” (VR1, od strony JP1) a „wysokonapięciową” (VR2, od strony JP3). Próby przy VR1=1,2 V i VR2=1,8V wykazały, że układ pracuje prawidłowo – testy przeprowadzono przy częstotliwości sygnału na linii SCL wynoszącej 1,2 MHz, ale dane zawarte w nocie katalogowej sugerują możliwość uzyskania jeszcze lepszych wyników (nawet do 19 MHz!).

Układ PCA9306 wyposażono w wejście EN (Enable), umożliwiające logiczne rozłączenie buforowanych magistral (zwarte styki 2-3 JP2, podczas normalnej pracy powinny być zwarte styki 1-2).

Na schemacie elektrycznym i w wykazie elementów nie podano wartości rezystancji rezystorów R1…R4, co wynika z konieczności dopasowania ich do wymogów aplikacji (napięcia zasilającego, długości przewodów, częstotliwości synchronizującej przesył danych itp.). W tab. 1 zestawiono przykładowe zalecane wartości rezystancji dla różnych napięć zasilających, które umożliwiają wykorzystanie nominalnych parametrów układu PCA9306.

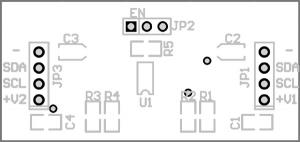

Schemat montażowy płytki drukowanej translatora napięciowego pokazano na rys. 2.

Rys. 2. Schemat montażowy od strony elementów

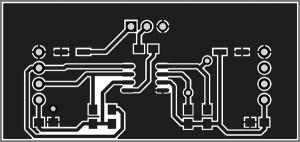

Rys. 3. Widok ścieżek od strony elementów

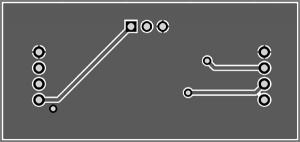

Rys. 4. Widok ścieżek od strony lutowania

Tab. 1. Zalecane wartości rezystancji R1…R4 dla różnych napięć zasilających i prądów obciążających wyjścia interfejsów I2C

| Vrx [V] |

R1…R4 przy Iout=10mA [?] |

R1…R4 przy Iout=3mA [?] |

| 5 | 330 | 1,6k |

| 3,3 | 220 | 1,1k |

| 2,5 | 150 | 750 |

| 1,8 | 100 | 510 |

| 1,5 | 82 | 390 |

| 1,2 | 62 | 300 |

Wykaz elementów

| Rezystory | |

| R1, R2 | dobrać zgodnie z opisem z tab. 1 |

| R3, R4 | dobrać zgodnie z opisem z tab. 1 |

| R5 | 47 k? |

| Kondensatory | |

| C1, C4 | 100 nF/0805 |

| C2, C3 | 10µF/10V SMD-A |

| Półprzewodniki | |

| U1 | PCA9306D |

| Inne | |

| JP1, JP3 | gold-piny 4×1 |

| JP2 | gold-piny 3×1 |