Producenci układów PLD nie zasypują gruszek w popiele: w pierwszych dniach grudnia Altera ogłosiła wprowadzenie na rynek nowej rodziny układów CPLD z rodziny MAX V, które uzupełnią portfolio nowoczesnych układów tego typu, reprezentowanych dotychczas przez rodzinę MAX II. W skład rodziny MAX V wchodzą układy o szerokim spektrum zasobów logicznych (liczba „makrokomórek” od 32 w układzie 5M40 do 1700 w układzie 5M2210), konfigurowalnej pamięci EEPROM o pojemności 8 kb, a także wewnętrznym generatorze taktującym z cyfrową pętlą PLL. Generator sygnału zegarowego charakteryzuje się niewielką dokładnością częstotliwości generowanego przebiegu (która mieści się w przedziale 3,9 do 5,3 MHz), ale jest wystarczająca do wielu aplikacji wymagających sygnału synchronizującego. Najmniejszy z układów udostępnia konstruktorom 54 linie I/O, ich maksymalna liczba wynosi 271, w tym 4 globalne linie zegarowo-zerujące.

Projekty dla układów MAX V można przygotowywać za pomocą dostępnego bezpłatnie pakietu narzędziowego Quartus II w wersji od 10.1 począwszy, który jest dostępny pod adresem: https://www.altera.com/download/dnl-index.jsp.

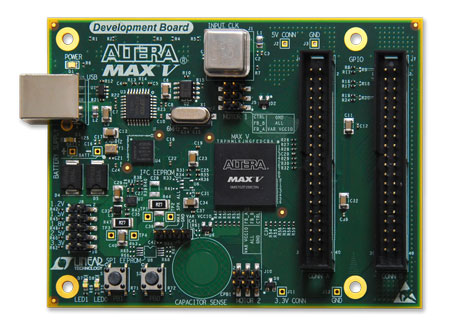

Zestaw uruchomieniowy dla układów MAX V

Producent opracował tani zestaw uruchomieniowy dla ukłądów MAX V, który ma być dostępny w styczniu 2011, jego opis jest dostępny pod adresem: http://www.altera.com/products/devkits/altera/kit-max-v.html.

Szczegółowe informacje na temat układów MAX V są dostępne na stronie producenta: www.altera.com/pr/maxv.