Realizacja projektu opisanego w książce „Układy programowalne dla początkujących” w rozdziale zatytułowanym „Pierwszy projekt” może być wykonana zarówno przy użyciu zestawów uruchomieniowych produkowanych przez firmy KAMAMI (ZL14PLD + ZL15PLD) jak i DIGILENT (SK-CRII-L-G), gdyż wymagania sprzętowe tego projektu są spełnione w obu przypadkach. Zadaniem prezentowanego rozwiązania jest odczyt stanu przycisków i prezentacja uzyskanej informacji na wyświetlaczu LED.

Projekt przedstawiony w artykule bazuje na książce „Układy programowalne dla początkujących„, której autorem jest Andrzej Pawluczuk. Projekt przedstawiony w artykule bazuje na książce „Układy programowalne dla początkujących„, której autorem jest Andrzej Pawluczuk. |

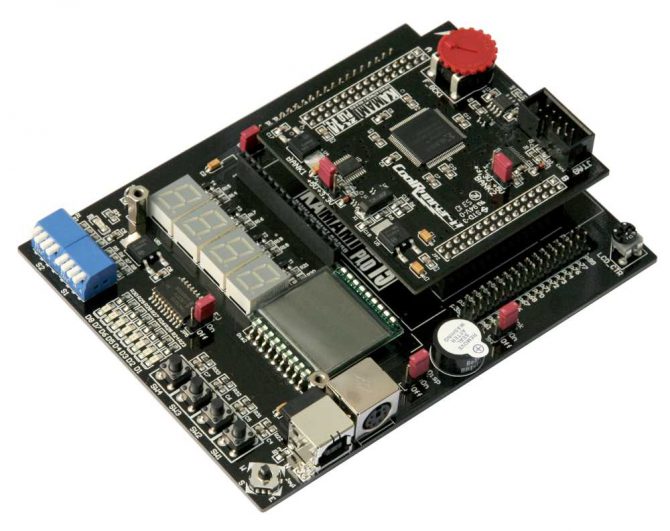

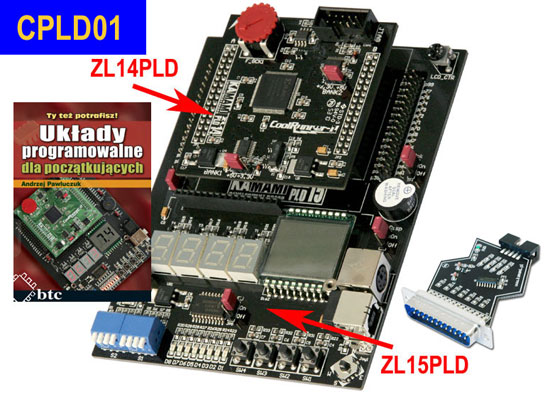

Rys. 1. Sprzętowe środowisko uruchomieniowe wymagane w projekcie

Chociaż koncepcja rozwiązania w obu przypadkach jest identyczna, ze zrozumiałych względów, wynikających z sposobu sterowania podzespołów funkcjonalnych przyłączonych do układu CPLD, opisy projektu zawierają niewielkie różnice. Dla przypomnienia, do istotnych różnic dotyczących środowiska sprzetowego należą:

- częstotliwość sygnału zegarowego,

- sposób sterowania wyświetlaczem.

|

Sklep KAMAMI.pl oferuje w promocyjnej cenie zestawy składające się z płytek ZL14PLD i ZL15PLD, ksiązki „Układy programowalne dla początkujących” oraz programatora ISP dla układów CPLD i FPGA firmy Xilinx. |

Projekt wymaga środowiska sprzętowego pokazanego na rysunku 1. Pokazuje on, że do układu CPLD do poprawnego działania całości konieczne jest przyłączenie:

- sygnału zegarowego – Clk (taki generator znajduje się w zestawie uruchomieniowym),

- sygnału z przycisku pełniącego funkcję zerowania – Reset (przycisk, którego naciśnięcie powoduje wystąpienie stanu logicznego zera na odpowiednim wejściu układu CPLD),

- zestawu przycisków – KeyIn0, KeyIn1, KeyIn2, KeyIn3 (zbioru przycisków, których naciśnięcie generuje stan logicznego zera na odpowiednim wejściu układu CPLD),

- czterocyfrowego siedmiosegmentowego wyświetlacza LED pracującego w trybie multipleksowanego wyświetlania, który jest sterowany przez wyjścia układu CPLD w zakresie włączania poszczególnych segmentów (SegA, SegB, SegC, SegD, SegE, SegF, SegG, SegK) oraz włączania poszczególnych cyfr wyświetlacza (DSel0, DSel1, DSel2, DSel3).

Rys. 2. Schemat blokowy prezentowanego projektu