Twórcą architektury Power jest firma IBM, której pierwotnym zamiarem było opracowanie 32-bitowych, RISC-owych rdzeni do różnych zastosowań. Do przedsięwzięcia zaangażowało się z czasem więcej firm, które współpracują ze sobą nad dalszym rozwojem i implementacjami tej architektury w ramach powstałej w 2004 roku organizacji POWER.org. Jej nazwa (jednocześnie nazwa promowanej architektury) jest akronimem od angielskich słów Performance Optimization With Enhanced RISC, które doskonale oddają cele stawiane sobie przez IBM i współpracujące firmy.

| Mikrokontrolery z rodziny SPC56 są dostępne w KAMAMI.pl. |

Jednym z kierunków aplikowania rdzeni PowerPC były nowoczesne mikrokontrolery, których jednym z producentów jest firma STMicroelectronics, w portfolio której znajduje się rodzina SPC56, wyposażona w rdzenie z serii e200, będące ewolucyjnymi następcami architektur POWER4 i POWER5 oraz PowerPC 400.

| O mikrokontrolerach SPC56 pisaliśmy już w artykule. |

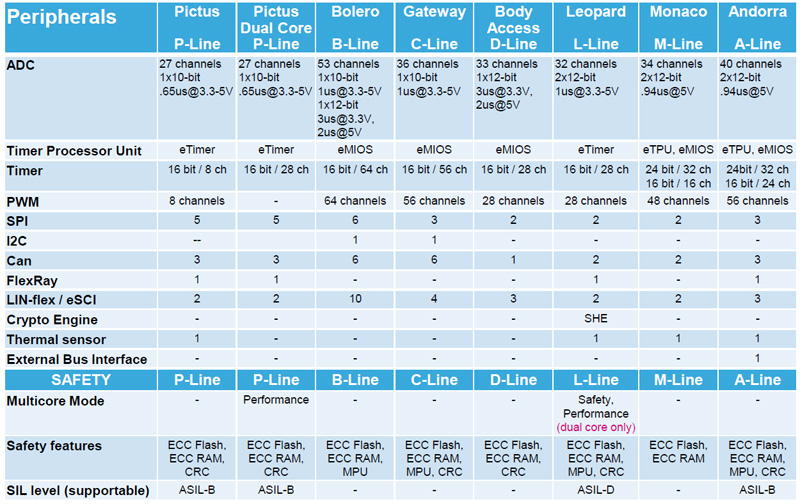

Rys. 1. Rdzenie stosowane w mikrokontrolerach SPC56 firmy STMicroelectronics

Firma STMicroelectronics stosuje w produkowanych przez siebie mikrokontrolerach SPC56 trzy wersje rdzeni (rysunek 1), których cechy i możliwości są dobrane do wymogów docelowych aplikacji.

Najprostszy ze stosowanych rdzeni – e200z0 – przypomina klasyczne rdzenie mikrokontrolerowe, nie jest wyposażony w FPU czy MMU, ma zintegrowaną także nieco prostszy funkcjonalnie system sprzętowego wspomagania debugowania. Maksymalna częstotliwość taktowania rdzeni e200z0 produkowanych w technologiach używanych przez STMicroelectronics wynosi do 100 MHz.

Rdzeń e200z3 jest rozbudowana wersją e200z0, zintegrowano w nim m.in. koprocesor zmiennoprzecinkowy oraz jednostkę zarządzania pamięcią MMU, przystosowaną do zarządzania 8 wydzielonymi regionami. Rdzeń e200z3 komunikuje się z otoczeniem za pomocą dwóch magistral (specyfikacja AMBA 2.0 v6 AHB), wyposażono go także w jednostkę wspomagającą debugowanie Nexus 3 (IEEE-ISTO 5001-2003), której możliwości są porównywalne z nieco bardziej popularnym rozwiązaniem firmy ARM – CoreSight. Maksymalna częstotliwość taktowania rdzeni e200z3 produkowanych w technologiach używanych przez STMicroelectronics wynosi do 100 MHz.

Najbardziej zaawansowane rdzenie z serii PowerPC dostępne w mikrokontrolerach SPC56 – oznaczone symbolem e200z4 – są rozwinięciem e200z3: wyposażono jej dodatkowo koprocesor DSP oraz pamięć cache dla instrukcji i danych, zastąpiono 4-poziomowy pipelineing systemem 5-poziomowym, a MMU przystosowano do obsługi 16 niezależnych regionów pamięci. Maksymalna częstotliwość taktowania rdzeni e200z4 produkowanych w technologiach używanych przez STMicroelectronics wynosi do 150 MHz.

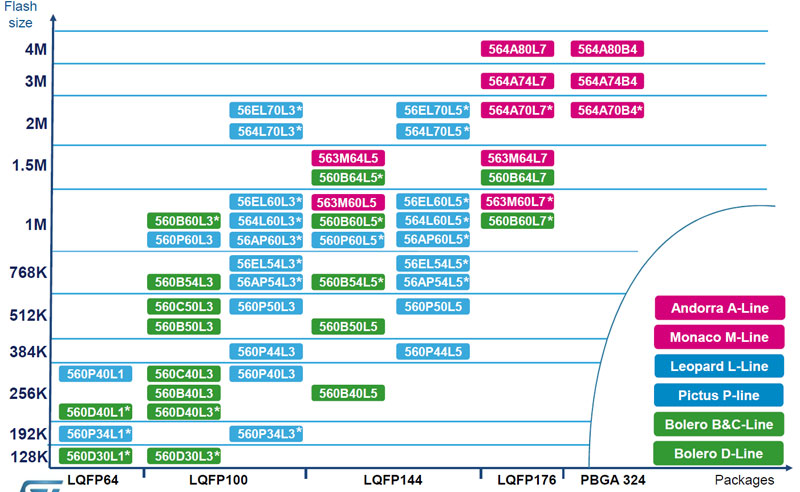

Rys. 2. Wybrane cechy mikrokontrolerów sz rodziny SPC56 (gwiazdką oznaczono układy planowane do wdrożenia do produkcji)

Firma STMicroelectronics produkuje 7 grup mikrokontrolerów SPC56, które są przeznaczone dla różnych aplikacji. Na rysunku 2 pokazano mikrokontrolery aktualnie dostępne i planowane do szybkiego wdrożenia do produkcji (zaznaczone na rysunku gwiazdkami), wraz z przypisaniem układów do dostępnych wersji obudów. Pomimo bogatego wyposażenia i zastosowania potężnego rdzenia, producent oferuje mikrokontrolery SPC56 także w niewielkich i łatwych w montażu obudowach (LQFP64/100), dzięki czemu można je stosować w aplikacjach niskobudżetowych, czemu sprzyjają także niewygórowane ceny mikrokontrolerów.

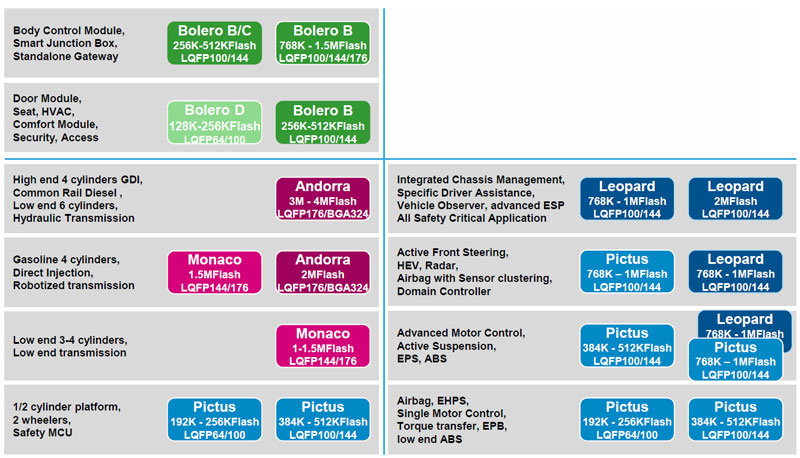

Rys. 3. Podstawowe cechy podrodzin mikrokontrolerów SPC56

Podział rodziny mikrokontrolerów SPC56 na podrodziny pokazane na rysunku 2 wiąże się z optymalizacją ich wyposażenia pod kątem wymogów docelowych aplikacji, przy czym wszystkie są „celowane” w aplikacje samochodowe – rysunek 3. Najtańsze i przy tym najbardziej uniwersalne mikrokontrolery (podrodziny Bolero i Pictus) są montowane w najmniejszych obudowach (między innymi) – LQFP64, wyposażono jej w pamięć Flash o pojemności do 256 kB (lub 512 kB, wersje w obudowach LQFP100), pozostałe elementy wyposażenia wewnętrznego pokazano w tabeli 1. Aplikacyjny „przechył” mikrokontrolerów SPC56 w kierunku automotive dobrze widać w ich wyposażeniu: interfejs I2C nie jest w nich oczywistym elementem wyposażenia, każda podrodzina ma natomiast wbudowany CAN, LIN, większość także FlexRay.

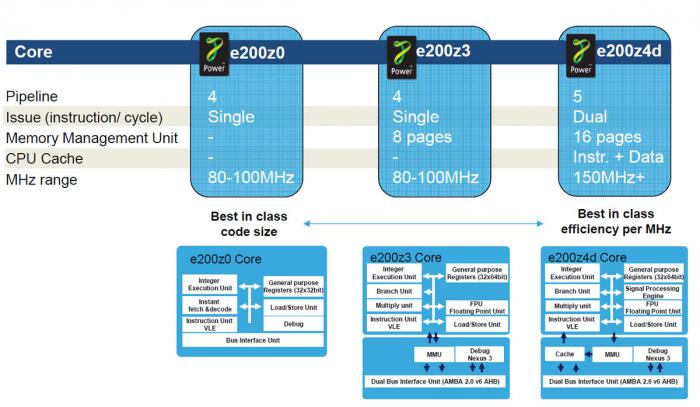

Tab. 1. Wyposażenie podrodzin mikrokontrolerów SPC56