Jeden z potentatów rynku logiki programowanej (PLD) – amerykańska firma Altera – wprowadziła na rynek trzy rodziny zaawansowanych układów FPGA (Cyclone V SoC, Arria V SoC oraz Arria 10 SoC), w których zintegrowano także szybkie rdzenie mikroprocesorowe Cortex-A9. Dzięki temu budowa komputera z możliwością rekonfiguracji sprzętowej stała się prosta jak nigdy dotąd.

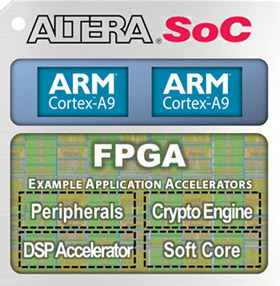

Czy da się zrobić komputer w FPGA? Oczywiście, ale zrobienie takiego urządzenia w sposób klasyczny jest dość kosztowne, skomplikowane i z czasochłonne. W lepszej sytuacji są konstruktorzy, którzy komputery budują na klasycznych mikroprocesorach lub układach SoC (System-on-Chip), które w jednej obudowie integrują „twardy” (czyli zaimplementowany w krzemie) rdzeń mikroprocesora wraz z jego podstawowym otoczeniem oraz rekonfigurowalny sprzęt w postaci matrycy FPGA (rysunek 1). Takie rozwiązania oferuje od niedawna Altera, w ofercie której pojawiły się trzy rodziny SoC (obecnie produkowane są układy z rodzin Arria V SoC i Cyclone V SoC, układy Arria 10 SoC nie są jeszcze dostępne w normalnej dystrybucji).

| Prezentowane w artykule układy Cyclone V SoC są wyposażone w 2-rdzeniowy mikroprocesor Cortex-A9MP. Są więc doskonałą alternatywą dla tradycyjnych mikroprocesorów dla aplikacji, w których konieczne jest zapewnienie wysokiej skali integracji systemu, ochrona własności intelektualnej lub wyposażenie komputera w peryferia o nietypowej funkcjonalności. |

W artykule skupimy się na przybliżeniu możliwości i cech układów Cyclone V SoC, ponieważ są one najlepiej dostosowane do popularnych aplikacji embedded, w których bez przeszkód mogą zastąpić standardowe mikroprocesory. Zastosowano w nich CPU z serii Cortex-A9MP, obecnie dostępne są układy wyposażone w dwa rdzenie tego typu.

Rys. 1. Uproszczony schemat blokowy układu Cyclone V SoC, ilustruje on budowę zintegrowanego systemu uP+FPGA

Altera wprowadziła do produkcji 6 podrodzin tworzących rodzinę Cyclone V, z których trzy są klasycznymi układami FPGA, pozostałe trzy należą do rodziny układów SoC. Najpoważniejszą różnicą pomiędzy klasycznymi układami FPGA i SoC jest wyposażenie tych drugich w „twardy” (czyli wykonany w krzemie, bez możliwości rekonfiguracji), dwurdzeniowy procesor z rdzeniami Cortex-A9.

|

ARM Cortex-A9 w wersji MPCore – rdzeń dla systemów wielordzeniowych Zastosowane w układach SoC Altery rdzenie Cortex-A9 MPCore są zmodyfikowaną wersją rdzeni Cortex-A9, zoptymalizowaną do implementacji w systemach wielordzeniowych. Wyposażono je w blok SCU (Snoop Control Unit), która zajmuje się wspomaganiem arbitrażu, zarządzaniem zawartością pamięci cache, wymianą danych pomiędzy rdzeniami i innymi funkcjami charakterystycznymi dla systemów wieloprocesorowych. |

Poszczególne podrodziny różnią się między sobą także wyposażeniem w szybkie transceivery komunikacyjne (przystosowane do budowy szybkich, szeregowych interfejsów komunikacyjnych):

– w ramach klasycznych rodzin FPGA:

- Cyclone V E – układy o zminimalizowanej cenie i poborze mocy, przeznaczone do stosowania w standardowych aplikacjach DSP i logicznych,

- Cyclone V GX – układy wyposażone w transceivery komunikacyjne (do 12 kanałów) przystosowane do transmisji danych z prędkością do 3,125 Gb/s,

- Cyclone V GT – układy wyposażone w transceivery komunikacyjne (do 12 kanałów) przystosowane do transmisji danych z prędkością do 6,144 Gb/s,

– w ramach rodzin SoC:

- Cyclone V SE – układy z wbudowanymi jednym (przedostatnia litera w symbolu oznaczenia typu to „S”) lub dwoma rdzeniami Cortex-A9, charakteryzujące się relatywnie niską ceną i poborem mocy, przeznaczone do stosowania w aplikacjach embedded, DSP i logicznych,

- Cyclone V SX – układy z wbudowanymi dwoma rdzeniami Cortex-A9, wyposażone w transceivery komunikacyjne (do 9 kanałów) przystosowane do transmisji danych z prędkością do 3,125 Gb/s,

- Cyclone V ST – układy z wbudowanymi dwoma rdzeniami Cortex-A9, wyposażone w transceivery komunikacyjne (do 9 kanałów) przystosowane do transmisji danych z prędkością do 5 Gb/s.

Tab. 1. Porównanie układów SoC z oferty firmy Altera

Tab. 2. Charakterystyka rodzin układów Cyclone V SoC

| Cecha | Cyclone V SE SoC | Cyclone V SX SoC | Cyclone V ST SoC |

| Rdzeń | ARM Cortex-A9 MPCore (dwa rdzenie) | ||

| Maksymalna częstotliwość taktowania CPU | 800 MHz | ||

| Liczba wbudowanych komórek | 25…110k LE | 85…110k LE | |

| Liczba transceiverów szeregowych | – | 9 | |

| Maksymalna prędkość transmisji szeregowej | – | 3,125 Gb/s | 6,144 Gb/s |

| Obsługiwane typy pami ęci | HPS: 32-bity, 400 MHz DDR2/DDR3 z ECC FPGA: 32-bity, 400 MHz, DDR2/DDR3 | ||

| Wbudowane „twarde” interfejsy | HPS: 10/100/1000 EMAC x 2 | HPS: 10/100/1000 EMAC x2 FPGA: x2 PCIe Gen2 | |

Rys. 2. Budowa komórki logicznej tworzącej matrycę FPGA – ALE

Oprócz standardowych, konfigurowalnych zasobów logicznych (LE – Logic Elements) oraz unowocześnionych bloków logicznych ALE (Adaptive Logic Module – rysunek 2), układy Cyclone V są wyposażone w konfigurowalne zasoby specjalizowane w postaci bloków DSP, multiplikatorów, zespołów konfigurowalnych interfejsów pamięci SDRAM (32-bitowe DDR2/DDR3, do 400 MHz), a także syntezerów sygnałów zegarowych bazujących na PLL. Niektóre typy prezentowanych układów producent wyposażył także w „twarde” interfejsy pamięci, a także interfejsy PCIe, konfigurowalne interfejsy I/O przystosowane do pracy z sygnałami LVDS. Budowę komórek linii I/O w układach Cyclone V pokazano na rysunku 3. Warto zwrócić uwagę na fakt wyposażenia komórek I/O w terminatory, które upraszczają budowę szybkich systemów transmisji danych w obrębie płytki drukowanej.

Rys. 3. Budowa pojedynczej linii I/O w układach Cyclone V