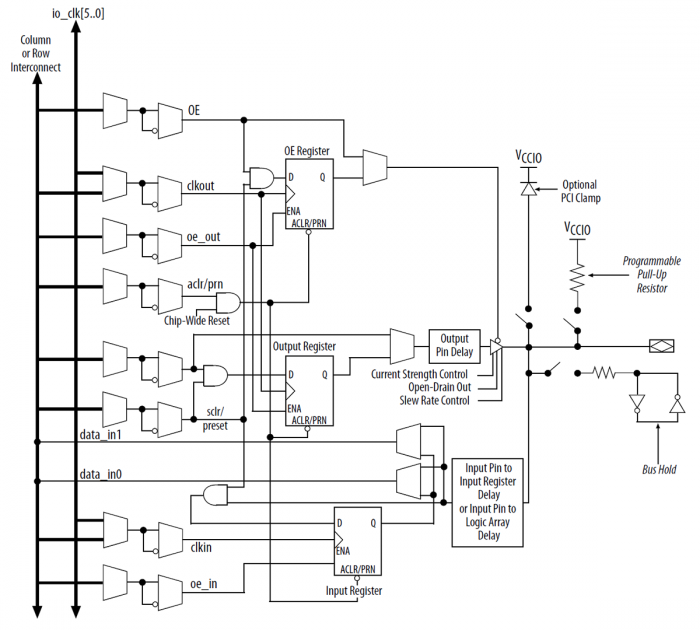

Duże znaczenie dla poprawnej współpracy układu MAX10 z otoczeniem mają linie GPIO, które współpracują z konfigurowalnymi komórkami logicznymi (schemat pokazano na rysunku 6). Linie I/O wyposażono w funkcje programowanego podciągania do plusa zasilania, możliwość pracy w trybie otwarty-dren, system podtrzymywania ostatniego stanu logicznego na wejściu (bus-hold), a także konfigurowalny ogranicznik prądowy, który ogranicza maksymalny prąd wyjściowy do wartości wybranej przez użytkownika (co ma znaczenie m.in. w aplikacjach z szybkimi sygnałami).

Rys. 6. Budowa komórki GPIO w układach MAX10

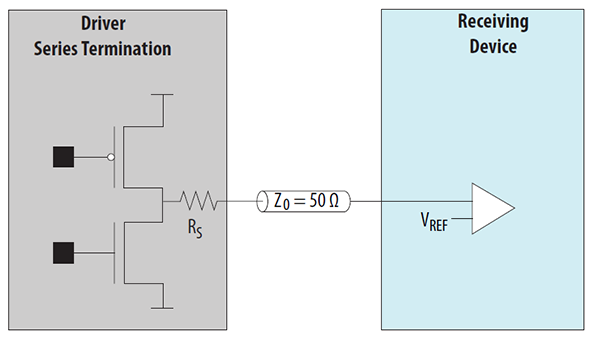

W układach MAX10 linie I/O są przystosowane do współpracy z układami cyfrowymi wyposażonymi w styki fizyczne pracujące w jednym z ponad 30 standardów czasowo-napięciowych, obsługiwanych przez układy MAX10 (m.in. HSTL, SSTL, HSUL, LVDS, PPDS, LVPECL, TMDS itd.). Ponadto komórki GPIO w układach MAX10 wyposażono w aktywowane przez użytkownika rezystory terminacyjne (blok OCT – On-Chip Termination), które można wykorzystywać w szybkich interfejsach komunikacyjnych (rysunek 7).

Rys. 7. Linie I/O w układach MAX10 są wyposażone w rezystory terminacyjne (projektant może je aktywować lub wyłączać, w zależności od potrzeb), które upraszczają projekt PCB z rozprowadzanymi szybkimi sygnałami

Jak wspomnieliśmy na początku, architektura układów MAX10 bazuje na układach FPGA Cyclone IV. Układy te – poza wymienionymi dotychczas zasobami – producent wyposażył także w moduły uniwersalnej, konfigurowalnej pamięci (które użytkownik może łączyć tworząc zespoły o większej pojemności). W zależności od potrzeb aplikacji pamięć może pełnić rolę klasycznej RAM, jedno- lub dwuportowej FIFO, a nawet pseudo-ROM.

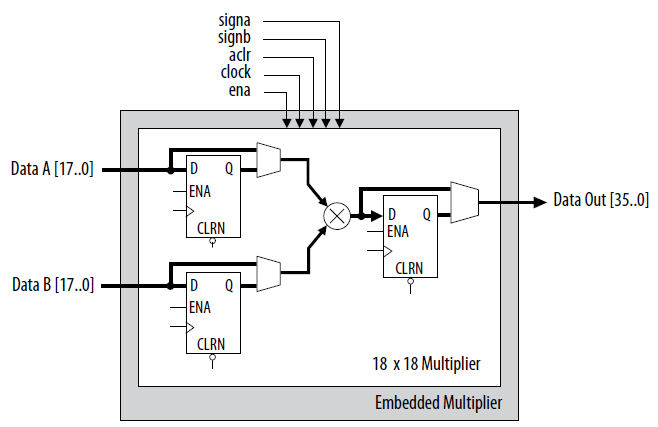

Elementem standardowego wyposażenia układów MAX10 są także wyspecjalizowane komórki wspomagające realizację algorytmów DSP. Można w nich implementować m.in. szybkie jednostki MAC (Multiply-Accumulate), w każdej tego typu komórce (rysunek 8) wykonując działania na dwóch liczbach 9-bitowych (wynik ma 18 bitów) lub 18-bitowych (wynik jest 36-bitowy). Oprogramowanie narzędziowe do syntezy logicznej może automatycznie implementować w fragmenty projektu w multiplikatorach, które mogą pracować synchronicznie (wejścia i wyjście niezależnie) lub asynchronicznie, co przydaje się w projektach szybkiej logiki z handshakingiem.

Rys. 8. Schemat blokowy sprzętowego multiplikatora pracującego w trybie 18×18 bitów – widać możliwości skonfigurowania ścieżki przepływu sygnałów (synchronicznie/asynchronicznie)

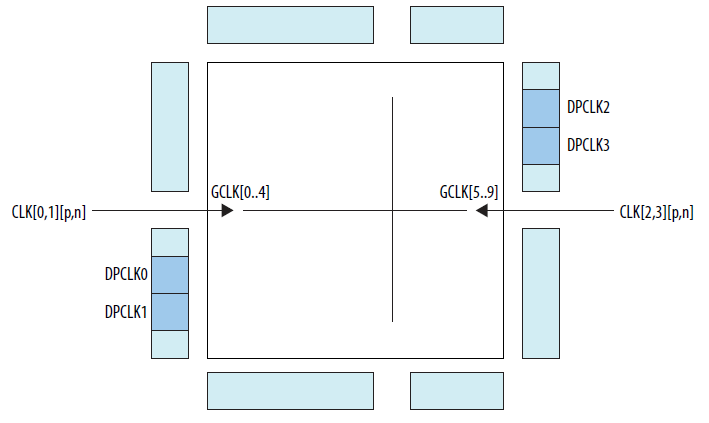

Ostatnim elementem sprzętowym, na który zwrócimy w artykule uwagę, są wewnętrzne syntezery sygnałów zegarowych, w jakie wyposażono układy MAX10. W dostępnych obecnie modelach układów są dostępne 2 lub 4 generatory przebiegów zegarowych, sygnały taktujące implementowany projekt można generować także na zewnątrz układu, rozprowadzając sygnały zegarowe za pomocą globalnych linii zegarowych (rysunek 9), których liczba jest zależna od typu układu.

Rys. 9. Schemat rozprowadzania sygnałów taktujących (zegarowych) w układach MAX10 – oprócz wewnętrznych źródeł z PLL można używać zewnętrznych sygnałów taktujących, które są rozprowadzane w strukturze za pomocą dedykowanych linii globalnych

;

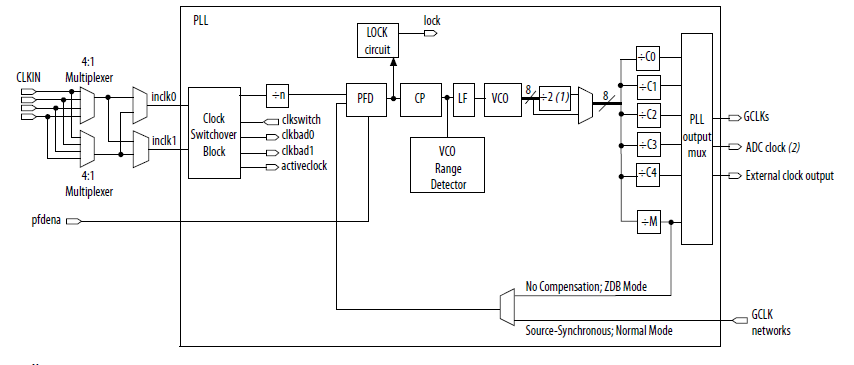

Na rysunku 10 pokazano schemat blokowy pojedynczego syntezera PLL wbudowanego w układy MAX10. Ważną jego cechą jest możliwość dynamicznej zmiany fazy generowanego sygnału, co jest niezwykle przydatną cechą np. w przypadku współpracy FPGA z szybkimi pamięciami zewnętrznymi. Duża liczba preskalerów wyjściowych w blokach PLL umożliwia ich wykorzystanie do jednoczesnego taktowania kilku bloków peryferyjnych, w tym pamięci wewnętrznych i ADC, możliwe jest także wyprowadzanie wygenerowanego sygnału na zewnątrz układu.

Rys. 10. Schemat blokowy jednego z 2 lub 4 syntezerów PLL wbudowanych w układy MAX10

Od strony sprzętowej układy MAX10 zdecydowanie przewyższają klasyczne CPLD (do których zalicza je producent), doskonale odnajdują się one także pośród klasycznych FPGA, nie powielając ich wad, pośród których szczególnie dokuczliwa jest konieczność używania zewnętrznej, nieulotnej pamięci konfiguracji. Producent prezentowanych układów – wraz z ich wprowadzeniem na rynek – udostępnił oprogramowanie projektowe Quartus II obsługujące wszystkie cechy układów MAX10. Co ważne, pakiet Quartus II w wersji WebEdition jest dostępny bezpłatnie, a aktywne w nim drobne ograniczenia funkcjonalne nie wpływają na wygodę implementacji projektu w układach MAX10.

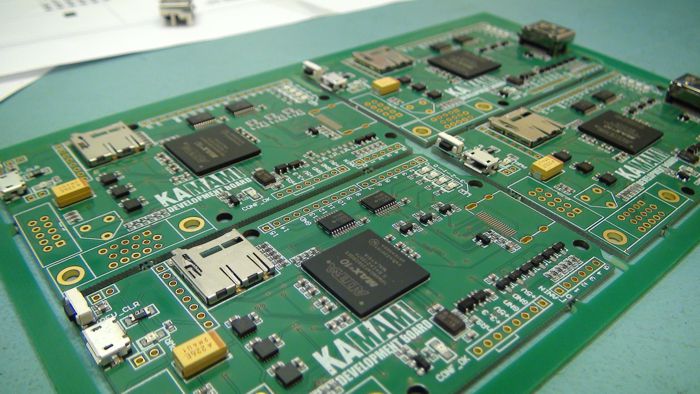

Rys. 11. Zdjęcie prototypowej wersji zestawu z MAX10, który powstał i będzie produkowany w Polsce przez firmę KAMAMI.pl

Dostępne są także pierwsze zestawy ewaluacyjne i startowe z prezentowanymi układami, które przedstawimy w następnym artykule. Ujawniając rąbek tajemnicy zapowiem tylko dojrzewającą na naszym rynku nowość: tani zestaw startowy z układem 10M08, który powstał w firmie KAMAMI.pl i będzie przez nią produkowany. Zdjęcie prototypowej wersji płytki drukowanej zestawu z układem MAX10 (10M08) pokazano na rysunku 11.

Zestaw jest sprzętowo kompatybilny z Arduino UNO, wszystkie linie cyfrowe są przystosowane do współpracy z logiką 3,3 i 5 VDC. Wejścia ADC układu 10M08 użytego w zestawie są chronione przed zbyt wysokim napięciem wejściowym, grożącym uszkodzeniem obwodów wejściowych. Zestaw jest zasilany z USB, wyposażono go m.in. w diody LED, złącze karty SD, interfejsy wideo: VGA oraz HDMI, kompletny zasilacz, bazowy generator sygnału zegarowego oraz potencjometr analogowy, którego suwak dołączono do jednego z wejść ADC. Zasoby układu 10M08 pozwalają na implementację w nim rdzenia (IP Core) 32-bitowego mikroprocesora NIOS II, który jest natywnym opracowaniem firmy Altera (także dostępny bezpłatnie).

Piotr Zbysiński