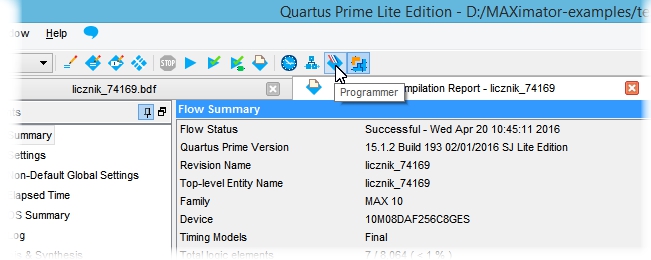

Po wprowadzeniu przypisani ponownie kompilujemy projekt (za pomocą przycisku pokazanego na rysunku 20) i w przypadku poprawnego jej zakończenia możemy zaprogramować układ FPGA z zestawie MAXimator. W tym celu musimy mieć dołączony do komputera programator USB Blaster (wchodzący w skład zestawu MAXimator – przypominam o tym, że zazwyczaj konieczne jest ręczne wskazanie systemowi ścieżki do driverów programatora, co zostało opisane w poprzedniej części artykułu), a sam programator za pomocą 10-żyłowego przewodu złącza JTAG do płytki MAXimator z dołączonym zasilaniem.

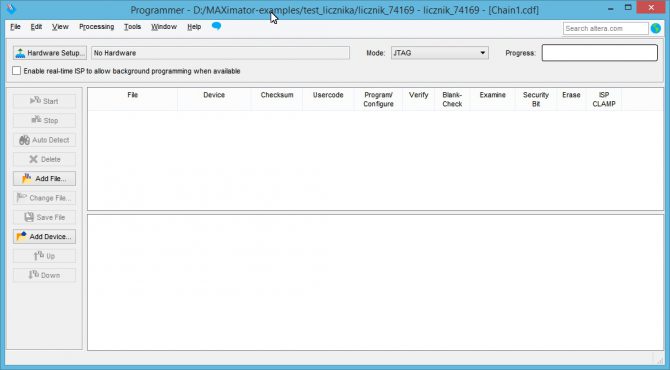

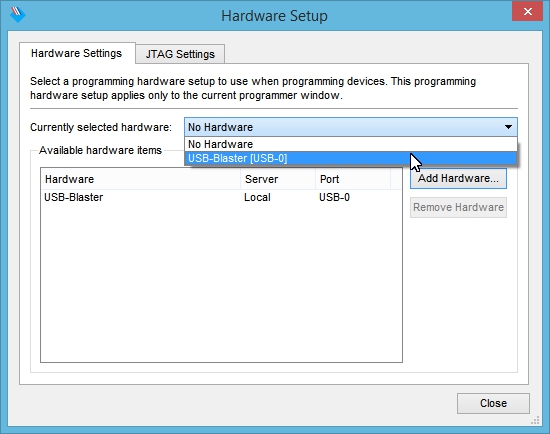

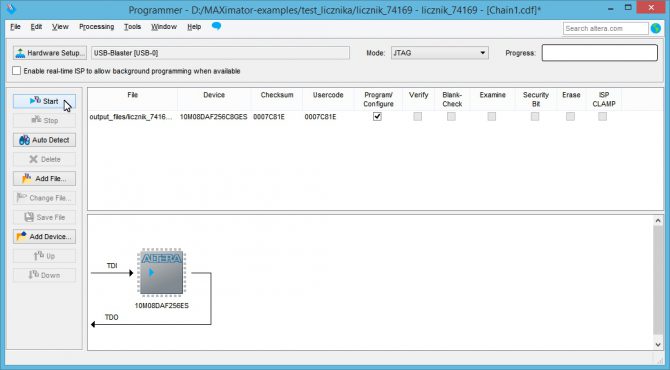

Program obsługujący programator jest uruchamiany za pomocą ikony w menu pokazanej na rysunku 26. Jego okno pokazano na rysunku 27. Jeżeli programator USB Blaster nie zostanie samoczynnie wykryty przez pakiet Quartus, klikamy przycisk Hardware Setup i w wyświetlonym oknie, w zakładce Hardware Settings wybieramy w oknie wyboru Currently selected hardware aktywny programator (rysunek 28). W kolejnym kroku naciskamy w oknie obsługującym programator przycisk Add File… (rysunek 29) i w wyświetlonym oknie wskazujemy plik wynikowy, który użyjemy do programowania FPGA.

Pliki wynikowe są domyślnie ulokowane w podkatalogu o nazwie \output_files ulokowanym w katalogu projektu. Quartus domyślnie generuje dwa rodzaje plików:

- o rozszerzeniu nazwy sof, który jest używany do bezpośredniej konfiguracji pamięci RAM w FPGA. Jego użycie zalecamy podczas eksperymentów z implementacją projektów, częsta modyfikacja zawartości RAM nie wpływa na żywotność pamięci konfiguracji Flash,

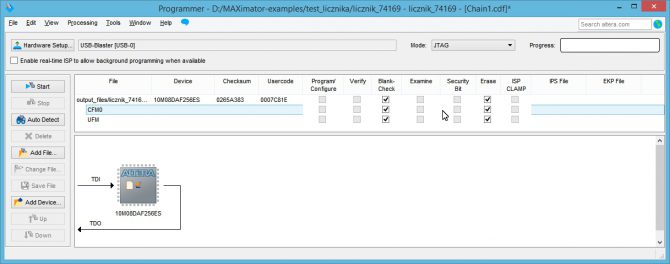

- o rozszerzeniu nazwy pof, który służy do zapisania konfiguracji projektu w nieulotnej pamięci konfiguracji typu Flash. Jego użycie zalecamy do zaprogramowania FPGA ostateczną wersją implementowanego projektu.

Dodanie pliku sof powoduje wyświetlenie symbolu układu w oknie programu obsługującego programator (rysunek 30) z domyślnie aktywną opcją Program/Configure, co umożliwia szybkie zapisanie konfiguracji do pamięci RAM FPGA. W przypadku wybrania pliku pof dostępne opcje są nieco inne (rysunek 31), omówimy je w kolejnych odcinkach kursu.

Przygotowanie i zapisanie do pamięci konfiguracji FPGA projektu przygotowanego według opisu gwarantuje jego poprawne działanie, przy czym należy pamiętać o dostarczeniu do linii D13 (C16) sygnału zegarowego o częstotliwości kilkunastu…kilkuset Hz, który umożliwi obserwację na LED pracy licznika. Zestaw MAXimator jest wyposażony w dwa własne źródła sygnałów zegarowych (generator kwarcowy 10 MHz i wewnętrzny generator zegarowy wbudowany w układ FPGA MAX10), ale częstotliwości generowanych przez nie sygnałów są zbyt duże, żeby można było zaobserwować zmiany stanów LED. Można zastosować preskaler dzielący częstotliwość sygnału generatora kwarcowego do wartości >200 Hz, co umożliwi obserwację pracy licznika bez konieczności stosowania dodatkowego generatora sygnału zegarowego.

Piotr Zbysiński