Pytanie:

Na początku przetestowałem z powodzeniem jeden z waszych ADC i nagle zacząłem dostawać dość dziwne wyniki FFT. Co się dzieje?

Odpowiedź:

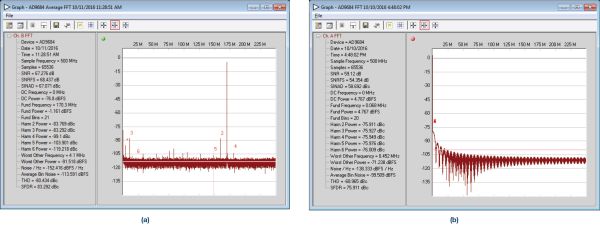

Niedawno otrzymałem takie pytanie i udało mi się dość szybko znaleźć odpowiedź. Problemy projektanta widać na wynikach FFT widocznych na rysunku 1.

Rys. 1. Poprawne i nieprawidłowe wyniki FFT otrzymane dla przetwornika analogowo-cyfrowego AD9684. Częstotliwość próbkowania to 500 milionów próbek na sekundę (Msps), częstotliwość sygnału – 170,3 MHz przy spadku amplitudy -1 dBFS

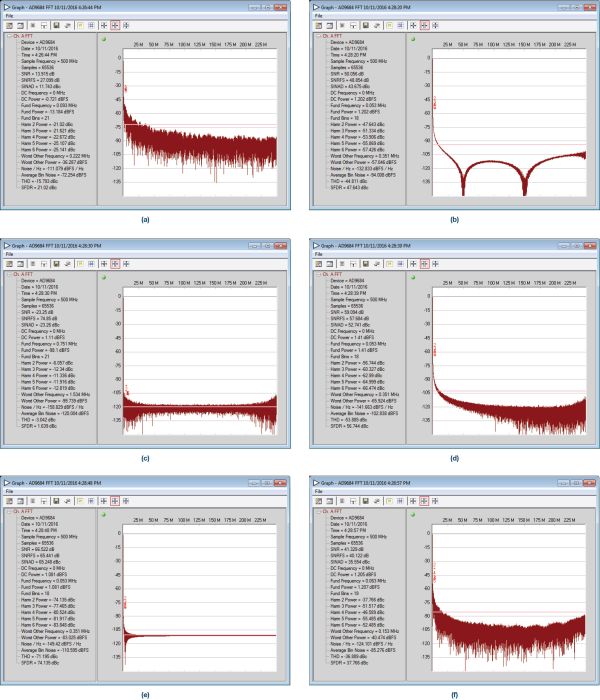

Użytkownik zgłosił nie tylko problem z bezsensownymi wynikami FFT, ale również brak ich spójności. To zachowanie potwierdziło moje początkowe przypuszczenia na temat źródła problemu: źródłowy zegar taktujący był wyłączony lub w ogóle niepodłączony, zatem zegar taktujący wejście przetwornika oscylował samoistnie. To może się zdarzyć również, jeśli połączenie doprowadzające zegar jest uszkodzone lub na ścieżce sygnałowej występuje niestabilny element. Nietrudno było znaleźć rozwiązanie, ponieważ widziałem podobne sytuacje wiele razy. Rysunek 2. przedstawia inne wyniki FFT, które można zaobserwować w takich warunkach:

Rys. 2. Przykładowe wyniki FFT jako skutek oscylacji niestabilnego zegara

Praktycznie we wszystkich zastosowaniach zegar próbkujący powinien mieć stałą częstotliwość. Jednak każda zmiana, czy to pod wpływem szumu fazowego czy termicznego, niestabilność częstotliwości lub niepożądana jej wartość, sprawią, że oczekiwana relacja między zegarem próbkującym a analogowym sygnałem wejściowym zniknie przy obserwacji wykresu w domenie częstotliwości. Nota aplikacyjna AN-756 opisuje przykładowe sytuacje, w których subtelny szum fazowy lub modulacja zegara mogą zniekształcić sygnał wejściowy podczas próbkowania.

Jaka była przyczyna w tym przypadku? Wejścia zegara próbkującego, w bardzo szybkich przetwornikach ADC są zazwyczaj wejściami różnicowymi, które widzą tę samą składową wspólną, a odbiornik ma bardzo duże wzmocnienie. Zatem bez przyłożonego sygnału różnicowego, wejścia są spolaryzowane takim samym napięciem. Każdy szum, który zawiera składową inną niż składowa sumacyjna, może wywołać oscylacje w odbiorniku zegara próbkującego. W takiej sytuacji oscylacje nie będą występować na jednej częstotliwości (gdyby tak się działo, byłaby to przydatna funkcja). Zamiast tego częstotliwość będzie zmieniać się w sposób losowy, a moc wejściowa zostanie rozproszona w całym paśmie Nyquista reprezentowanego w dziedzinie częstotliwości.

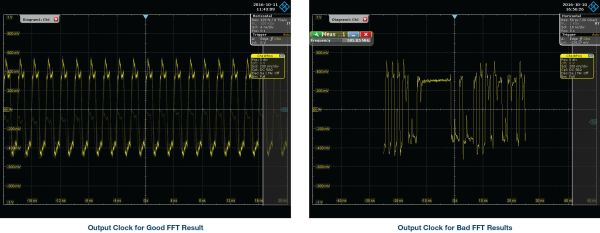

W większości przypadków łatwo można rozpoznać ten błąd i przywrócić żądaną częstotliwość zegara, aby kontynuować testy. Ale jeśli chcesz zweryfikować, że faktycznie na tym właśnie polega problem, należy obserwować DCO – zegar danych wyjściowych ADC (uwaga – nie ma to zastosowania w przypadku wyjść w standardzie JESD204B). Zazwyczaj sygnał ten stanowi opóźnioną kopię zegara próbkującego ADC lub jego podzieloną wartość, jeśli używasz jakichkolwiek cyfrowych funkcji decymacji transmisji danych. Rysunek 3 obrazuje przebiegi wyjściowego zegara danych odpowiadające dobremu i nieprawidłowemu przykładowi FFT z rysunku 1.

Rys. 3. Wyjścia zegara danych ADC odpowiadające dwóm przypadkom FFT z rys. 1

Jak widać, okres zmienia się zgodnie z oczekiwaniami. Rozumiem, dlaczego nie jest łatwo to zauważyć w pierwszej chwili (lub nawet w kilku kolejnych). Na pierwszy rzut oka wygląda na to, że system testowy działa, ale wyniki są nagle zaskakujące. Czy ADC uległ uszkodzeniu? Czy dane są niepoprawnie rejestrowane? Czy oprogramowanie jest uszkodzone? Nie, po prostu brakuje źródła sygnału.