Pamięć Flash jest obecnie najczęściej używanym rodzajem pamięci nieulotnej. Pamięć Flash typu NAND została zoptymalizowana pod kątem przechowywania plików, mając na celu zastąpienie tradycyjnych dysków twardych. Niniejszy artykuł omawia zasadę działania pamięci Flash oraz wpływ kontrolera na optymalizację wydajności i czasu życia takiej pamięci.

Czym jest pamięć Flash?

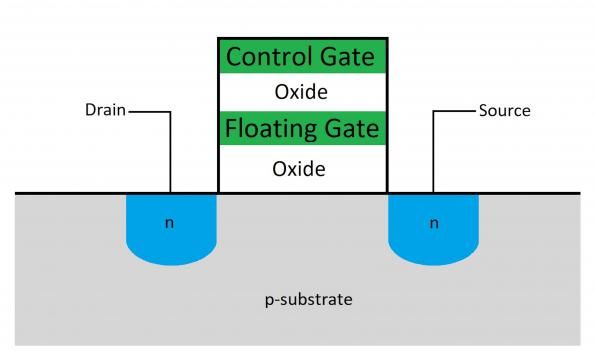

Podstawowym elementem pamiętającym wykorzystywanym w pamięci Flash jest zmodyfikowany tranzystor. W standardowym tranzystorze przepływ prądu w kanale między dwoma kontaktami jest włączony napięciem przyłożonym do trzeciego kontaktu – metalowej bramki znajdującej się nad kanałem, która jest oddzielona od niego izolującą warstwą tlenku. W komórce pamięci Flash obecna jest ponadto dodatkowo bramka izolowana elektrycznie. Tzw. „pływająca”. Znajduje się ona między bramką sterującą i kanałem, co widać na rys. 1.

Programowanie komórki Flash

Komórka pamięci Flash jest programowana za pomocą wysokiego napięcia przyłożonego do bramki sterującej. To sprawia, że elektrony przepływają przez warstwę tlenku pływającej bramki – jest to tzw. proces tunelowania. Obecność elektronów w pływającej bramce zmienia napięcie sterujące potrzebne do włączenia tranzystora. Wyzerowana komórka (bez ładunku pływającej bramce) włączy się i będzie przedstawiać wartość logiczną 1, natomiast zaprogramowania komórka nie włączy się i będzie przedstawiać logiczne 0.

Ponieważ pływająca bramka jest otoczona warstwami izolującymi, utrzyma ładunek elektryczny również po odłączeniu zasilania. Dzięki temu pamięć jest nieulotna.

Zerowanie komórki polega na odwróceniu tego procesu – przyłożenie wysokiego napięcia ujemnego do bramki sterującej, co zmusza elektrony do tunelowania poza pływającą bramkę.

Struktura matrycy Flash

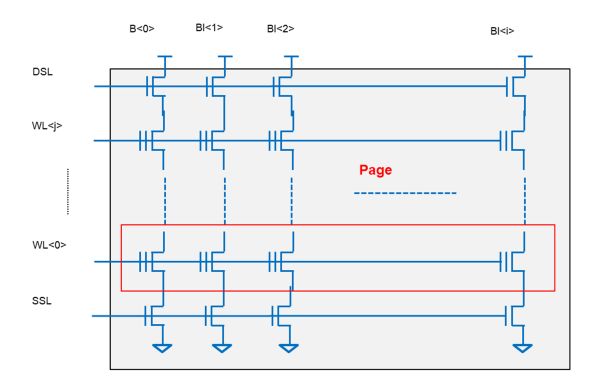

Komórki pamięci Flash są zorganizowane w hierarchii pokazanej na rys. 2, która zapewnia efektywny dostęp do wielu bitów. Pewna liczba komórek, typowo od 32 do 128, jest połączona w łańcuch. Łańcuchy są natomiast zorganizowane w bloki. Każdy łańcuch w bloku jest połączony z osobną linią bitów, a bramka każdej komórki w łańcuchu jest połączona z linią słowa. Linia słowa jest połączona z każdą komórką umieszczoną na tej samej pozycji w różnych łańcuchach i określa „stronę” w obrębie bloku. Strona jest minimalnym rozmiarem dostępnym dla operacji zapisu i odczytu. Blok jest najmniejszym rozmiarem dla operacji zerowania.

Wiele bloków można połączyć przy użyciu buforów danych i układów sterujących, tworząc warstwę (plane). Kompletne kości pamięci Flash zawierają jedną lub wiele warstw. W przypadku kości wielowarstwowych zazwyczaj można wykonywać operacje zapisu i odczytu na wielu warstwach jednocześnie, zwiększając sumaryczną wydajność.

Dane są odczytywane poprzez przyłożenie niskiego napięcia na linii słowa strony, która ma zostać odczytana. Wówczas dane te pojawią się na liniach bitów.

Aby zaprogramować komórki w bloku, dane są wprowadzane na linie bitów, a następnie wysokie napięcie zostaje przyłożone do linii słowa odpowiedniej strony. Ponieważ programowanie może jedynie zmienić stan komórki z 1 na 0, przy próbie zaprogramowania 1 komórki pozostaną w dotychczasowym stanie, jakikolwiek on by nie był. Z tego powodu wszystkie komórki muszą być wyzerowane przed zapisem. Takie postępowanie zapewnia, że wszystkie komórki, które nie zostaną zaprogramowane, już zawierają 1.

Jeśli komórki zawierają już dane, wówczas dane te trzeba odczytać z bloku, połączyć z nowymi danymi i następnie zaprogramować w nowym, wyzerowanym bloku. Blok, z którego dane zostały skopiowane, jest wówczas gotowy do powtórnego użycia po wyzerowaniu.

Komórki wielowartościowe

Powyższy opis dotyczy komórek przechowujących pojedyncze wartości binarne, 0 lub 1. Możliwe jest jednak wprowadzenie różnej ilości ładunku do pływającej bramki, przez co pojedyncza komórka reprezentuje wiele wartości. Komórka dwuwartościowa (multi-level cell, MLC) wykorzystuje cztery różne wartości, aby przechowywać dwa bity. Z kolei komórka trójwartościowa (TLC) wykorzystuje 8 różnych poziomów do przechowywania 3 bitów naraz. To pozwala zmieścić więcej danych w macierzy, obniżając koszt pojedynczego bitu. Jednak powoduje to spadek wydajności, ponieważ napięcia podczas programowania i odczytu muszą być dokładniej kontrolowane. Z tego samego poziomu pamięć Flash MLC jest bardziej podatna na błędy.

Pamięć Flash 3D

Pamięć 3D jest nowym rozwiązaniem, które pozwala w dalszym stopniu zwiększyć gęstość opakowania i obniżyć koszt w stosunku do pojemności pamięci Flash. Polega ono na wykorzystaniu trójwymiarowej struktury układu zamiast struktury powierzchniowej. Rzędy komórek pamięci są rozmieszczone pionowo w krzemie, co pozwala zmieścić wielokrotnie więcej bitów na tej samej powierzchni. Tworzenie pamięci Flash 3D wiąże się z kilkoma trudnościami technicznymi, jednak rozwiązania ta są już wykorzystywane do tworzenia układów o bardzo wysokiej pojemności.

Kontroler Flash

Kontroler pamięci Flash stanowi interfejs między systemem hosta a układami pamięci. Pełni liczne funkcje, w tym mapowanie adresu dostarczonego przez hosta na konkretne komórki w pamięci Flash. Ponadto musi przeciwdziałać naturalnym wadom tej technologii.

Detekcja i korekcja błędów

Z powodu możliwości wystąpienia błędów podczas odczytu danych z matrycy Flash, kontroler podczas zapisu dodaje kilka bitów, które stanowią sumę kontrolną (ECC). Suma kontrolna jest odczytywana razem z danymi. Zastosowanie kodów korekcyjnych pozwala na korekcję pojedynczych nieprawidłowych bitów oraz detekcję błędu występującego na wielu bitach.

Naturalne wady technologii Flash

Jedną z wad pamięci Flash jest ograniczona liczba cykli zapisu i zerowania. Stosowanie wysokich napięć prowadzi do stopniowego uszkodzenia komórek, które z czasem są coraz trudniejsze do zaprogramowania i wyzerowania. Uszkodzenie warstw izolujących wokół pływającej bramki skraca również czas, przez jaki dane mogą zostać utrzymane. To ogranicza żywotność pamięci Flash do około 100.000 cykli, lub mniej w przypadku komórek MLC.

Czas życia pamięci Flash można zmaksymalizować zapewniając, że liczba cykli zapisu i zerowania dla wszystkich bloków jest taka sama – dzięki temu zużycie pamięci jest rozłożone równomiernie. Aby to zrealizować, kontroler pamięci musi przechowywać informacje o zużyciu bloków i wybierać najlepszy blok na zapisanie nowych danych.

Napięcia potrzebne do zapisu i odczytu komórek mogą powodować niewielkie zmiany ładunku z sąsiednich komórkach, w końcu doprowadzając do wystąpienia błędów przy odczycie. Jest to efekt chwilowy, który zostaje naprawiony przy kolejnym zapisie danych do komórki. Kontroler pamięci może odświeżyć zawartość komórki, aby zapobiec utracie danych. Może to robić regularnie lub w przypadku wykrycia zbyt wielu błędów.

Podobnie jak w każdym układzie pamięci, może pojawić się pewna liczba bloków, które nie będą działały poprawnie z powodu defektów czy rozrzutu procesu produkcji. Pewne bloki ulegną też awarii z biegiem czasu – można je wykryć, jeśli kody korekcyjne nie wykażą poprawy po zapisaniu nowych danych. Kontroler musi zapamiętywać te bloki i zmienić sposób zapisu danych w matrycy, aby uniknąć użycia wadliwych bloków.

Kontroler zarządza przechowywaniem danych i maskuje nieuniknione wady technologii NAND Flash z punktu widzenia hosta. Tym samym maksymalizuje wydajność i czas życia pamięci Flash. Jest to dobre rozwiązanie do masowych systemów magazynowania danych, które wymagają wysokiej niezawodności.