Firmy Intel Corporation i Altera Corporation poinformowały o zawarciu porozumienia, na mocy którego Intel kupi Alterę. Łączny koszt transakcji wyniesie 16.7 mld USD.

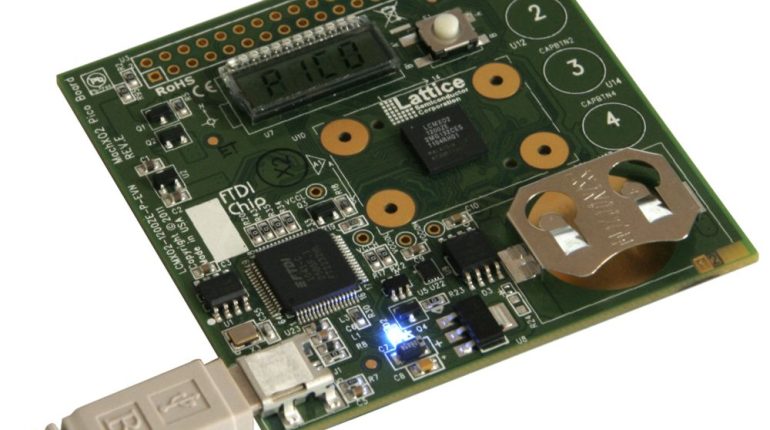

Lattice MachXO2 Pico Development Kit – platforma dla projektów SoC

Jedną z najbardziej interesujących nas nowości w ofercie firmy Lattice są układy MachXO2 programowalne klasyfikowane jako CPLD, ale o cechach i wewnętrznym wyposażeniu przewyższającym niejedną rodzinę FPGA. Drugim atutem rodziny MachXO2 są różnorodne, tanie, doskonale wyposażone zestawy ewaluacyjne, z których jeden – Pico Development Kit – przedstawiamy w artykule.

Nowe projekty referencyjne dla układów MachXO2 firmy Lattice

Nowe projekty referencyjne obejmują interfejsy I2C, SPI oraz pamięć Flash Hard IP.

Nowe układy w rodzinie MachXO2

Producent układów PLD – firma Lattice – wprowadziła do sprzedaży w rodzinie MachXO2 nowe typy układów, oferowane w miniaturowych obudowach QFN32.

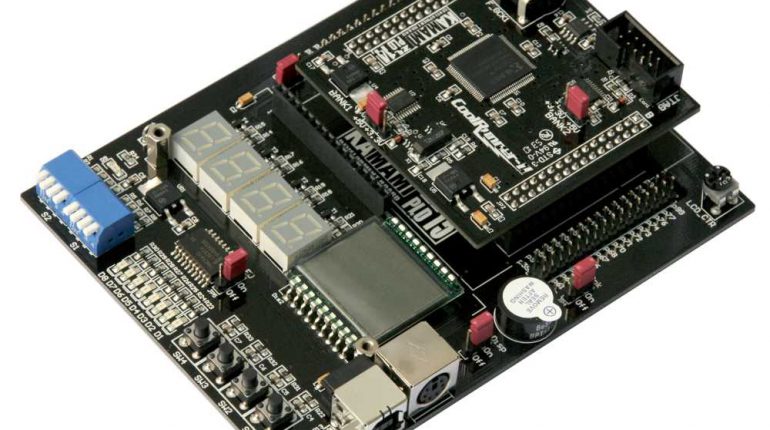

Pierwsze kroki z CPLD (Xilinx CoolRunner II): obsługa przycisków

Jednym z istotnych elementów projektów zaprezentowanych w książce „Układy programowalne dla początkujących” jest obsługa przycisków. Pozornie prosta operacja w rzeczywistości sprawia wiele problemów, które wynikają ze zjawiska nazywanego „dzwonieniem styków”.

Pierwsze kroki z CPLD (Xilinx CoolRunner II): 4-cyfrowy licznik BCD

Do realizacji projektu opisanego w książce „Układy programowalne dla początkujących” może być wykorzystany zarówno zestaw uruchomieniowy produkowany przez KAMAMI (ZL14PLD + ZL15PLD) jak i SK-CRII-L-G firmy DIGILENT.

Prosty projekt w VHDL dla CPLD firmy Xilinx z rodziny CoolRunner

Realizacja projektu opisanego w książce „Układy programowalne dla początkujących” w rozdziale zatytułowanym „Pierwszy projekt” może być wykonana zarówno przy użyciu zestawów uruchomieniowych produkowanych przez firmy KAMAMI (ZL14PLD + ZL15PLD) jak i DIGILENT (SK-CRII-L-G), gdyż wymagania sprzętowe tego projektu są spełnione w obu przypadkach. Zadaniem prezentowanego rozwiązania jest odczyt stanu przycisków i prezentacja uzyskanej informacji na wyświetlaczu LED.

Quartus II w wersji 11.0 z narzędziem do integracji systemów Qsys

Altera poinformowała o wprowadzeniu rynek swojego oprogramowania Quartus II w wersji 11.0, będącego w swojej branży oprogramowaniem numer jeden pod względem wydajności i produktywności dla układów CPLD, FPGA oraz HardCopy ASIC.

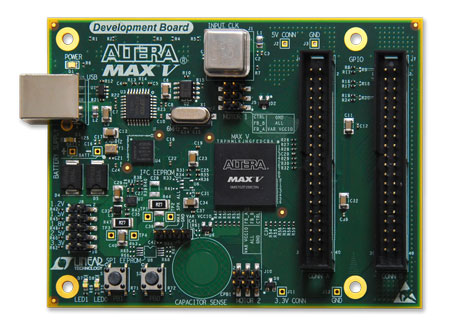

Nowa rodzina układów CPLD w ofercie Altery: MAX V

Nowością w ofercie firmy Altera są układy CPLD tworzące rodzinę o nazwie MAX V. Ich wyposażenie i możliwości odbiegają od standardów znanych z klasycznych rodzin CPLD, budową i możliwościami są natomiast zbliżone do znanych dość dobrze na rynku układów z rodziny MAX II.

MAX V: nowe CPLD w ofercie Altery

Producenci układów PLD nie zasypują gruszek w popiele: w pierwszych dniach grudnia Altera ogłosiła wprowadzenie na rynek nowej rodziny układów CPLD z rodziny MAX V, które uzupełnią portfolio nowoczesnych układów tego typu, reprezentowanych dotychczas przez rodzinę MAX II. W skład rodziny MAX V wchodzą układy o szerokim spektrum zasobów logicznych (liczba „makrokomórek” od 32 w układzie 5M40 do 1700 w układzie 5M2210), konfigurowalnej pamięci EEPROM o pojemności 8 kb, a także wewnętrznym generatorze taktującym z cyfrową pętlą PLL. Generator sygnału zegarowego charakteryzuje się niewielką dokładnością częstotliwości generowanego przebiegu (która mieści się w przedziale 3,9 do 5,3 MHz), ale jest wystarczająca do wielu aplikacji wymagających sygnału synchronizującego. Najmniejszy z układów udostępnia konstruktorom 54 linie I/O, ich maksymalna liczba wynosi 271, w tym 4 globalne linie zegarowo-zerujące.