Firma Xilinx zaprezentowała przełomowy produkt należący do nowej kategorii zwanej ACAP (adaptive compute acceleration platform). Jego funkcjonalność znacznie przewyższa możliwości tradycyjnych rozwiązań FPGA. ACAP stanowi heterogeniczną, wielordzeniową platformę obliczeniową o wysokim stopniu integracji, która może się zmieniać na poziomie sprzętowym w celu adaptacji do zróżnicowanych zadań i zastosowań. Adaptację ACAP można przeprowadzić w sposób dynamiczny podczas pracy. Platforma oferuje taką wydajność w stosunku do poboru mocy, która przewyższa możliwości procesorów CPU lub GPU.

Platforma ACAP nadaje się do przyspieszenia wielu różnych systemów w nadchodzącej erze Big Data oraz sztucznej inteligencji. Do przykładowych zastosowań należą: transkodowanie wideo, przetwarzanie baz danych, kompresja danych, wyszukiwanie, wnioskowanie AI, genomika, wizja maszynowa oraz urządzenia sieciowe. Projektanci sprzętu oraz programiści będą w stanie stworzyć produkty oparte na ACAP dla urządzeń komputerowych, urządzeń brzegowych i chmury. Pierwsza seria produktów ACAP o nazwie „Everest” zostanie wykonana w procesie technologicznym TSMC 7 nm i będzie wprowadzona w tym roku.

„Jest to znaczący przełom dla rynku i nasze największe osiągnięcie inżynieryjne od czasów wynalezienia FPGA.” – oznajmił Victor Peng, prezes i dyrektor generalny Xilinx. „Ta rewolucyjna, nowa architektura jest częścią szerszej strategii, która wykracza poza same układy FPGA i ofertę dla projektantów sprzętu. Zastosowanie produktów ACAP przez centra danych, jak i inne rynki naszej firmy, pozwoli przyspieszyć powszechne wykorzystanie adaptacyjnych obliczeń. Dzięki temu wizja świata inteligentnych, połączonych i adaptacyjnych urządzeń stanie się bliższa realizacji.”

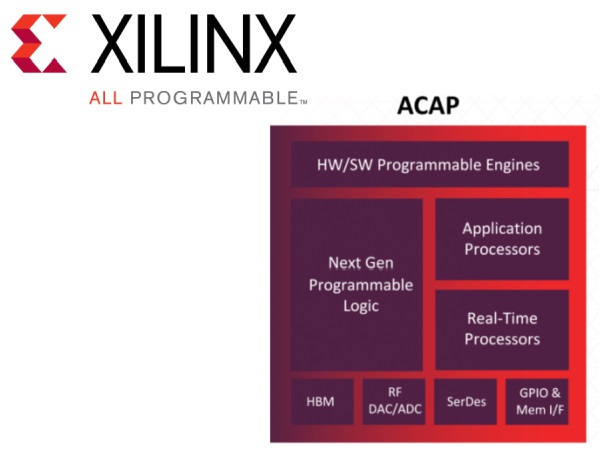

Układy ACAP opierają się na nowej generacji macierzy FPGA z rozproszoną pamięcią i sprzętowo programowanych blokach DSP. Zawierają one również wielordzeniowe układy SoC (System-on-Chip) i jeden lub więcej silników obliczeniowych (compute engine) – programowanych w odpowiednim języku, lecz jednocześnie pozwalających na adaptację sprzętową. Wszystko to jest połączone siecią, tzw. Network on Chip (NoC). ACAP dysponuje również programowalnymi wejściami I/O o wysokim stopniu integracji – od sprzętowo programowalnych kontrolerów pamięci, zaawansowanych układów SerDes i najnowszych przetworników RF-ADC/DAC, do zintegrowanej pamięci wysokiej przepustowości (HBM) – w zależności od wersji układu.

Programiści będą mogli wykorzystać systemy oparte na układach ACAP przy użyciu takich języków, jak C/C++, OpenCL i Python. Układy ACAP można również programować sprzętowo na poziomie RTL przy użyciu narzędzi przeznaczonych dla układów FPGA.

Platforma ACAP była projektowana przez cztery lata, a badania pochłonęły miliard dolarów. Obecnie ponad 1500 inżynierów Xilinx projektuje sprzęt i oprogramowanie ACAP oraz Everest. Narzędzia programistyczne zostały już dostarczone kluczowym klientom. Produkcja serii Everest ruszy w tym roku, a pierwsze dostawy do klientów nastąpią w roku 2019.

Xilinx oczekuje, że Everest osiągnie dwudziestokrotny wzrost wydajności wielowarstwowych sieci neuronowych – w porównaniu do obecnego najnowszego układu FPGA Virtex VU9P w rozmiarze technologicznym 16 nm. Zdalne nadajniki radiowe 5G oparte na układach Everest uzyskają czterokrotnie wyższą przepustowość, niż najnowsze systemy radiowe oparte na układach 16 nm. Zwiększoną wydajność i lepszą sprawność energetyczną można wykorzystać w wielu obszarach zastosowań: w nauce i przemyśle, motoryzacji i medycynie, a także w obronności i lotnictwie, pomiarach i emulacji, systemach audio/wideo oraz transmisji, jak też w zastosowaniach użytkowych.

Architektura ACAP została po raz pierwszy zapowiedziana w ramach najnowszej strategii firmy. Dodatkowe informacje są dostępne na stronie Xilinx.