Pierwsze kroki z zestawem FPGA Lattice MachXO2 Pico Development Kit [1]

Uwaga! Druga część artykułu jest dostępna pod adresem.

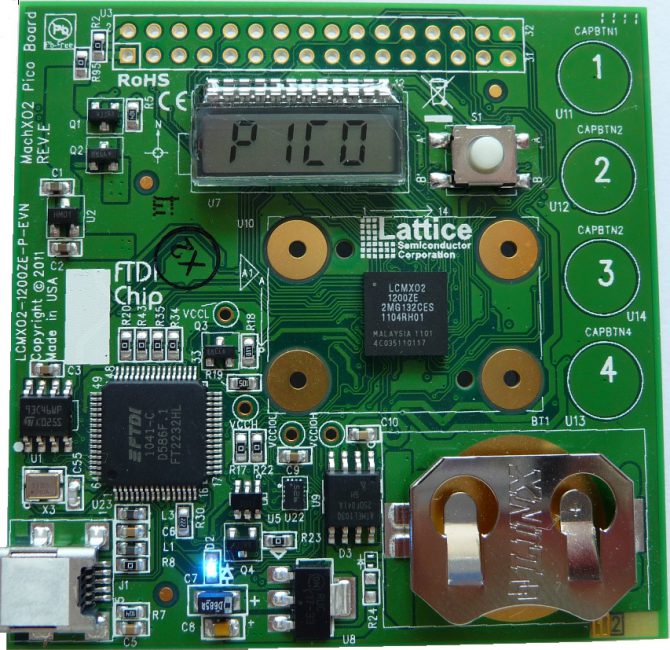

Firma Lattice jest producentem interesującej rodziny układów FPGA o nazwie MachXO2. Są one produkowane w procesie 65 nm, bazują na technologii Flash, mają duże zasoby logiczne – w tym pamięć RAM – pojemności wbudowanej pamięci RAM, do tego wszystkiego są energooszczędne. To wszystko oznacza, że układy MachXO2, o zasobach logicznych sięgających 7000 komórek LUT, mogą swobodnie konkurować z „mniejszymi” układami FPGA rodzin Actel IGLOO, Altera Cyclone czy Xilinx Spartan. Z myślą o konstruktorach zainteresowanych tymi układami producent udostępnił tani zestaw ewaluacyjny MachXO2 Pico DK, umożliwiający praktyczne poznanie najważniejszych właściwości układów rodziny. Celem naszego kursu jest zilustrowanie sposobu projektowania stosunkowo nieskomplikowanych systemów cyfrowych, opartych na nowoczesnych układach programowalnych, z wykorzystaniem zestawu MachXO2 Pico.

Kurs rozpoczniemy od zaprezentowania właściwości układów Lattice MachXO2, przestawimy architekturę zestawu MachXO2 Pico Developmnet Kit, opiszemy nowe środowisko projektowe Lattice Diamond Design Software, a następnie przedstawimy szereg przykładowych projektów zrealizowanych z wykorzystaniem wspomnianego zestawu ewaluacyjnego.

Architektura układów PLD Lattice MachXO2

Chociaż producent na kartach dokumentacji technicznej dla tej rodziny konsekwentnie stosuje określenie PLD (Programmable Logic Device), to jednak układy te posiadają wiele cech charakterystycznych dla typowych struktur FPGA (np.: komórki logiczne oparte na tablicach LUT, wbudowane bloki pamięci RAM, układy pętli synchronizacji fazowej PLL dla sygnałów zegarowych). W połączeniu z takimi właściwościami jak bardzo niski pobór mocy, wbudowana nieulotna pamięć konfiguracji Flash z wydzieloną przestrzenią dla danych użytkownika, wewnętrzny generator CMOS, wbudowane sprzętowe bloki kontrolera magistral SPI i I2C a także licznika/czasomierza, wsparcie dla wstępnego przetwarzania sygnałów synchronicznych w komórkach wejścia/wyjścia (DDR, DDR2, LPDDR) oraz szeroki zakres standardów obsługiwanych przez bufory wejścia/wyjścia (LVCMOS, LVTTL, PCI, LVDS, SSTL, HSTL) – rodzina układów MachXO2 jest bardzo atrakcyjna z inżynierskiego punktu widzenia.

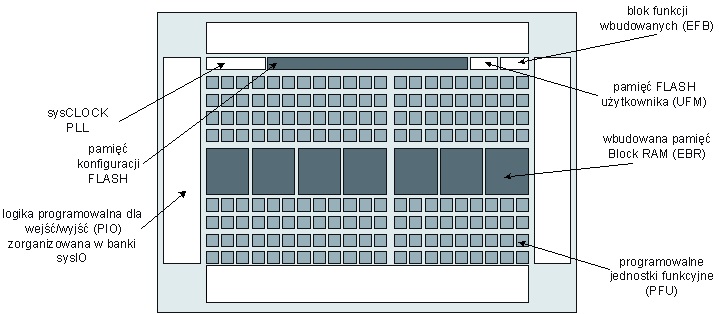

Na rysunku 1 przedstawiono ogólny schemat architektury wybranego układu z rodziny MachXO2. Programowalne jednostki funkcyjne PFU (Programmable Function Unit) oraz bloki pamięci EBR (Embedded Block RAM) są rozmieszczone w wierszach i kolumnach dwuwymiarowej siatki. Siatka ta jest z zewnątrz otoczona przez programowalną logikę wejścia/wyjścia PIO (Programmable Input/Output). Jednostki PFU oraz pamięci EBR są ze sobą połączone za pośrednictwem programowanej matrycy połączeń (routing channel resources). Architektura innych układów z tej rodziny jest identyczna z wyjątkiem liczby dostępnych jednostek PFU, bloków pamięci EBR oraz rozmiaru pamięci Flash użytkownika UFM (User Flash Memory). Jedynie „najmniejszy” z oferowanych układów rodziny MachXO2 nie posiada wbudowanej pamięci RAM, pamięci UFM oraz bloku PLL.

Programowalne jednostki funkcyjne PFU

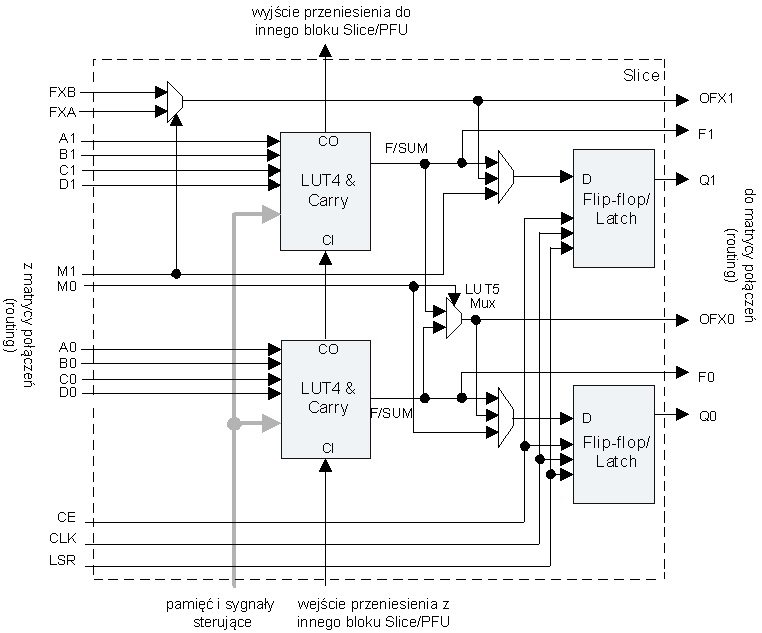

Zasadniczym elementem architektury układów rodziny MachXO2 są programowalne jednostki funkcyjne PFU, realizujące operacje logiczne i arytmetyczne, a także mogące pełnić rolę rozproszonych pamięci RAM i ROM (distributed RAM, ROM). Każda jednostka PFU składa się z 4 połączonych ze sobą bloków slice. Strukturę pojedynczego bloku slice przedstawia rysunek 2. Każdy blok slice zawiera, z kolei, dwie 4-wejściowe tablice LUT (generatory funkcji, Look-Up Table) oraz dwa przerzutniki.

Warto tutaj wspomnieć, że ogólna architektura układów PLD rodziny MachXO2 jest bardzo zbliżona do rodziny XP2 – typowych, „dużych” układów FPGA również oferowanych przez Lattice. Struktura jednostek PFU oraz bloków slice jest dla tych dwóch rodzin dokładnie identyczna. Ponadto budowa samego bloku slice wykazuje również pewne podobieństwa do analogicznych bloków silce układów FPGA Xilinx rodziny Spartan-2 i Spartan-3 (w przypadku układów Spartan-3 sposób połączenia dwóch tablic LUT z dwoma przerzutnikami jest nieco bardziej rozbudowany niż dla rodziny MachXO2 czy XP2).

Programowalne komórki wejścia-wyjścia

Układy z rodziny MachXO2 zapewniają wsparcie dla implementacji szybkich interfejsów przesyłania danych dla aplikacji wykorzystujących techniki SDR (Single Data Rate) oraz DDR (Double Data Rate – transmisja danych odbywa się z wykorzystaniem obydwu zboczy sygnału zegarowego). Dzięki programowalnym blokom PIO możliwa jest np. implementacja interfejsów do pamięci DDR, DDR2, LPDDR SDRAM, bez wykorzystywania logiki dostępnej w jednostkach PFU.

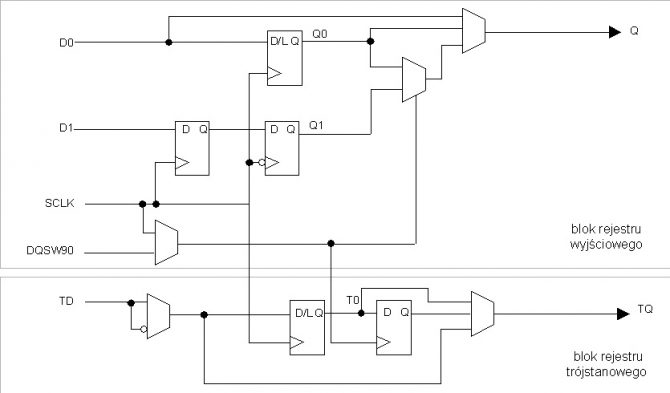

Logika programowalna związana z wejściami i wyjściami określana jest jako komórka PIO (Programmable Input/Output). Pojedyncza komórka PIO jest połączona poprzez bufory wejścia/wyjścia z zewnętrznymi końcówkami układu programowalnego. Układy MachXO2 zawierają grupę 4 komórek PIO, która nazywana jest programowalną komórką wejścia/wyjścia PIC (Programmable Input/Output Cell). Na rysunku 3 pokazano ogólny schemat komórki PIC.

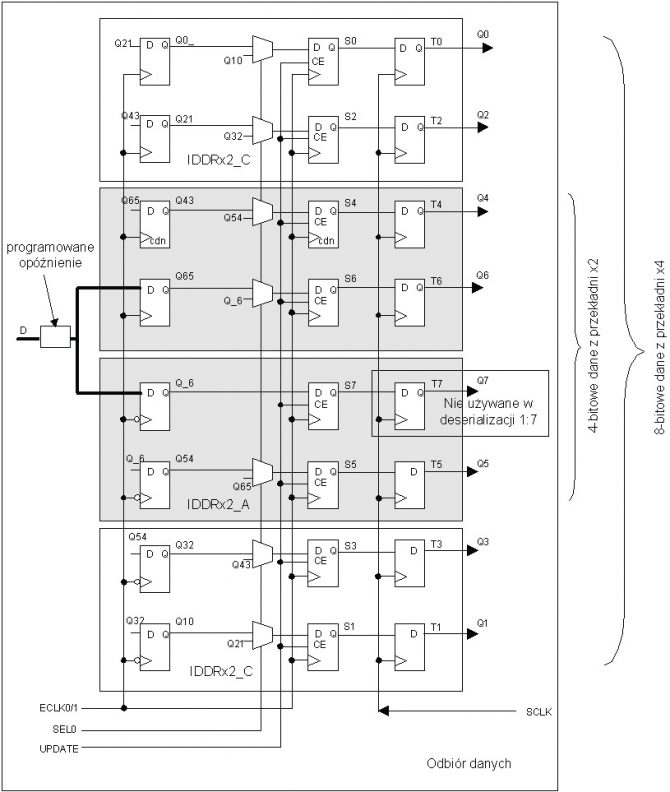

Implementacja szybkich interfejsów DDR realizowana jest poprzez wbudowane tzw. przekładnie (gearing logic), znajdujące się w komórkach PIO. Zastosowanie przekładni znajdujących się w blokach wejścia-wyjścia zmniejsza wymagania odnośnie wydajności układu PLD (FPGA), przy pomocy którego realizowany jest szybki interfejs danych.

W układach MachXO2 dostępne są cztery przełożenia (gearing ratio), zależnie od lokalizacji banku wejścia/wyjścia oraz ilości dostępnych zasobów logicznych układu: x1, x2, x4 oraz 7:1 (wykorzystywany w aplikacjach wyświetlaczy video lub jako serializer – deserializer danych). Zapewnienie istnienia takich przełożeń realizowane jest za pomocą trzech typów komórek PIO: podstawowej, komórki pamięci PIO oraz komórki video PIO. Ogólnie, pierwsze dwa typy komórek zawierają trzy bloki: blok rejestru wejściowego, blok rejestru wyjściowego i blok rejestru trójstanowego (rysunek 3). Dla przykładu, na rysunku 4 i rysunku 5 pokazano strukturę komórki wyjściowej pamięci PIO oraz strukturę przekładni wejściowej.

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485