Nowa rodzina układów CPLD w ofercie Altery: MAX V

![]()

Prezentowany w portalu artykuł jest zaktualizowaną i rozszerzoną przez autora wersją publikacji z miesięcznika Elektronika Praktyczna 12/2010.

Nowością w ofercie firmy Altera są układy CPLD tworzące rodzinę o nazwie MAX V. Ich wyposażenie i możliwości odbiegają od standardów znanych z klasycznych rodzin CPLD, budową i możliwościami są natomiast zbliżone do znanych dość dobrze na rynku układów z rodziny MAX II.

Konstruktorzy korzystający z układów MAX V mają do dyspozycji ich duże zasoby logiczne, w tym 8 kb wewnętrznej pamięci Flash. Podstawowe komórki logiczne (Logic Element) układów MAX V są zbudowane w sposób podobny do stosowanych w alterowskich FPGA, dzięki temu charakteryzują się podobną elastycznością konfiguracyjną. Wewnątrz układów MAX V zintegrowano także generator taktujący oraz implementowaną (ale w standardowych zasobach logicznych!) cyfrową pętlę PLL umożliwiającą generowanie wewnętrznych sygnałów zegarowych. Zestawienie podstawowych cech układów z rodziny MAX V przedstawiono w tab. 1.

Tab. 1. Zestawienie podstawowych cech układów MAX V

| Cecha | 5M40Z | 5M80Z | 5M160Z | 5M240Z | 5M570Z | 5M1270Z | 5M2210Z |

| Liczba LE | 40 | 80 | 160 | 240 | 570 | 1,270 | 2,210 |

| Pojemność pamięci Flash UFM [b] | 8192 | 8192 | 8192 | 8192 | 8192 | 8192 | 8192 |

| Liczba sygnałów globalnych (o programowanych funkcjach) | 4 | 4 | 4 | 4 | 4 | 4 | 4 |

| Wewnętrzny generator zegarowy 4 MHz | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| Maksymalna liczba I/O | 54 | 79 | 79 | 114 | 159 | 271 | 271 |

Budowa układów MAX V

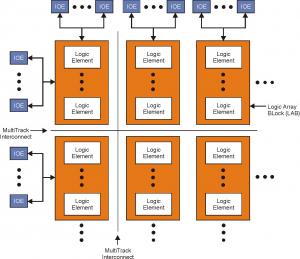

Schemat ilustrujący budowę układów MAX V pokazano na rys. 1. Każdy LAB (Logic Array Block) składa się z 10 podstawowych komórek logicznych LE (Logic Element) oraz zasobów komunikacyjnych o zasięgu lokalnym i globalnym, zapewniających komunikację pomiędzy implementowanymi w układzie fragmentami projektu.

Rys. 1. Schemat blokowy ilustrujący budowę układów MAX V

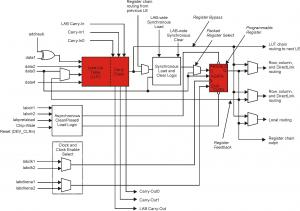

Rys. 2. Budowa komórki LE (kolorem zaznaczono tablicę LUT i konfigurowalny przerzutnik)

W skład LE wchodzi 4-wejściowa tablica LUT (Look-up Table – rys. 2) zintegrowana z generatorami przeniesień (co przyspiesza operacje arytmetyczne i logiczne wykonywane na wielobitowych danych) oraz konfigurowalny przerzutnik, który może pracować jako rejestr D oraz przerzutnik T, JK lub RS (w wersji synchronicznej i asynchronicznej). Układy MAX V wyposażono w 4 globalne linie zegarowe, którymi można przesyłać sygnały pobrane z wejść zewnętrznych lub wytwarzane wewnątrz układu (rys. 3).

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii  Mieszacze aktywne – ćwiczenie z serii ADALM

Mieszacze aktywne – ćwiczenie z serii ADALM