Nowa rodzina układów CPLD w ofercie Altery: MAX V

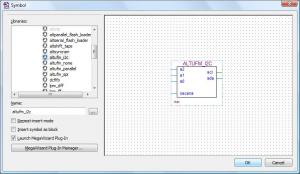

Rys. 7. Wygląd symbolu graficznego megafunkcji ALTUFM_I2C

– ALTUFM_I2C (rys. 7) – pozwalająca operować na zawartości Flash poprzez interfejs I2C,

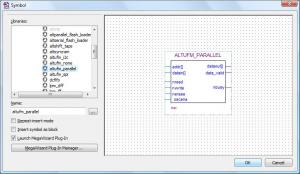

Rys. 8. Wygląd symbolu graficznego megafunkcji ALTUFM_PARALLEL

– ALTUFM_PARALLEL (rys. 8) – pozwalająca operować na zawartości Flash poprzez 16-bitowy interfejs równoległy.

Podczas korzystania z pamięci Flash należy wziąć pod uwagę dwa istotne fakty:

- jej zawartość nie jest chroniona przed dostępem z zewnątrz (także poprzez interfejs JTAG) – wbudowane w układy MAX V zabezpieczenie przed nieuprawnionym kopiowaniem chroni wyłącznie pamięć konfiguracji układu!

- deklarowana przez producenta dopuszczalna liczba cykli kasowania/programowania pamięci Flash wynosi 1000 razy, co nie zawsze może się okazać liczbą wystarczającą w projektach intensywnie operujących na zawartości pamięci nieulotnej.

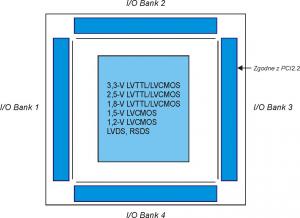

Rys. 9. W zależności od zasobów logicznych linie I/O są podzielone na 2 lub 4 banki (w tym przypadku jeden z nich jest zgodny ze standardem PCI2.2)

Jak widać na rys. 1 konfigurowalny „rdzeń” układów MAX V jest otoczony komórkami I/O (podzielonymi na 2 lub 4 banki – rys. 9), które także można konfigurować. Ich budowa jest bardzo prosta (rys. 10), ale zapewnia pełną funkcjonalność oraz elementy pozwalające pracować w otoczeniu silnie zakłóconym (m.in. wejściowy, opcjonalny, przerzutnik Schmitta oraz dołączane na żądanie rezystory pull-up lub przerzutniki bus-hold).

|

Zestaw uruchomieniowy dla układów MAX V

Pierwsze próby aplikacyjne z układami MAX V ułatwi opracowany przez producenta zestaw uruchomieniowy, który ma być dostępny w pierwszej połowie 2011 roku. |

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii  Mieszacze aktywne – ćwiczenie z serii ADALM

Mieszacze aktywne – ćwiczenie z serii ADALM