Tajniki XMC1100: 32-bitowy Cortex-M0 na 32 MHz

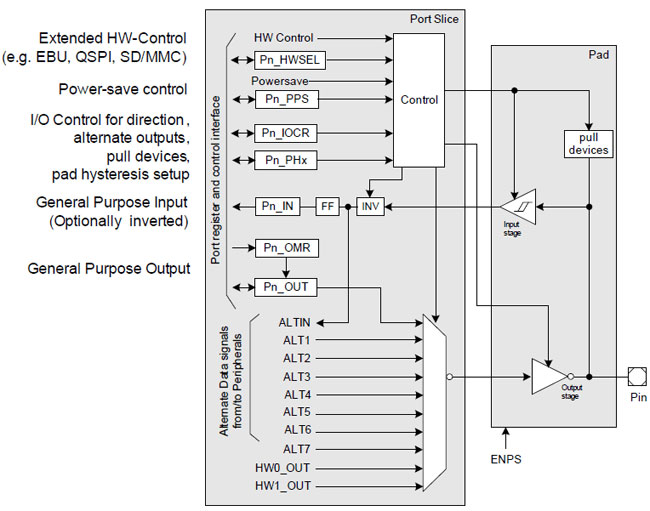

Rzadko spotykane, lecz przydatne w praktyce – zwłaszcza w aplikacjach przemysłowych – rozwiązanie firma Infineon zastosowała także w komórkach GPIO, których schemat blokowy pokazano na rysunku 4. Widoczne na wejściu przerzutniki Schmitta mają programowo zmienianą histerezę, dzięki czemu wybrane linie wejściowe mogą pracować z sygnałami o niezbyt stromych zboczach oraz z sygnałami zakłóconymi (niestabilnymi w czasie z powodu zakłóceń), bez konieczności angażowania programisty i czasu CPU.

Rys. 4. Budowa portów GPIO w mikrokontrolerach XMC1000

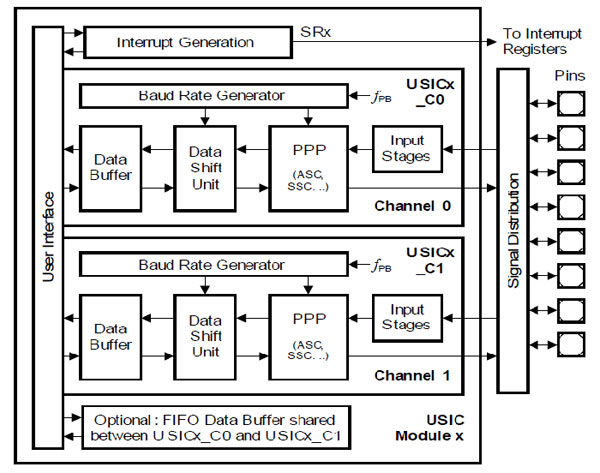

Bardzo zaawansowanymi blokami peryferyjnymi zastosowanymi w mikrokontrolerach XMC1100 są interfejsy komunikacyjne USIC, których schemat blokowy pokazano na rysunku 5. Budowa tych interfejsów także odbiega nieco od najpopularniejszych rozwiązań na rynku: są to bowiem dwa w pełni konfigurowalne kanały komunikacyjne, które mogą pracować (każdy niezależnie) w jednym z trybów, jako: UART, SPI/QSPI, I2C, I2S lub LIN. W trybach SPI/QSPI oraz I2C interfejsy mogą spełniać rolę mastera lub slave’a, w zależności od potrzeb transmisja może się odbywać z wykorzystaniem buforów FIFO lub bez nich.

Rys. 5. Schemat blokowy interfejsu USIC

Poza dużą elastycznością i bogatym wparciem sprzętowym, wspomagającym obsługę protokołów transmisyjnych, niebagatelnym atutem bloków USIC są preskalery częstotliwości taktujących, w których przewidziano możliwość stosowania ułamkowych współczynników, co zwiększa dokładność doboru częstotliwości taktującej każdy kanał komunikacyjny.

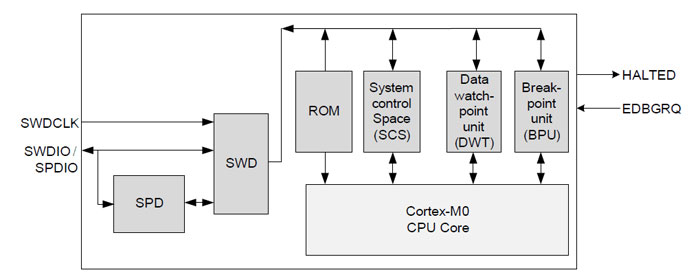

Rys. 6. Schemat blokowy interfejsu Trace&Debug w mikrokontrolerach XMC1100

Ostatnim elementem wyposażenia mikrokontrolerów XMC1100, na który zwrócimy uwagę w artykule, jest – także dość rzadko spotykana w takiej konfiguracji – blok wspomagający debugowanie pracy CPU (rysunek 6), którego pracą użytkownik może sterować za pomocą interfejsu 1- lub 2-przewodowego. Nowością jest wyposażenie go w 1-liniowy interfejs SPD (taktowany do 8 MHz), który – podobnie do SWD – umożliwia m.in.: zatrzymanie pracy CPU, pracę krokową, podgląd zawartości rejestrów i pamięci, zarządzanie 4 sprzętowymi breakpointami i 2 watchpointami, wymuszanie przerwań, zerowanie CPU itp. W większości aplikacji większa niż gwarantowana przez SPD prędkość wymiany danych z interfejsem Trace&Debug nie jest potrzebna, a oszczędzenie jednego wyprowadzenia może mieć duże znaczenie, zwłaszcza w przypadku użycia mikrokontrolera w obudowie TSSOP16.

Na tym kończymy przegląd ponadstandardowych rozwiązań zastosowanych przez producenta w mikrokontrolerach XMC1100 i zachęcamy do podjęcia samodzielnych prób ich poznania, w czym – także ze względu na niską cenę – bardzo pomocny będzie zestaw startowy XMC2go.

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii  Mieszacze aktywne – ćwiczenie z serii ADALM

Mieszacze aktywne – ćwiczenie z serii ADALM