SDAccel – nowe środowisko projektowe Xilinx dla układów FPGA

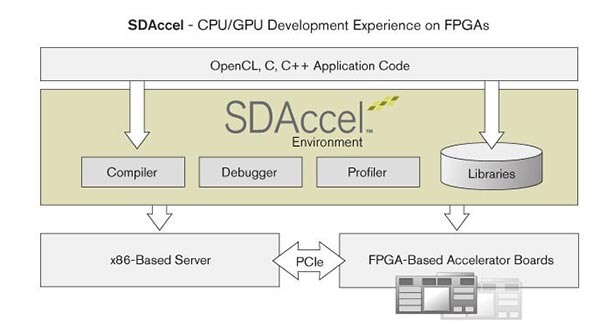

Firma Xilinx ogłosiła wprowadzenie na rynek środowiska programistycznego SDAccel, przeznaczonego do pracy z układami FPGA przy użyciu języków C, C++ oraz frameworku OpenCL. SDAccel jest najnowszym członkiem rodziny SDx, wyposażonym w pierwszy na rynku optymalizujący architektonicznie kompilator obsługujący dowolne połączenia tych trzech technologii i dającym możliwość pracy z układami FPGA w sposób zbliżony do narzędzi znanych z programowania procesorów oraz kart graficznych.

Środowisko dostarcza przykładowy kod oraz biblioteki, pozwala kompilować, debugować i profilować kod na wszystkie platformy docelowe, włączając w to emulację procesorów x86, badanie wydajności z użyciem symulacji oraz wykonywanie kodu na układach FPGA. Zostało zaprojektowane tak, by pozwolić także programistom CPU/GPU na łatwe przenoszenie projektów na FPGA, z możliwością użycia istniejącego kodu OpenCL, C i C++. Z użyciem SDAccel, projektanci mogą wykorzystać znajomy sposób pracy nad kodem i uruchamiania do optymalizacji swoich aplikacji i wykorzystać platformy FPGA nie mając z nimi doświadczenia.

SDAccel wyposażone jest w kompilator, uzyskujący do 25 razy lepszą wydajność z wata w porównaniu z układami CPU i GPU oraz trzykrotnie lepszą wydajność i efektywność wykorzystania zasobów, niż inne rozwiązania FPGA.

Dostarczane ze środowiskiem napisane w języku C biblioteki obejmują algorytmy DSP, przetwarzanie video oraz operacje algebry liniowej, a do specyficznych zastosowań dostępne są też biblioteki OpenCV i BLAS kompatybilne z OpenCL, opracowane przez firmę Auviz Systems.

Środowisko SDAccel pozwala obsługiwać duże aplikacje z wieloma programami i ładowalnymi na życzenie modułami w stylu CPU/GPU. Jako jedyne środowisko na rynku pozwala tworzyć oparte na FPGA jednostki obliczeniowe, mogące ładować nowe jądra akceleratorów w trakcie pracy systemu. Przez cały czas podtrzymywane są przy tym krytyczne funkcje i interfejsy, takie jak pamięć, Ethernet, PCIe oraz monitory wydajności. Rekonfigurowalne w locie jednostki obliczeniowe pozwalają natomiast współdzielić akceleratory FPGA między aplikacjami. Dla przykładu, system można zaprogramować tak, by przełączał się między wyszukiwaniem obrazów, przetwarzaniem ich i transkodowaniem video.

Szczegółowe informacje można znaleźć na stronie producenta.

Polska chce zwiększyć znaczenie sektora półprzewodników. Toczą się prace nad krajową polityką w tym obszarze

Polska chce zwiększyć znaczenie sektora półprzewodników. Toczą się prace nad krajową polityką w tym obszarze  Medicalgorithmics wesprze nowego partnera z Korei Południowej w ekspansji na rynku amerykańskim

Medicalgorithmics wesprze nowego partnera z Korei Południowej w ekspansji na rynku amerykańskim  PGZ i Frankenburg Technologies pogłębiają strategiczną współpracę w obszarze nowoczesnych systemów obronnych

PGZ i Frankenburg Technologies pogłębiają strategiczną współpracę w obszarze nowoczesnych systemów obronnych