STM32F7 (z Cortex-M7): nowe mikrokontrolery w rodzinie STM32

Zmiany, zmiany, zmiany…

Koniec roku 2014 zaowocował wprowadzeniem przez STMicroelectronics pierwszych na świecie mikrokontrolerów wyposażonych w rdzeń Cortex-M7. W artykule – na kilka tygodni przed wprowadzeniem mikrokontrolerów STM32F7 do masowej produkcji – przedstawiamy ich ekspresową prezentację.

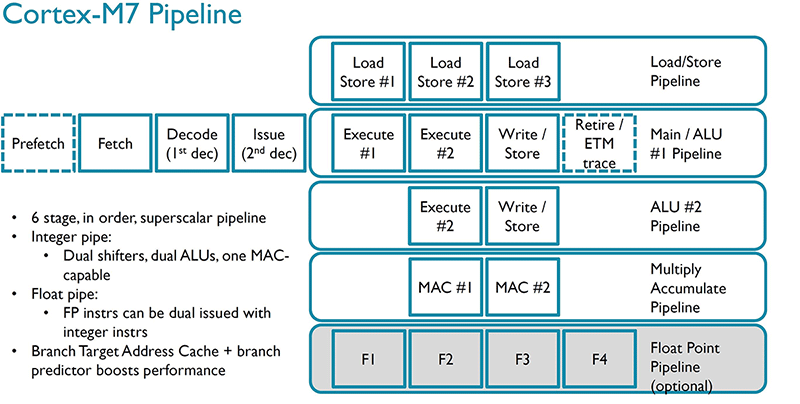

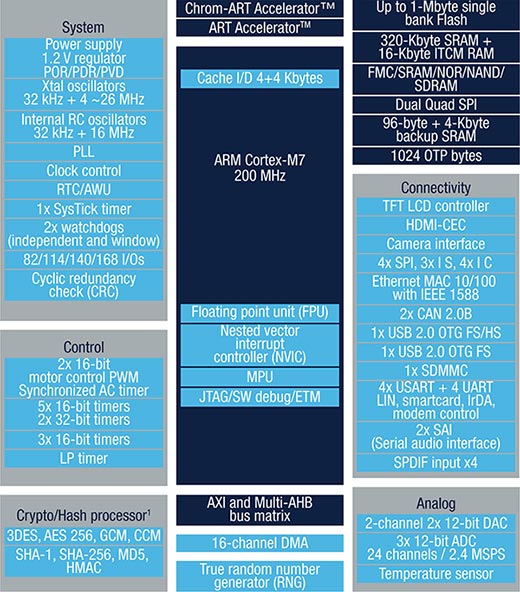

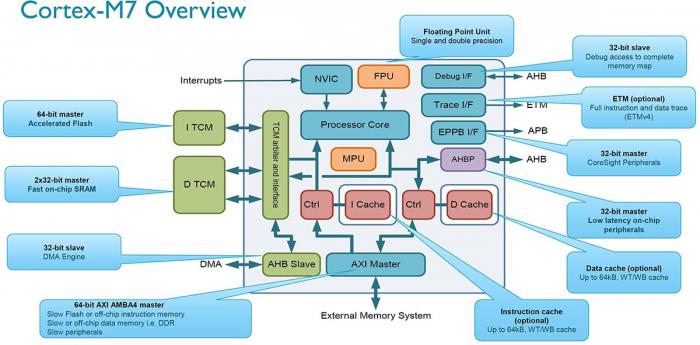

W ostatnich tygodniach 2014 rodzina rdzeni Cortex-M powiększyła się o nowe rozwiązanie nazwane przez firmę ARM mianem Cortex-M7 (schemat blokowy pokazano na rysunku 1). Jest to rozbudowana wersja rdzenia Cortex-M4, przystosowana do współpracy z wewnętrzną, szybką pamięcią SRAM TCM (dla danych i instrukcji programu), wyposażoną w pamięci cache dla danych i instrukcji, a także zaawansowany 6-poziomowy mechanizm przetwarzania potokowego z predykcją oraz sprzętowym wsparciem superskalarnego wykonywania programu (na rysunku 2 pokazano zasadę działania systemu potokowania). Wypadkowa wydajność nowego rdzenia wynosi nawet 5 CoreMark/MHz (do 3,23 DMIPS/MHz), co daje wynik ponad o 47% więcej niż uzyskiwano w przypadku rdzenia Cortex-M4 (3,4 CoreMark/MHz).

Rys. 1. Schemat blokowy rdzenia Cortex-M7

Rys. 2. Działanie systemu potokowania w rdzeniu Cortex-M7

Tab. 1. Podstawowe cechy rdzeni Cortex-M

| Rdzeń | SysTick Timer | Memory Protection Unit | Thumb | Thumb-2 | Sprzętowe mnożenie | Sprzętowe dzielenie | Zintegrowane instrukcje DSP | Konfiguracja pamięci | Nazwa architektury |

| Cortex-M0 | Opcja | – | Wszystkie | Niektóre | 1 lub 32 takty | – | – | Von Neumann | ARMv6-M |

| Cortex-M0+ | Opcja | Opcja | Wszystkie | Niektóre | 1 lub 32 takty | – | – | Von Neumann | ARMv6-M |

| Cortex-M1 | Opcja | – | Wszystkie | Niektóre | 3 lub 33 takty | – | – | Von Neumann | ARMv6-M |

| Cortex-M3 | + | Opcja | Wszystkie | Wszystkie | 1 takt | + | – | Harvard | ARMv7-M |

| Cortex-M4 | + | Opcja | Wszystkie | Wszystkie | 1 takt | + | + | Harvard | ARMv7E-M |

| Cortex-M7 | + | Opcja | Wszystkie | Wszystkie | 1 takt | + | + | Harvard | ARMv7E-M |

Architektura rdzenia Cortex-M7 jest taka sama jak w przypadku rdzeni Cortex-M3 i Cortex-M4 (zgodnie z nomenklaturą firmy ARM nosi ona oznaczenie ARMv7E-M – tabela 1), a jego działanie jest zgodne z definicją architektury Harvard: magistrale zapewniające komunikację z pamięcią danych i poleceń są rozdzielone. Firma ARM w opisie konstrukcyjnym rdzenia użyła nowych mechanizmów obniżających pobór mocy, które są dostępne opcjonalne podczas implementacji rdzenia w nowoczesnych technologiach półprzewodnikowych, charakteryzujących się niewielkim wymiarem charakterystycznym.

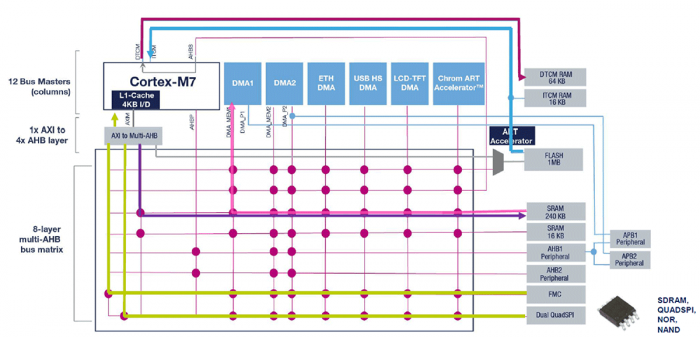

Rys. 3. System magistralowy z interfejsem AXIM zastosowany w mikrokontrolerach STM32F7

Udoskonaleniem wprowadzonym w rdzeniu Cortex-M7 jest nowy interfejs komunikacyjny (de facto jest to konfigurowalna magistrala z lokalnymi kontrolerami) zastosowanym w rdzeniu Cortex-M7 i mającym wpływ na wypadkową prędkość pracy mikrokontrolera, jest Master AXI (AXIM – rysunek 3), który zapewnia „splatanie” kilku kanałów magistrali AHB w jeden, bardzo szybki kanał dwukierunkowej komunikacji rdzenia z otoczeniem (w rdzeniach Cortex-M4 rdzeń komunikuje się z otoczeniem za pomocą „standardowych” interfejsów-magistral AHB).

Pierwszą na świecie firmą, która zdecydowała się na zastosowanie rdzeni Cortex-M7 w swoich mikrokontrolerach jest STMicroelectronics, która poinformowała o pierwszych mikrokontrolerach z nowej rodziny STM32F7 w tym samym momencie, w którym firma ARM wprowadziła oficjalnie na rynek rdzeń Cortex-M7.

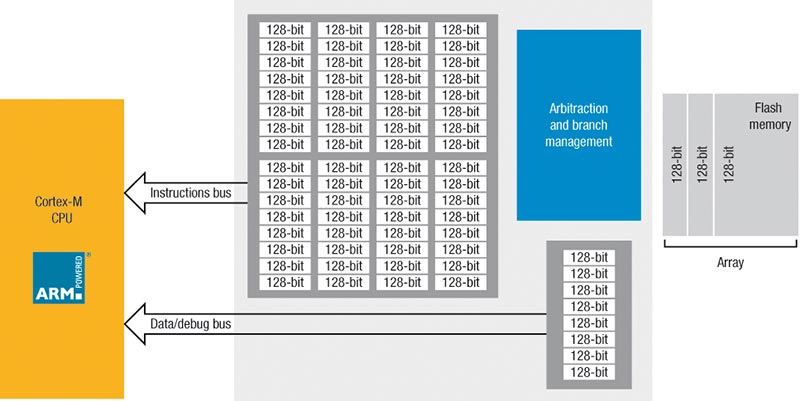

Rys. 4. Schemat blokowy interfejsu ART stosowanego w mikrokontrolerach STM32

Rozwiązania zastosowane przez firmę ARM w rdzeniu Cortex-M7 pozwalają na szybszy niż w przypadku poprzedników dostęp rdzenia do zawartości pamięci SRAM i Flash, oczywiście przy założeniu, że konstrukcja pamięci umożliwia bezpośredni odczyt danych z relatywnie wysoką częstotliwością (dla typowych pamięci nieulotnych za taką uchodzi próg 70-90 MHz). Żeby uniknąć efektu „wąskiego gardła” w dostępie do zawartości pamięci Flash, producenci stosują różne rozwiązania, na przykład w mikrokontrolerach STM32 pobieranie danych z pamięci Flash jest buforowane za pomocą sprzętowego akceleratora ART (Adaptive Real-Time – rysunek 4). Jego działanie polega m.in. na dekompozycji 128-bitowych słów przechowywanych w pamięci Flash na słowa 16- lub 32-bitowe, które są kolejkowane w lokalnej (wbudowanej w ART) pamięci cache. Według informacji publikowanych przez producenta, mechanizmy usprawniające dostęp do zawartości Flash spowodowały, że nie ma konieczności używania podczas odczytu wait-state’ów dotychczas istotnie zmniejszających realną prędkość transferu danych.

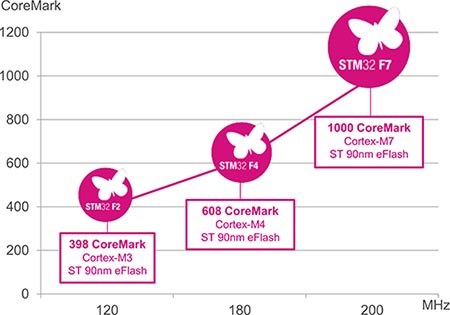

Rys. 5. Wydajności mikrokontrolerów z wybranych rodzin STM32

Efekty zabiegów konstruktorów mikrokontrolerów STM32F7 widać w ich wydajności: przy maksymalnej dopuszczalnej częstotliwości taktowania CPU, wynoszącej obecnie 200 MHz, uzyskiwana jest wartość CoreMark na poziomie 1000 (vs 608 w przypadku STM32F4 @180MHz – rysunek 5), a zgodnie z wybiegającymi w niezbyt odległą przyszłość zapowiedziami producenta, po zmianie technologii półprzewodnikowej używanej do produkcji mikrokontrolerów, planowane jest osiągnięcie wyniku testu CoreMark o wartości 2000.

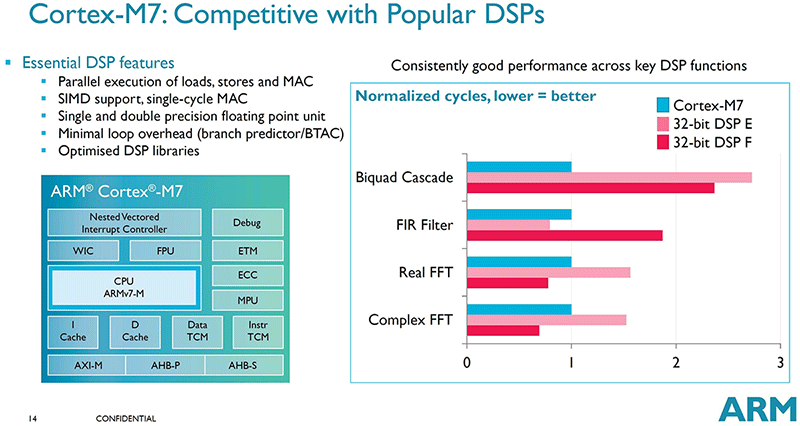

Równie dobre wyniki rdzeń Cortex-M7 uzyskuje w przypadku wyrafinowanych obliczeniowo aplikacji DSP, na rysunku 6 pokazano wyniki (i porównanie wydajności) uzyskane przez Cortex-M7 oraz dwa wyspecjalizowane procesory DSP. Realizacja przykładowych aplikacji bazuje na bibliotekach CMSIS opracowanych i udostępnionych przez ARM.

Rys. 6. Porównanie wydajności w wykonywaniu algorytmów DSP (dla każdego testu punktem odniesienia jest Cortex-M7)

Rys. 7. Schemat blokowy mikrokontrolerów STM32F7

Producent opracowując mikrokontrolery STM32F7 zadbał o wyposażenie ich w bogaty zestaw elementów peryferyjnych (ich schemat blokowy pokazano na rysunku 7), w skład którego wchodzą wszystkie interfejsy znane z poprzednich generacji mikrokontrolerów oraz kilka nowych rozwiązań, w tym m.in.:

- zmodyfikowany podsystem generacji sygnałów zegarowych, pozwalający na modyfikację częstotliwości taktowania bloków peryferyjnych bez konieczności zmiany ustawień taktowania CPU,

- dwukanałowy transceiver I2S z obsługą SPDIF oraz 3 półdupleksowe kanały wejściowe SPDIF, interfejsy USB-OTG z wydzielonym zasilaniem, co pozwala korzystać z tego interfejsu także przy zasilaniu mikrokontrolera napięciem 1,8 V,

- dwa interfejsy QSPI, które sprzętowo realizują transmisję danych z pamięciami wyposażonymi w 1-, 4- lub 8-bitowe interfejsy komunikacyjne.

Mogłoby się wydawać, że bogate wyposażenie wewnętrzne i duże możliwości obliczeniowe muszą spowodować wzrost mocy pobieranej podczas pracy, ale według zapewnień producenta cechy te nie wpłynęły na pogorszenie ich parametrów „oszczędnościowych” w porównaniu z układami STM32F4, co pozwoliło uzyskać wynik 7 CoreMark/mW w trybie Run, statyczny pobór 120 mA w trybie STOP z podtrzymaniem zawartości pamięci SRAM, 1,7 mA w trybie STANDBY oraz 0,1 mA w trybie VBAT.

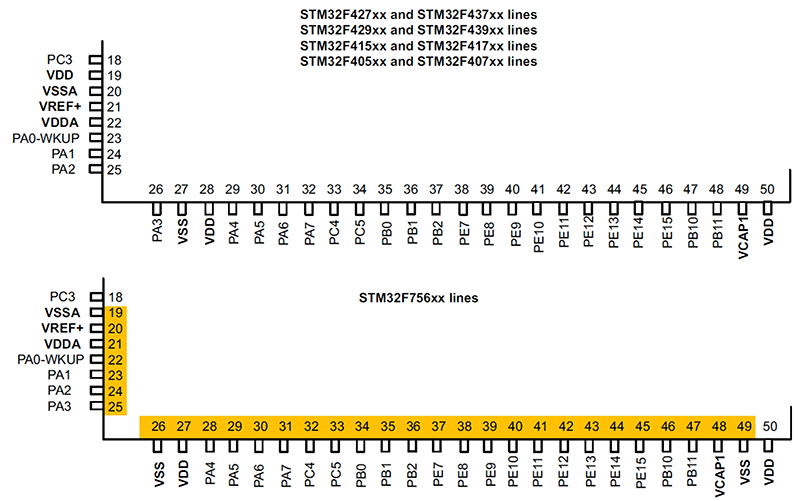

Rys. 8. Producent zapewnił kompatybilność mikrokontrolerów STM32F7 i STM32F4, jedynym wyjątkiem jest obudowa LQFP100

Projektanci podrodziny STM32F7 zadbali o jeszcze jedną ważną rzecz: ich kompatybilność z mikrokontrolerami STM32F4, zarówno pod kątem fizycznego rozmieszczenia wyprowadzeń w obudowie, jak i ich kompatybilności elektryczno-czasowej, co minimalizuje ryzyko powstania problemów w przypadku modyfikowania konstrukcji urządzeń z tymi mikrokontrolerami. Zabieg ten niezupełnie udał się w przypadku najmniejszych dostępnych w rodzinie STM32F7 obudów – LQFP100 – w których 30 wyprowadzeń jest umieszczonych odmiennie w obydwu podrodzinach (rysunek 8). Pozostałe planowane wersje obudów (na razie dla mikrokontrolerów STM32F75x) – LQFP144, LQFP176, UFBGA176, LQFP208, TFBGA216 oraz WLCSP143 – dokładnie odpowiadają mikrokontrolerom STM32F4.

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii