Terasic DE0-Nano – miniaturowy zestaw startowy z FPGA dla początkujących

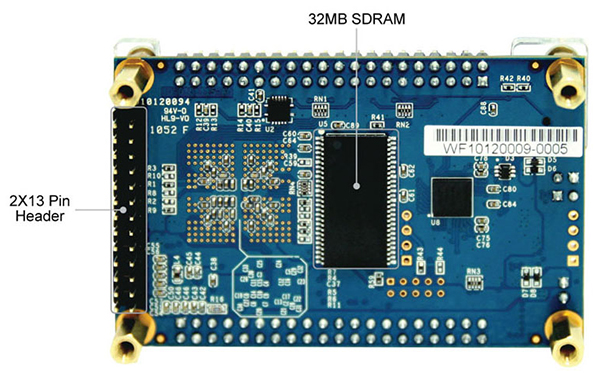

Zestaw Terasic DE0-Nano wyposażono w dwie pamięci dostępne dla aplikacji użytkownika: EEPROM z interfejsem I2C o pojemności 2 kb oraz SDRAM o pojemności 32 MB (jest ona montowana na spodniej stronie płytki zestawu, widać ją na rysunku 4). Standardowym elementem wyposażenia zestawu jest także konfigurator Flash EPCS64, której zadaniem jest przechowywanie konfiguracji FPGA i dostarczanie danych do konfiguracji FPGA po włączeniu zasilania zestawu.

Widoczne na rysunku 3 złącze MiniUSB służy do skomunikowania programatora-konfiguratora wbudowanego w zestaw z oprogramowaniem Quartus II oraz Quartus Prime, za jego pomocą można także zestaw zasilać. Alternatywną ścieżką zasilania zestawu (np. z baterii ogniw) jest 2-stykowe złącze widoczne na rysunku 3 nieco poniżej złącza USB.

Rys. 4. Elementy wyposażenia zestawu Terasic DE0-Nano widoczne od dolnej strony PCB

Na rysunkach 3 i 4 widać trzy złącza szpilkowe, na które wyprowadzono:

- na złącza 40-stykowe dostępne od góry płytki: 72 linie GPIO przystosowane do współpracy z systemami zasilanymi napięciem 3,3 V,

- na złącze 26-stykowe dostępne od dołu płytki: 16 linii GPIO przystosowanych do współpracy z systemami zasilanymi napięciem 3,3 V oraz 8 wejść analogowych (dołączonych do przetwornika A/C).

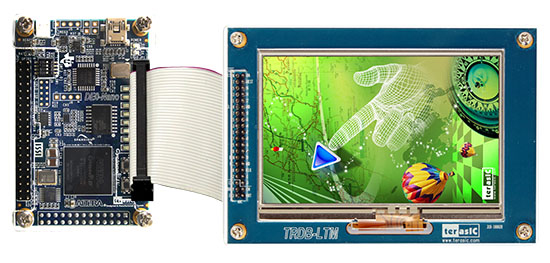

Na wybrane styki złącz doprowadzono ponadto napięcia +3,3 V, +5 V oraz masy GND. Producent zestawu przewidział możliwość dołączania do styków gold-pin różnego rodzaju ekspanderów funkcjonalnych, w tym pochodzących z własnej oferty jak na przykład kolorowy wyświetlacz LCD-TFT z touch-panelem oferowany na module LTM (fotografia 5).

Fot. 5. Do złączy zestawu Terasic DE0-Nano można dołączać ekspandery funkcjonalne, także z oferty firmy Terasic

Implementację poważnych projektów w FPGA zastosowanym w prezentowanym zestawie (EP4CE22F17C6N w obudowie FBGA256) umożliwiają wspomniane już wcześniej duże zasoby logiczne, w tym: 22320 komórek LE, 594 kb wbudowanej w FPGA pamięci RAM, 4 generatory taktujące z PLL, a także 66 sprzętowych multiplikatorów umożliwiających wykonywanie operacji na słowach 18 x 18 bitów. Przykłady przygotowane i bezpłatnie udostępniane użytkownikom zestawu obejmują m.in. implementację 32-bitowego mikroprocesora NIOS II, który jest programowany w języku C. Kompletne środowisko projektowe umożliwiające implementację w prezentowanym zestawie projektów, zarówno czysto sprzętowych FPGA jak i bazujących na implementacji mikroprocesora NIOS II, jest dostępne na stronie firmy Altera bezpłatnie. Jedna ze starszych wersji pakietu Quartus II jest dystrybuowana na DVD wraz z zestawem, ale można – do tego zachęcam – korzystać z aktualnych wersji oprogramowania Quartus Prime.

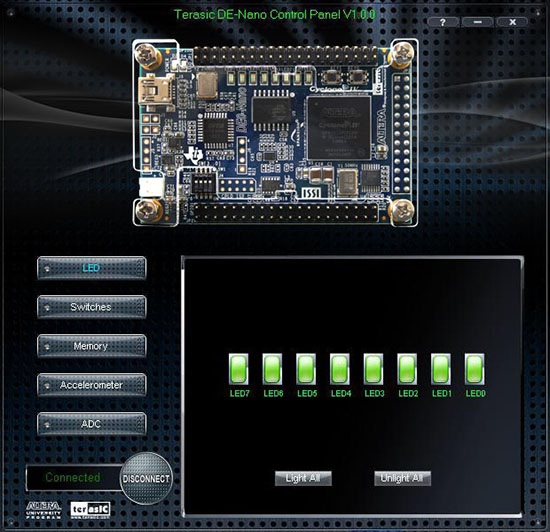

Rys. 6. Widok okna programu DE0-Nano Control Panel

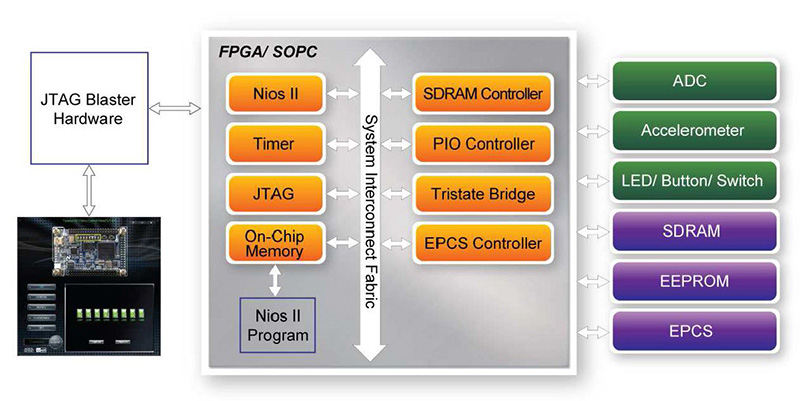

W skład zestawu wchodzi także płyta z oprogramowaniem demonstracyjnym DE0-Nano Control Panel (rysunek 6), którego działanie można obejrzeć na filmie. Za jego pomocą można – po dołączeniu zestawu Terasic DE0-Nano do PC – zweryfikować działanie elementów peryferyjnych zastosowanych na płytce. Aplikacja zaimplementowana w FPGA, realizująca obsługę komunikacji z PC, została zrealizowana na bazie mikroprocesora NIOS II, który został zaimplementowany w FPGA zgodnie ze schematem blokowym pokazanym na rysunku 7.

Rys. 7. Schemat blokowy aplikacji demonstracyjnej, współpracującej z programem DE0-Nano Control Panel, zaimplementowanej w FPGA zestawu Terasic DE0-Nano

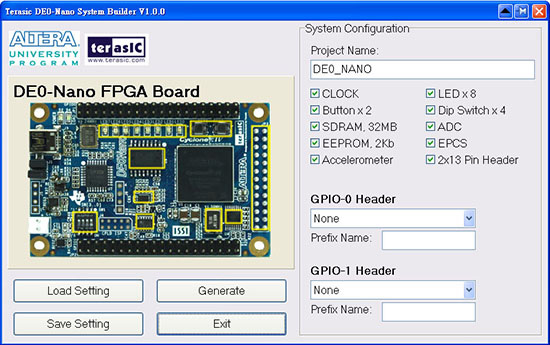

Rys. 8. Widok okna programu DE0-Nano System Builder

Wraz zestawem Terasic DE0-Nano dostarczany jest także program narzędziowy o nazwie DE0-Nano System Builder (rysunek 8), który służy do generowania plików projektu dla środowiska Quartus II z opisem i przypisaniami linii GPIO układu FPGA do elementów peryferyjnych zestawu. Narzędzie to ułatwia i przyspiesza skonfigurowanie projektu i doskonale sprawdza się w przypadku korzystania z domyślnych elementów peryferyjnych oraz ekspanderów funkcjonalnych zdefiniowanych przez producenta, jak choćby wyświetlacz LCD-TFT czy kamera wideo.

Caroline Pannier – nowa dyrektorka targów electronica – analizuje sytuację gospodarczą branży i przedstawia wyniki

Caroline Pannier – nowa dyrektorka targów electronica – analizuje sytuację gospodarczą branży i przedstawia wyniki  Konstrukcja Ventiva Zoned Cooling™ – ukierunkowane chłodzenie powietrza dla urządzeń AI Edge

Konstrukcja Ventiva Zoned Cooling™ – ukierunkowane chłodzenie powietrza dla urządzeń AI Edge  Komunikacja dalekiego zasięgu oparta na technologii Qualcomm dla robotyki i dronów

Komunikacja dalekiego zasięgu oparta na technologii Qualcomm dla robotyki i dronów