[4] Pierwsze kroki z FPGA – szkoła MAXimatora – monitorowanie pracy projektu z użyciem debugera SignalTAP II

Po ustaleniu potrzebnej liczby wejść generujemy (wciskając Generate HDL…) pliki źródłowe debugera w wybranym języku HDL (Verilog lub VHDL). Późniejsze ewentualne modyfikacje parametrów modułu można wygodnie zmieniać otwierając plik TAP74169.qsys i po wprowadzeniu zmian ponownie generując pliki HDL. W tym momencie mamy wygenerowany opis HDL debugera, ale nie został on jeszcze dodany do projektu. Proces ten musimy wykonać ręcznie, co wymaga otwarcia pliku TAP74169.qip (znajduje on się katalogu sciezka_generacji_plikow-debugera\synthesis) i następnie dodania go do projektu (Project>Add Current File to Project).

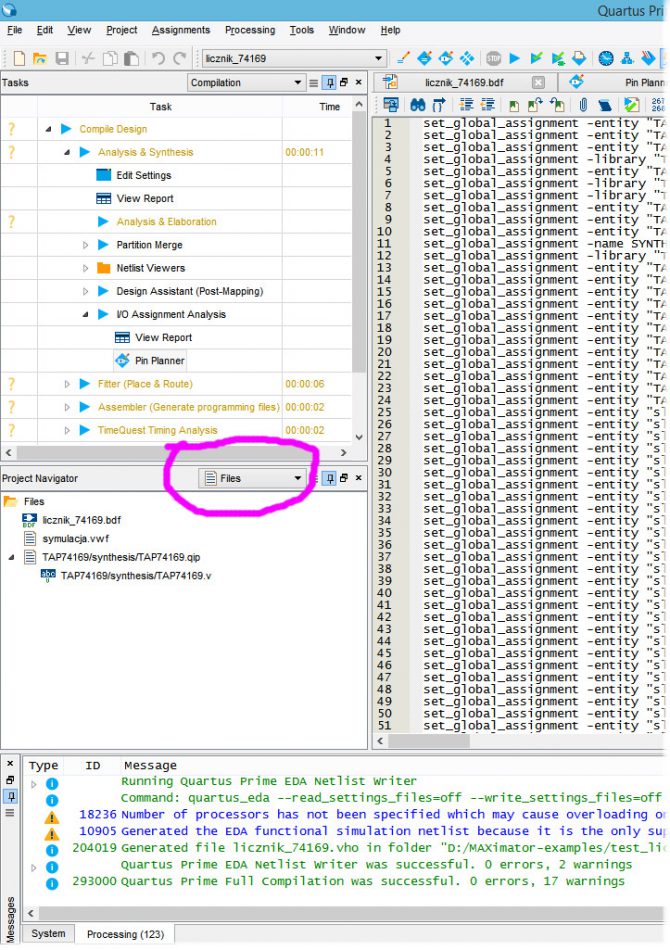

Po wykonaniu tych czynności w nawigatorze projektu (Project Navigator – rysunek 6) wyświetlamy wszystkie pliki wchodzące w skład projektu i rozwijamy gałąź TAP74169/sythesis/ (rysunek 6), w której znajduje się plik HDL z opisem debugera (w przykładzie jest to plik w Verilogu). Klikamy w nazwę pliku prawym klawiszem myszki i wybieramy opcję Create Symbol Files for Current File (rysunek 7), co powoduje dodanie graficznego symbolu debugera do biblioteki projektu.

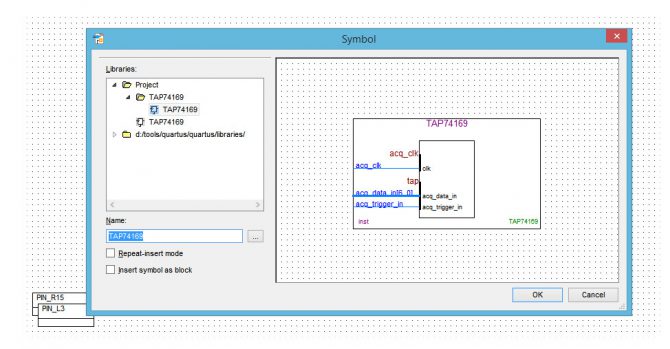

Żeby położyć symbol debugera na planszy schematu postępujemy tak jak w przypadku innych symboli – dwukrotnie klikamy w puste miejsce na planszy, co spowoduje wyświetlenie okna Symbol (rysunek 8), w którym dostępne są dwa symbole TAP74169. Jest to normalne zjawisko, wynikające z pewnych niekonsekwentnych rozwiązań w pakiecie Quartus, przy czym są one nieszkodliwe.

Wybieramy jeden z dostępnych symboli i opisujemy sposób dołączenia linii wejściowych oraz linii wyzwalającej do testowanej części projektu. Odbywa się to w taki sam sposób, jak w przypadku rysowania schematu rozwiązania implementowanego w ramach projektu.

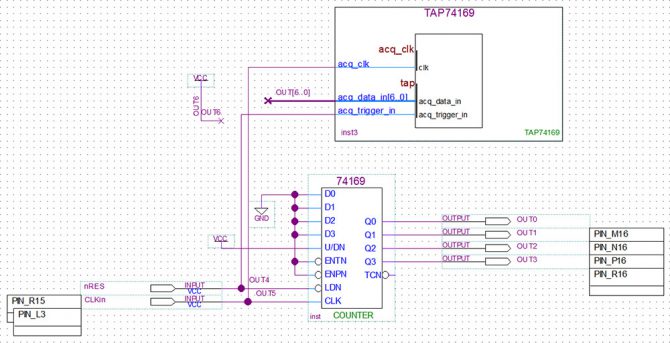

Na rysunku 9 pokazano schemat połączeń układu testowego, w którym jedno z wejść debugera dołączono na stałe do logicznej „1”. Po wykonaniu wszystkich połączeń kompilujemy projekt, żeby wychwycić ewentualne błędy uniemożliwiające jego poprawną implementację. Jeżeli wszystko jest w porządku, możemy przejść do kolejnego kroku – przygotowania pliku debugera.

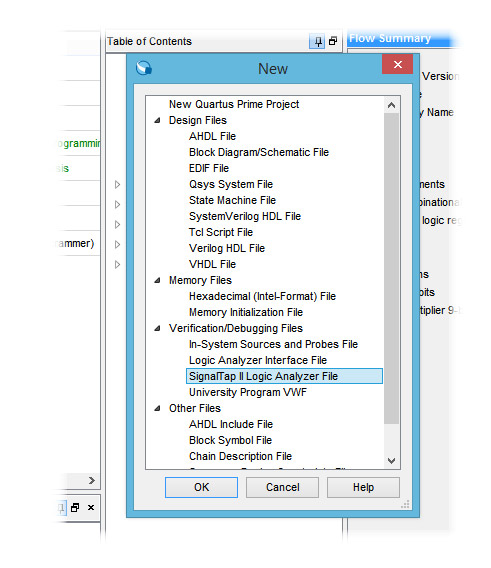

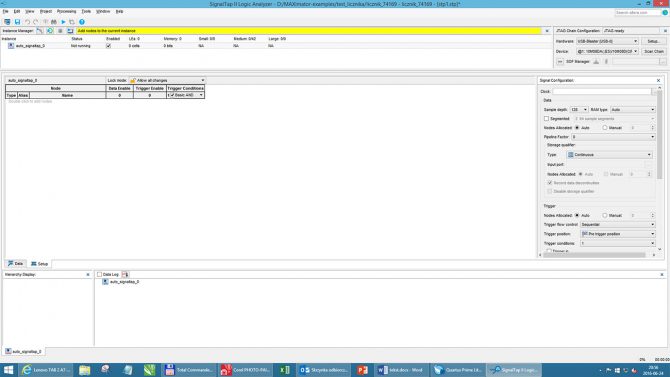

W tym celu wybieramy w menu File>New i w wyświetlonym oknie, w sekcji Verification/Debugging Files (rysunek 10), wybieramy SignalTap II Logic Analyzer File. Okno analizatora pokazano na rysunku 11.

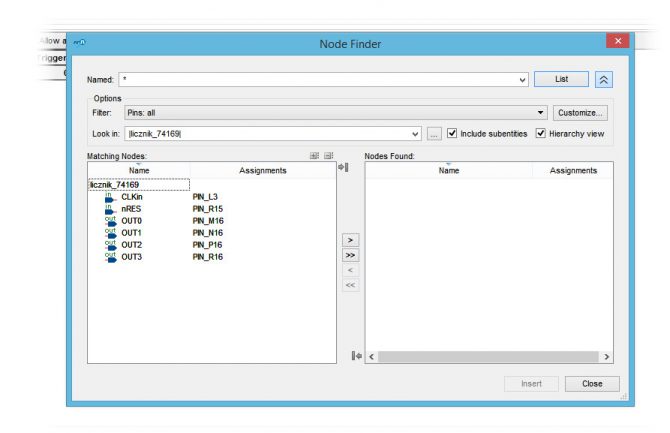

Konfigurację tej części projektu zaczynamy od ustalenia listy monitorowanych sygnałów, co wymaga dwukrotnego kliknięcia w zakładce Setup, w wyniku czego wyświetli się okno Node Finder pokazane na rysunku 12.

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii