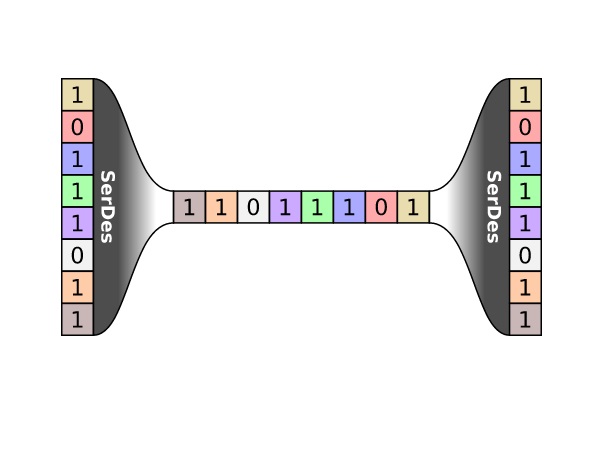

[WEBINARIUM] Projektowanie i charakterystyka kanałów SerDes (Serializer-Deserializer)

CST – Computer Simulation Technology GmbH (Dassault Systèmes) zaprasza na webinarium „Projektowanie i charakterystyka kanałów SerDes (Serializer-Deserializer)”.

CST – Computer Simulation Technology GmbH (Dassault Systèmes) zaprasza na webinarium „Projektowanie i charakterystyka kanałów SerDes (Serializer-Deserializer)”.

Webinarium odbędzie się 19.10.2017 o godz. 17:00. Czas trwania: ok.1 godz.

Projektowanie kanału szybkiej transmisji danych (High Speed Channel) zazwyczaj obejmuje dwa etapy. W fazie pre-layout przestrzeń projektowa jest badana metodą analizy „what-if„. W fazie post-layout dominuje sprawdzanie funkcjonalności przed wyprodukowaniem prototypu. W obu etapach należy wziąć pod uwagę realistyczne modele nadajników PISO (Parallel Input Serial Output) i odbiorników SIPO (Serial Input Parallel Output). Modele te powinny uwzględniać istotne charakterystyki układów takie, jak jitter, modulację i wyrównywanie (equalization).

Webinarium poprowadzi dr Klaus Krohne (CST / Market Development Manager for EDA).

Szczegóły i rejestracja na stronie https://www.cst.com/events/webinars/serdes-2017

Tajwańskie stowarzyszenie TEEMA rozważa utworzenie Parku Technologicznego w Polsce

Tajwańskie stowarzyszenie TEEMA rozważa utworzenie Parku Technologicznego w Polsce  Microchip rozszerza zakres usług bezpieczeństwa w ramach Trust Platform

Microchip rozszerza zakres usług bezpieczeństwa w ramach Trust Platform  ADLINK wprowadza moduły MXM oparte na architekturze NVIDIA Blackwell

ADLINK wprowadza moduły MXM oparte na architekturze NVIDIA Blackwell