[RAQ] Magia! Decymatory powielają wirtualne kanały przetwornika ADC

Pytanie:

Kupiłem dwukanałowy przetwornik ADC i skonfigurowałem decymatory. Teraz okazuje się, że otrzymałem 4 przetworniki! Czy występuje tu gdzieś przetwornik danych 2-do-1, o którym nie wiedziałem?

Odpowiedź:

Od momentu powstania pierwszych monolitycznych, krzemowych przetworników analogowo-cyfrowych (ADC) układy tego typu podążały za najnowszymi udoskonaleniami procesu technologicznego. Wcześniejsze przetworniki wykorzystywały bardzo proste układy cyfrowe, nie licząc korekcji błędów i cyfrowych sterowników. Obecnie natomiast można stworzyć tani przetwornik ADC z bardzo zaawansowanym przetwarzaniem cyfrowym. Nowa rodzina przetworników gigasamplowych (GSPS), zwanych również przetwornikami ADC RF powstała dzięki procesowi technologicznemu CMOS 65 nm i pozwala na integrację wielu cyfrowych funkcji przetwarzania, które usprawniają pracę takiego przetwornika.

Przy wysokich, gigasamplowych szybkościach mamy do czynienia z dużą przepustowością danych liczoną w bitach na sekundę. Wybrany dla przykładu układ AD9680 jest podwójnym 14-bitowym przetwornikiem o częstotliwościach próbkowania 1,25 GSPS, 1 GSPS, 720 MSPS lub 500 MSPS obsługującym standard JESD204B. Przyjmując maksymalną wartość 1,25 GSPS, otrzymujemy przepustowość:

Taka ilość wymagałaby wykorzystania ogromnej liczby linii LVDS w celu ekstrakcji wszystkich danych cyfrowych. Aby umożliwić implementację tak dużej przepustowości, został wykorzystany standard JEDS204B. Jest to protokół transmisji wysokiej szybkości wykorzystujący kodowanie 8b/10b i scrambling oraz inne rozwiązania w celu zapewnienia odpowiedniej integralności sygnału. Użycie standardu JESD204B oznacza, że całkowita przepustowość wynosi

Dzięki zastosowaniu standardu JESD204B dane można podzielić na cztery szybkie linie szeregowe, każda o przepustowości 12,5 Gb/s. W przypadku interfejsu LVDS, którego każda linia jest ograniczona do przepustowości około 1 Gb/s, oznaczałoby to ponad 28 par!

Rzut oka na kartę katalogową AD9680 pozwala zauważyć, że konfiguracja łącza jest skomplikowana. Wcześniejsze generacje przetworników ADC z interfejsem LVDS były łatwiejsze w implementacji, natomiast przetworniki JESD205B są bardziej złożone. Sytuacja komplikuje się jeszcze bardziej po uwzględnieniu konfiguracji cyfrowego decymatora (DDC). Konfiguracja przetwornika ADC jest określona główne przez trzy litery:

- L – liczba linii na łącze JESD204B

- M – liczba przetworników na łącze JESD204B

- F – liczba oktetów w ramce danych w łączu JESD204B

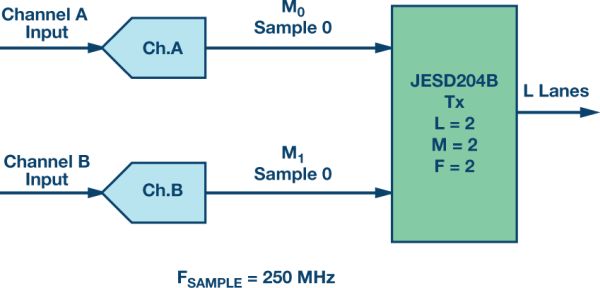

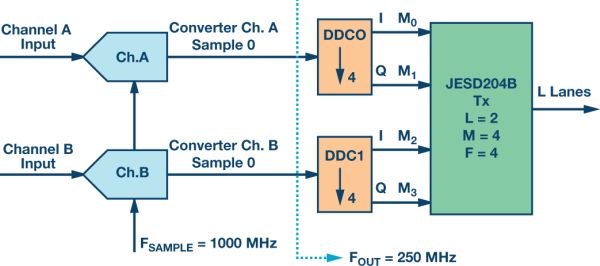

Przykładowo, model AD9250 jest podwójnym 14-bitowym przetwornikiem analogowo-cyfrowym o szybkości 250 MSPS z interfejsem JESD204B. Rys. 1. przedstawia układ AD9250 w domyślnej konfiguracji.

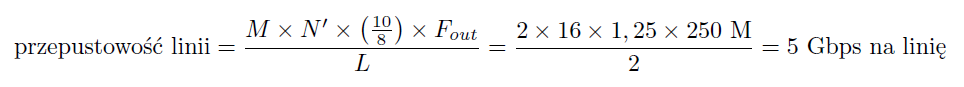

W tej konfiguracji łącze JESD204B (reprezentowane przez nadajnik JESD204B) działa w dość oczywisty sposób, ponieważ w układzie AD9250 nie jest wykonywane dodatkowe przetwarzanie. Kanał A odpowiada przetwornikowi 0 (M0), kanał B – przetwornikowi 1 (M1), a zatem wartość M wynosi 2. Kompletne równanie opisujące tą konfigurację to

Porównajmy tą sytuację z układem AD9680 pracującym z szybkością GSPS – jednak w tym przypadku dwa decymatory pracują w trybie kwadraturowym (I/Q). Rys. 2. pokazuje, gdzie znajdują się decymatory dzielące częstotliwość próbkowania 1 GSPS na 4. Otrzymana w wyniku tego częstotliwość próbkowania (FOUT) jest równa 250 MSPS.

Na rys. 2. widać wyraźnie, że układ AD9680 może efektywnie zmniejszyć częstotliwość próbkowania dzięki wbudowanym cyfrowym decymatorom. Ponieważ na każdym wyjściu DDC znajduje się strumień o rozdzielczości 16 bitów, nie ma już związku między fizycznymi strumieniami przetwornika a parametrem M związanym ze specyfikacją JESD204B. Zgodnie ze standardem M jest liczbą przetworników przypadających na strumień. W tym zmodyfikowanym przykładzie M staje się parametrem zwanym przetwornikiem wirtualnym. Choć układ AD9680 fizycznie ma tylko dwa kanały (A i B), tryb kwadraturowy decymatora generuje cztery różne 16-bitowe strumienie danych przekazywanym do interfejsu JESD204B. Z punktu widzenia tego interfejsu istnieją teraz 4 (wirtualne) przetworniki generujące strumienie bitów. Wobec tego M staje się równe 4, co oznacza zwielokrotnienie przetworników. W takim scenariuszu przepustowość linii na wyjściu staje się równa

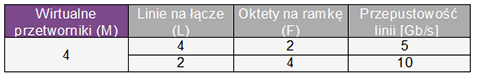

Elastyczność interfejsu JESD204B dostępna w układzie AD9680 jest w tym scenariuszu bardzo widoczna. Dzięki niej otrzymujemy dwie możliwości w zależności od szybkości linii, jaką jest w stanie zaakceptować układ odbiorczy (specjalizowany lub FPGA). Tabela 1. przedstawia opcje dostępne dla interfejsu JSD204B w konfiguracji AD9680 przedstawionej na rys. 2.

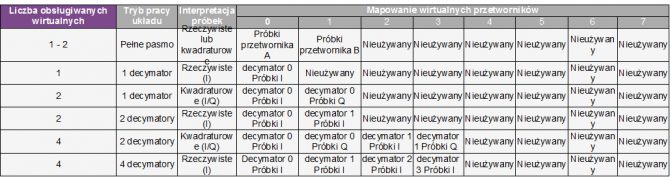

Tabela 2. Przedstawia możliwe mapowania wirtualnych konwerterów w różnych konfiguracjach dla przetwornika ADC przetwornika wyposażonego w 4 cyfrowe decymatory, takiego jak AD9680.

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii