[RAQ] Niskonapięciowy wzmacniacz operacyjny w roli bufora wysokiego napięcia dzięki układowi bootstrap

Właściwa implementacja układu

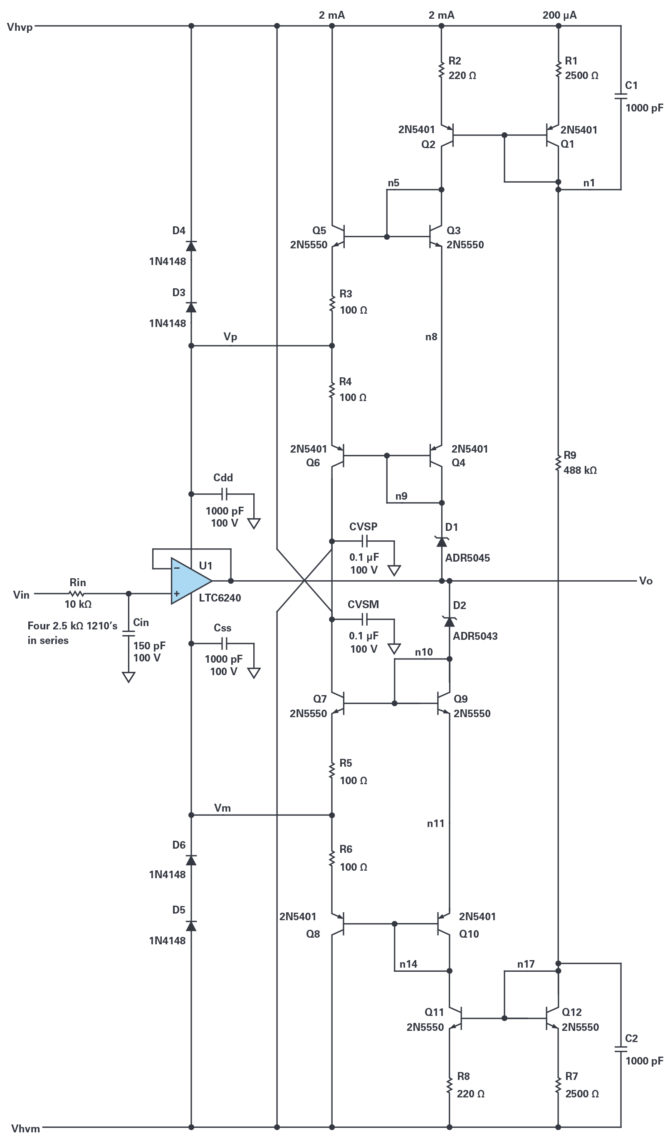

Rysunek 3 prezentuje pełny układ.

Warto zwrócić uwagę, że kondensator 1000 pF musi znajdować się blisko wyprowadzeń zasilania LTC6240. Wzmacniacze operacyjne zawierają mnóstwo tranzystorów, a w tym konkretnym układzie ich częstotliwość graniczna jest rzędu gigaherców. Są też często połączone w pętle sprzężenia między sobą, a więc jeśli nie ma kondensatorów blokujących, mogą samoistnie oscylować przy wysokich impedancjach zasilania dla prądu zmiennego. Wartość 1000 pF jest wystarczająca, by stłumić te oscylacje. Chcemy również, aby kondensator blokujący był o wiele większy niż jakakolwiek pojemność obciążająca wyjście, ponieważ na wysokich częstotliwościach sygnały przechodzące przez pojemność obciążenia powodują przepływ prądu na liniach zasilania. To z kolei wpływa na napięcie zasilania i również może powodować powstawanie oscylacji. Kondensatory blokujące zapobiegają modulacjom napięcia zasilania, a także redukują sprzężenie między wyjściem a zasilaniem.

Opis układu

Przez kondensatory blokujące będzie płynął duży prąd i to w obu kierunkach. Tranzystory Q5 i Q6 pracują jako wtórniki emiterowe sterujące kondensatorami. Q3 i Q4 pracują jak diody ustalające prąd spoczynkowy tranzystorów Q5 i Q6. Q2 dostarcza prąd polaryzujący te diody, a także diodę zenera D1 (lub częściej układ scalony napięcia referencyjnego), która ustala dodatnie napięcie zasilania zależne od sygnału wyjściowego. Kolektor tranzystora Q2 jest wyjściem lustra prądowego polaryzowanego przez rezystor R9 między szynami zasilania. R9 można zastąpić dwoma źródłami prądowymi jeśli napięcia zasilania nie są stałe.

Tranzystory od Q7 do Q12 tworzą sterownik napięcia ujemnego, który jest odwzorowaniem powyższego układu. Warto zwrócić uwagę na różnicę napięć zenera: 5 V w gałęzi dodatniej i 3 V w gałęzi ujemnej. Ta różnica pozwala ustawić napięcie wyjściowe w zakresie obsługiwanym przez zasilanie LTC6240.

W normalnych warunkach prąd zasilania układu LTC6240 przechodzi przez emiter Q5 i otwiera jednocześnie Q6, co sprawia, że impedancja wyjściowa bufora Vp to głównie rezystancja R3. Pasmo pętli sprzężenia zwrotnego od strony dodatniej wynosi więc ok. 1/(2π x 100 Ω x 0,001 µF) = 1,6 MHz. To gwarantuje, że wzmocnienie pętli w okolicach 10 MHz jest mniejsze niż 1. A właśnie tam faza wzmacniacza LTC6240 w otwartej pętli może spowodować oscylacje. Rezystor 100 Ω pozwala również wtórnikowi Q5 nie sterować bezpośrednio pojemności 1000 pF. Wtórniki emiterowe wykazują bowiem indukcyjność wyjściową, która może rezonować z obciążeniem pojemnościowym, powodując dzwonienie, a nawet oscylacje.

Zaprojektowany układ bootstrap nie zadziała więc powyżej częstotliwości 1,6 MHz. Za chwilę dowiemy się jednak, że już powyżej 100 kHz działanie układu zacznie się psuć. Jeśli wyjście nie naśladuje dokładnie wejścia, korzyści z zastosowania układu bootstrap spadają. Elementy Rin oraz Cin ograniczają pasmo do 100 kHz, działając jako część filtru antyaliasingowego przetwornika ADC. Tłumią także interferencje radiowe oraz sygnały o zbyt stromych zboczach.

Zabezpieczenia układu

Układ musi być w stanie przetrwać sygnały o dowolnej szybkości narastania oraz wyładowania elektrostatyczne. Rezystor Rin ogranicza również prąd wejściowy. Rezystancję podzielono na cztery segmenty połączone szeregowo, aby podzielić sygnał wejściowy, a także umożliwić wytrzymanie skoków napięcia nawet do 1 kV. W zależności od źródła sygnału oraz przewidywanych obciążeń wejścia, można zastosować mniejszy rezystor.

W układzie zastosowano diody zabezpieczające, które ściągają prądy wejściowe do szyn zasilania Vp lub Vm. Maksymalny prąd, jaki można doprowadzić do wrót wejściowych LTC6240 wynosi 10 mA, ale gdy połączymy je z układem, który może szybko odłączyć prąd wejściowy, to na wejście układu można przez krótką chwilę podać wyższy prąd. W docelowej aplikacji tą rolę będzie pełnić przekaźnik SPDT. Gdy będzie on wyłączony, to sygnał wejściowy zostanie przekierowany do dzielnika 1:10. Natomiast gdy przekaźnik będzie włączony, sygnał wejściowy będzie bezpośrednio połączony z buforem. Wobec tego, gdy przekaźnik jest wyłączony, bufor jest podłączony do źródła o impedancji dużo większej niż 10 kΩ, a prąd i napięcie wejściowe jest zredukowane, by utrzymać ciągły prąd wejściowy poniżej 10 mA.

Układ ograniczający prąd

Zakres napięcia wejściowego mojej aplikacji to ±400 V z możliwością krótkotrwałego wytrzymania napięcia ±1000 V. Można to zrobić bezpiecznie jedynie wówczas, gdy układ zawiera dwa komparatory, które mogą wykryć nadmierne napięcie na wejściu i szybko włączyć przekaźnik. To może trwać od 1 ms do 2 ms, co pozwoli ograniczyć prąd chwilowy do 100 mA – wartości, która nie przepali diod zabezpieczających układ LTC6240. Warto zwrócić uwagę, że diody od D3 do D6 przełączają nadmierny prąd wejściowy przepływający przez LTC6240 do linii Vp i Vm na szyny zasilania Vhvp oraz Vhvm. Te szyny prawdopodobnie nie są w stanie przyjąć tego prądu, gdyż płynie on w przeciwnym kierunku niż prąd zasilania – będziemy musieli więc polegać na dużej pojemności kondensatora, która pozwoli utrzymać napięcie zasilania podczas oczekiwania na przełączenie przekaźnika. Aby przeciwstawić się zmianie napięcia o 2 V przez 2 ms spowodowanej przez prąd 100 mA, będziemy potrzebowali kondensatora o pojemności 100 µF.

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii