[WEBINARIUM] Projektowanie FPGA w języku C/C++ za pomocą narzędzia SmartHLS

Microchip zaprasza na webinarium poświęcone tematyce obsługi narzędzia SmartHLS służącego do implementacji algorytmów zapisanych w C/C++ w układach FPGA. Webinarium będzie dwudniowe i odbędzie się 19 oraz 20 października 2021. W oba dni sesje rozpoczną się o godzinie 14.00 i potrwają 90 minut. Całe wydarzenie organizowane jest w języku polskim.

Obecne trendy w sektorze systemów wbudowanych oraz układów FPGA to zadawanie układom zadań, które wymagają coraz większej mocy obliczeniowej. Często dotyczą one przetwarzania wideo, sterowania silnikami oraz ogólnego przetwarzania cyfrowego. Tak skomplikowane algorytmy niełatwo zaimplementować w tradycyjnych językach opisu sprzętu (Verilog, VHDL). W sukurs przychodzą algorytmy dostępne już w języku C/C++, które można wykorzystać dzięki programowi SmartHLS.

Obie sesje w języku polskim pozwolą zaprezentować w jaki sposób zaprojektować metodę w C/C++, przetestować kod, a także pogodzić to z dużymi możliwościami zrównoleglania operacji układów FPGA.

Program webinarium obejmuje:

- Wprowadzenie i omówienie cech układów FPGA Microchip,

- Omówienie paradygmatu syntezy wysokiego poziomu,

- Jak użyć narzędzia SmartHLS do syntezy wysokiego poziomu.

Wydarzenie poprowadzi Mirosław Dybizbański, inżynier aplikacyjny firmy Microchip

Microchip rozszerza zakres usług bezpieczeństwa w ramach Trust Platform

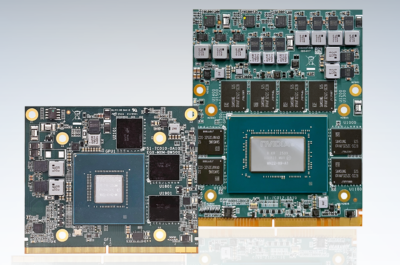

Microchip rozszerza zakres usług bezpieczeństwa w ramach Trust Platform  ADLINK wprowadza moduły MXM oparte na architekturze NVIDIA Blackwell

ADLINK wprowadza moduły MXM oparte na architekturze NVIDIA Blackwell  Polski przemysł obronny stoi dziś w punkcie zwrotnym

Polski przemysł obronny stoi dziś w punkcie zwrotnym