[RAQ] Izolacja w układach z przetwornikami analogowo-cyfrowymi SAR

Pytanie:

Jak dodać izolację do układu z przetwornikiem ADC, aby nie pogorszyć jakości próbkowania?

Odpowiedź:

Podczas projektowania izolacji przetworników analogowo-cyfrowych wysokiej klasy należy zwrócić uwagę przede wszystkim na sygnały zegarów i izolację zasilania.

Przetworniki ADC z sukcesywną aproksymacją (SAR) tradycyjnie stosowano przy niższych częstotliwościach próbkowania i niższych rozdzielczościach. Obecnie jednak dostępne są szybkie i precyzyjne, 20-bitowe przetworniki próbkujące z szybkością 1 MSPS, np. LTC2378-20, Na rynku są również układy z nadpróbkowaniem, o rozdzielczości 32 bitów, takie jak LTC2500-32. Podczas projektowania układu z przetwornikiem ADC wymagany jest bardzo niski poziom szumów w całym torze sygnałowym. Jednak należy pamiętać, że izolacja galwaniczna ma znaczący wpływ na parametry systemu.

Podczas izolacji przetworników analogowo-cyfrowych należy rozważyć trzy zagadnienia:

- Izolację zasilania,

- Separację sygnałów danych,

- Izolację zegara taktującego przetwornik.

Izolacja zasilania (porównanie topologii Flyback i Push-Pull)

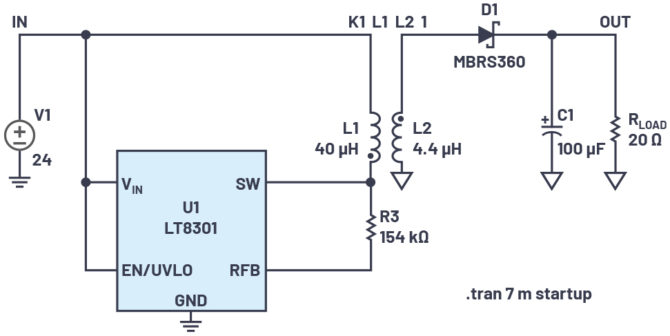

Do izolacji galwanicznej zasilania powszechnie stosuje się przetwornice typu flyback. Rysunek 1 prezentuje schemat tego typu konwertera. Zaletą topologii jest prostota oraz niewielka liczba wymaganych elementów. Przetwornice mają tylko jeden klucz, który jednak może być głównym źródłem szumu w torze sygnałowym. Konwerter flyback generuje wiele nieliniowości, co powoduje m.in. powstawanie emisji elektromagnetycznych (EMI) mających negatywny wpływ na sprawność funkcjonowania układu.

Rysunek 1. Typowa topologia konwertera Flyback

Rysunek 1. Typowa topologia konwertera Flyback

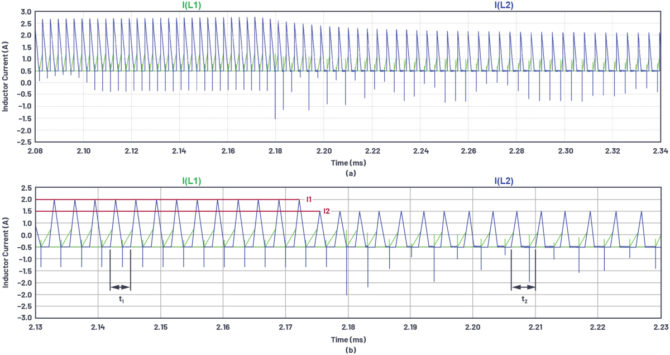

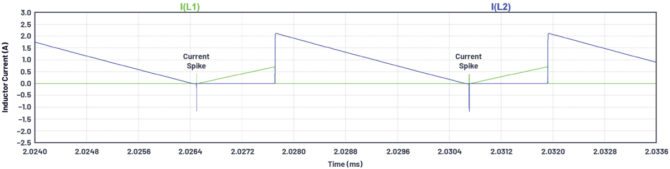

Rysunek 2 przedstawia przebiegi prądów w uzwojeniach transformatora. Prądy w uzwojeniu pierwotnym (L1) i wtórnym (L2) w bardzo krótkim czasie zmieniają się między wysokimi wartościami i zerem. Zmiany te są doskonale widoczne także na rysunku 3. Przepływający prąd powoduje magazynowanie energii w indukcyjności w uzwojeniu pierwotnym. Przy wyłączaniu klucza energia natychmiast przekazywana jest do indukcyjności w uzwojeniu wtórnym, co powoduje powstawanie stanów nieustalonych oraz generowanie szumów. Efekty szumów przełączania trzeba redukować, a więc konieczne jest wprowadzenie do projektu tłumików i filtrów. Oprócz tego w topologii flyback trzeba także stosować stosunkowo większe transformatory ze względu na wymagane wysokie indukcyjności. Ponadto, gorące pętle konwertera są duże i niełatwe do zarządzania.

Więcej informacji na temat gorących pętli uzyskasz w nocie aplikacyjnej AN139.

Rysunek 2. Prądy w uzwojeniach transformatora w układzie z LT8301

Kolejnym problemem topologii flyback są wahania częstotliwości przełączania. Na rysunku 3 można zauważyć zmianę częstotliwości spowodowaną zmianą obciążenia układu. Częstotliwość spada wraz ze spadkiem prądu obciążenia (t1 < t2). Takie wahania mogą w generować szumy i nieliniowości w zupełnie nieprzewidywalnych momentach.

Dodatkowo, różnice w częstotliwościach przełączania występują nawet pomiędzy różnymi egzemplarzami układu. Utrudnia to dobór parametrów filtra, ponieważ istnieje możliwość, że konieczny będzie indywidualny dobór elementów do każdej produkowanej płytki PCB.

Biorąc pod uwagę, że w 20-bitowym przetworniku SAR ADC z zakresem wejściowym 5 V, najmniej znaczący bit (LSB) odpowiada różnicy ~5 μV, to należy zapewnić, że błędy wprowadzane przez szumy są mniejsze niż 5 μV. Oznacza to, że topologia flyback może nie być najlepszym wyborem do izolacji zasilania w systemach precyzyjnych.

Rysunek 3. (a) Zmiana częstotliwości układu LT8301 (b) zbliżenie na zmianę okresu z 2,13 ms na 2,23 ms

Rysunek 3. (a) Zmiana częstotliwości układu LT8301 (b) zbliżenie na zmianę okresu z 2,13 ms na 2,23 ms

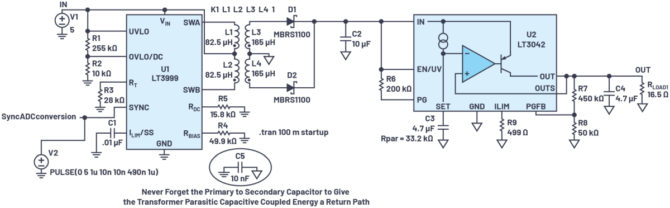

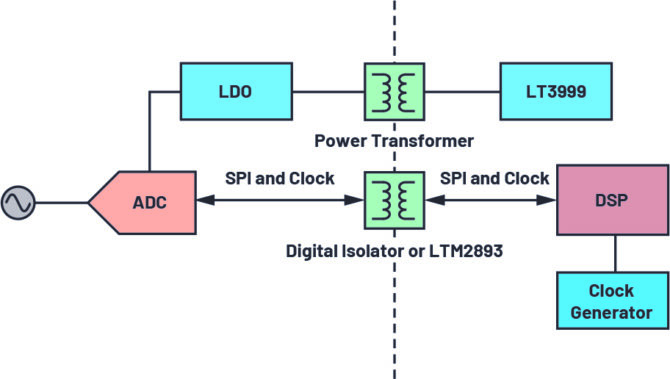

Istnieją jednak inne topologie z izolowanym zasilaniem, zapewniające niższe szumy i mniejszą emisję promieniowania. Znacznie lepsze pod tym względem są m.in. układy push-pull. Konwertery takie jak LT3999 oferują możliwość synchronizacji przełączania klucza z zegarem przetwornika ADC, co pomaga osiągnąć wysoką sprawność rozwiązania. Rysunek 4 pokazuje układ LT3999 w izolowanym obwodzie zasilania z synchronizacją z zegarem taktowania przetwornika ADC. Pojemność między masą po stronie pierwotnej i po stronie wtórnej zapewnia szumom drogę powrotną, co pozwala ograniczyć efekty szumów współbieżnych. Koncepcję tą można zrealizować jako pojemność pomiędzy nakładającymi się warstwami na PCB i/lub jako zwykły kondensator.

Rysunek 4. Układ LT3999 z dodatkowym niskoszumnym stabilizatorem na wyjściu

Rysunek 4. Układ LT3999 z dodatkowym niskoszumnym stabilizatorem na wyjściu

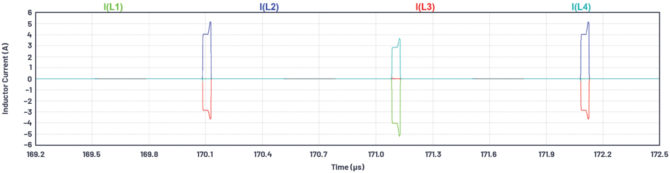

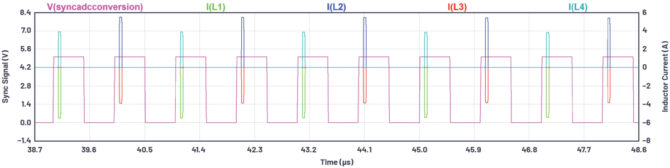

Rysunek 5 przedstawia przebiegi prądu na transformatorze, zarówno po stronie pierwotnej, jak i wtórnej. Taki kształt prądu zapewnia lepsze wykorzystanie transformatora, a także niższe zakłócenia EMI.

Rysunek 5. Przebiegi prądu na transformatorze w układzie z LT3999

Rysunek 5. Przebiegi prądu na transformatorze w układzie z LT3999

Rysunek 6 prezentuje sposób synchronizacji konwertera z zewnętrznym zegarem. Koniec fazy akwizycji danych w ADC jest związany z narastającym zboczem sygnału na pinie SYNC. Jak widzimy na przebiegach, następuje po tym dość długi moment ciszy na linii zasilania. Pozwala to na pobranie kolejnej próbki bez obawy, że proces zostanie zakłócony niepożądanymi stanami nieustalonymi. Przykładowo, przetwornik LTC2378-20 ma czas akwizycji rzędu 312 ns, a więc bez problemu mieści się w luce czasowej ok. 1 µs.

Rysunek 6. LT3999 i zależności prądowe podczas synchronizacji z sygnałem zewnętrznym

Rysunek 6. LT3999 i zależności prądowe podczas synchronizacji z sygnałem zewnętrznym

Izolacja danych

Izolację sygnałów danych można wykonać przy użyciu tradycyjnych izolatorów cyfrowych, np. z rodziny ADuMx. Układy te dostępne są dla wielu standardowych interfejsów takich jak SPI, I2C, CAN itd. Przykładowo układ ADuM140 służy do izolacji magistrali SPI. Aby osiągnąć pełną izolację interfejsu, przez układ powinny przepływać sygnały: zegara, SDO, SCK i Busy. Separacja sygnałów danych polega na tym, że energia elektryczna jest przenoszona ze strony pierwotnej na wtórną poprzez barierę indukcyjną. Rozwiązanie powinno koniecznie zawierać ścieżkę powrotną prądu, co jest realizowane poprzez pojemność. Można ją wykonać jako sprzężenie pomiędzy nakładającymi się na siebie warstwami na PCB.

Izolacja zegara

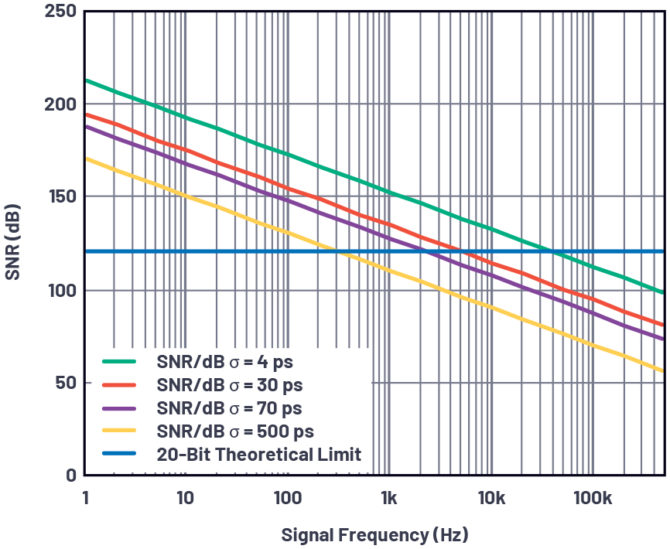

Bardzo ważnym zadaniem jest także izolacja sygnału zegara. W przypadku stosowania przetwornika analogowo-cyfrowego o rozdzielczości 20 bitów, przy częstotliwości próbkowania 1 MHz, np. takiego jak LTC2378-20, można uzyskać stosunek sygnału do szumu (SNR) na poziomie 104 dB. Aby jednak osiągnąć tak wysokie parametry, wymagany jest zegar praktycznie bez jittera. Do izolacji sygnału zegarowego nie należy jednak używać standardowego izolatora, takiego jak ADuM14x. Dodaje on bowiem do zegara jitter, co znacząco ogranicza sprawność przetwornika ADC.

Więcej szczegółów na temat wymagań dotyczących jittera w aplikacjach przetworników ADC można znaleźć w nocie projektowej DN1013.

Rysunek 7 pokazuje teoretyczną granicę SNR w stosunku do częstotliwości dla różnych wartości jittera zegara. Wysokiej jakości przetworniki analogowo-cyfrowe, takie jak LTC2378, cechują się jitterem apertury (własnym) na poziomie 4 ps, co daje teoretyczną granicę 106 dB w paśmie do 200 kHz.

Rysunek 7. Wpływ jittera zegara na wydajność przetwornika ADC

Rysunek 7. Wpływ jittera zegara na wydajność przetwornika ADC

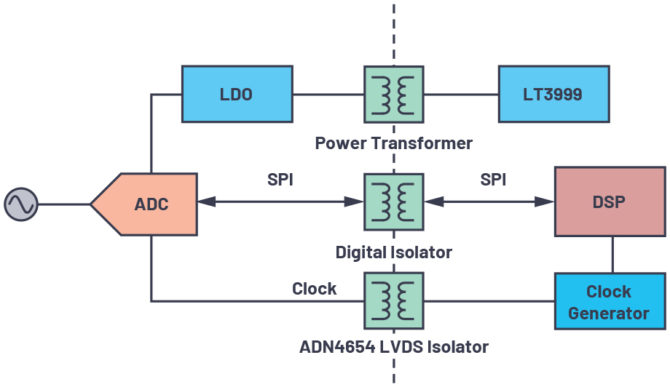

Tradycyjną koncepcję separacji sygnałów zegarowych przedstawiono na rysunku 8. Taki układ może zawierać:

- Standardowy, dobrej klasy izolator cyfrowy, taki jak ADuM250N wprowadza jitter na poziomie 70 ps rms. W celu uzyskania SNR na poziomie 100 dB, trzeba ograniczyć pasmo do 20 kHz.

- Izolator zoptymalizowany dla sygnałów zegarowych, np. LTM2893, który wprowadza jitter na poziomie jedynie 30 ps rms (max). Można wtedy uzyskać SNR rzędu 100 dB przy szerszym paśmie, do 50 kHz.

Rysunek 8. Izolacja zegara przy użyciu rozwiązania standardowego

Przy wyższych częstotliwościach należy stosować izolatory LVDS. Przykładowo, układ ADN4654 wprowadza jitter na poziomie jedynie 2,6 ps, co pozwala na zbliżenie się do maksymalnych możliwych osiągów przetwornika ADC. Tak niski jitter pozwala na osiągnięcie SNR rzędu 110 dB przy paśmie 100 kHz.

Rysunek 9. Izolacja zegara przy użyciu izolatora LVDS

Rysunek 9. Izolacja zegara przy użyciu izolatora LVDS

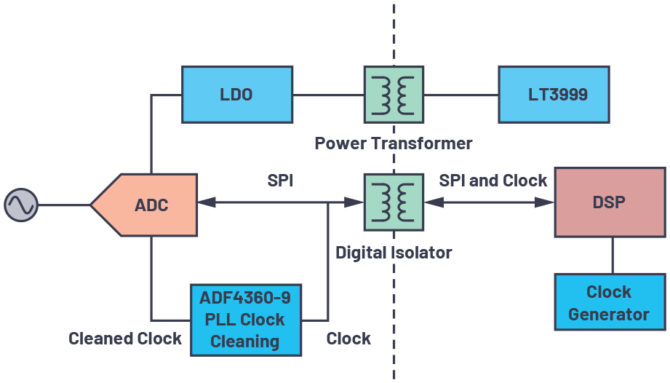

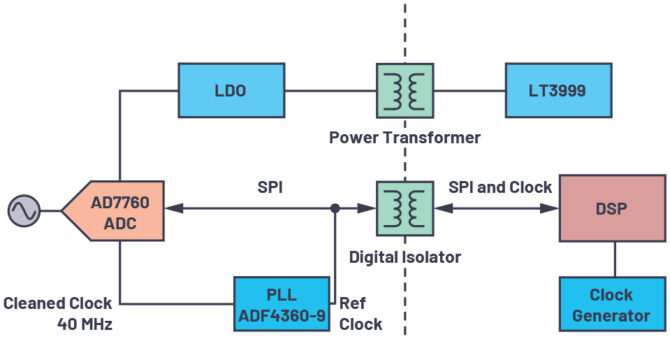

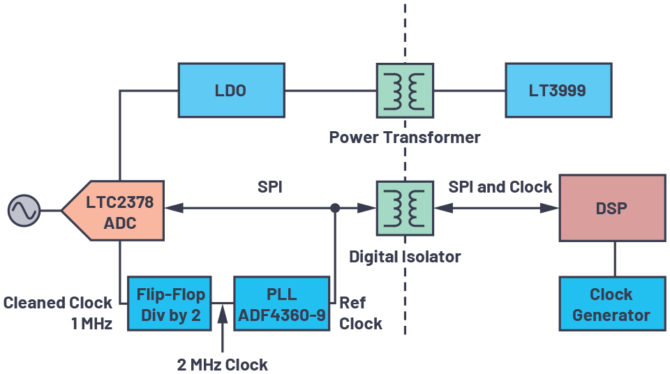

Rysunek 10 przedstawia użycie pętli PLL do regeneracji zegara. W roli pętli PLL można użyć układu ADF4360-9.

Rysunek 10. Izolacja przy użyciu dodatkowej pętli PLL do regeneracji zegara

Rysunek 10. Izolacja przy użyciu dodatkowej pętli PLL do regeneracji zegara

Rysunek 11. ADF4360-9 używany do regeneracji zegara

Rysunek 11. ADF4360-9 używany do regeneracji zegara

Zastosowany generator ADF4360-9 jest w stanie produkować sygnał o minimalnej częstotliwości 1,1 MHz. Nie może więc bezpośrednio taktować przetwornika LTC2378, wymagającego taktowania maksymalnie 1 MHz. W takim wypadku pomocny jest przerzutnik o niskim poziomie jittera, pracujący jako dzielnik częstotliwości przez 2.

Rysunek 12. Przerzutnik służący do obniżenia taktowania dla LTC2378

Rysunek 12. Przerzutnik służący do obniżenia taktowania dla LTC2378

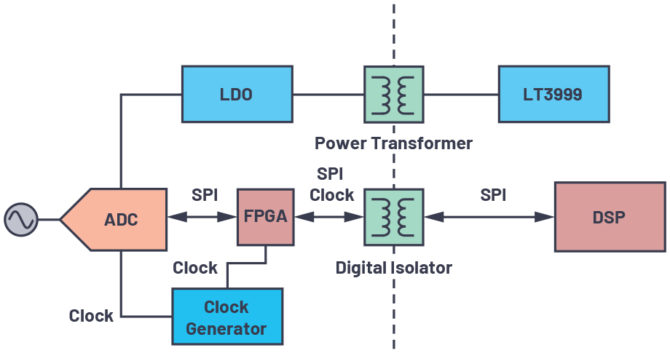

Kolejną możliwością uzyskania zegara o wymaganej charakterystyce jittera jest lokalne generowanie sygnału. Komplikuje to jednak architekturę rozwiązania, ponieważ wprowadza do systemu asynchroniczne domeny zegarowe. Jeśli więc potrzebujemy dwóch oddzielnych, izolowanych przetworników ADC, ich zegary mogą się różnić częstotliwością bezwzględną, co oznacza konieczność dodania do projektu układu konwertera częstotliwości próbkowania. Niektóre szczegóły dotyczące konwersji częstotliwości można znaleźć w nocie EE-268.

Rysunek 13. Generowanie taktowania po stronie izolowanej (gorącej)

Rysunek 13. Generowanie taktowania po stronie izolowanej (gorącej)

Sygnał zegarowy dla przetworników ADC sigma-delta

Podobne problemy z zegarami dotyczą również przetworników ADC typu sigma-delta, takich jak AD7760. W tej sytuacji ważne jest doprowadzenie do układu zegara nadpróbkowania o możliwie najmniejszym jitterze, np. o częstotliwości 40 MHz. Dla takiej częstotliwości nie są wymagane żadne dodatkowe dzielniki.

Podsumowanie

Izolacja galwaniczna aplikacji z wysokiej klasy przetwornikami analogowo-cyfrowymi wymaga przemyślanego projektu i zastosowania różnych technik. Pod pewnymi warunkami można jednak osiągnąć bardzo dobrą jakość sygnału, np. stosunek sygnału do szumu ponad 100 dB. Szczególną uwagę należy poświęcić izolacji sygnału zegarowego, gdyż ma to kluczowy wpływ na dokładność systemu. Poza tym należy zwrócić baczną uwagę na izolację zasilania. Proste topologie przetwornic impulsowych, takie jak flyback, mogą spowodować problemy z kompatybilnością elektromagnetyczną.

Aby tego uniknąć można zastosować np. przetwornicę w topologii push-pull. Separacja sygnałów danych również jest ważna, ale standardowe rozwiązania są tu wystarczająco dobre i nie wywierają zbyt dużego wpływu na ogólną jakość systemu. Zastosowanie wszystkich trzech typów izolacji pozwala zaprojektować wydajne, izolowane galwanicznie rozwiązanie wykorzystujące przetwornik analogowo-cyfrowy.

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii