[RAQ] Czy jest możliwe wykonanie układu nadzorującego zasilanie pracującego od napięcia zerowego?

Pytanie:

Czy istnieją układy nadzorujące napięcie zasilania pracujące już od napięcia zerowego, czy jest to tylko koncepcja teoretyczna?

Odpowiedź:

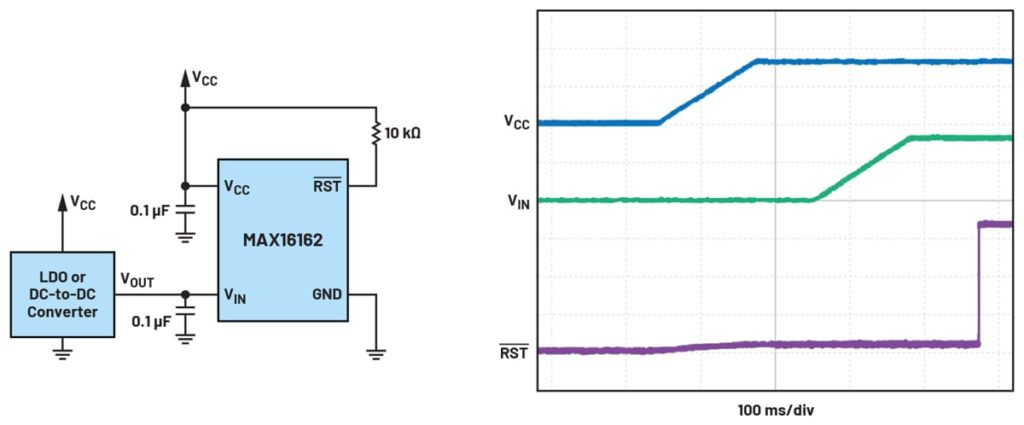

Tak, takie układy naprawdę istnieją. Przykładami takich konstrukcji są MAX16161/MAX16162, które są w stanie wygenerować sygnał resetu nawet przy zupełnym braku zasilania. Pozwala to na monitorowanie zasilania nawet o napięciu poniżej 1 V.

Układ monitorujący zasilanie to prosty obwód generujący sygnał reset przy obniżeniu napięcia poniżej pewnego ustalonego progu. Jest to przydatne w stanach awaryjnych lub przy uruchamianiu zasilania, gdyż zapobiega powstawaniu w układzie niepożądanych stanów nieustalonych.

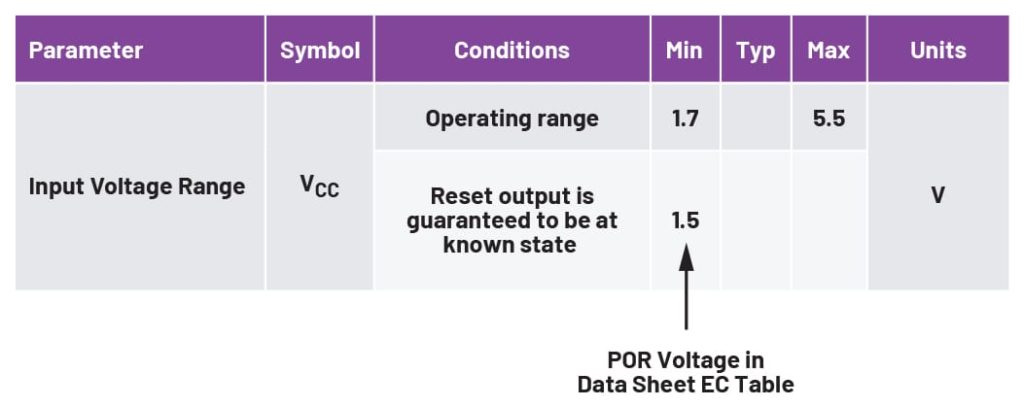

Solidny monitor zasilania jest często konieczny w systemach elektronicznych, gdyż poprawia on niezawodność systemu i jego pracę przy skokach napięcia i awariach. Producenci ciągle usprawniają tego typu obwody. Jednak nadal większość monitorów do poprawnego wygenerowania sygnału resetu potrzebuje pewnego minimalnego napięcia (power-on reset voltage, VPOR). Zanim linia zasilania osiągnie takie napięcie, stan sygnału resetu jest nieokreślony, co może powodować problemy z ponownym uruchomieniem systemu.

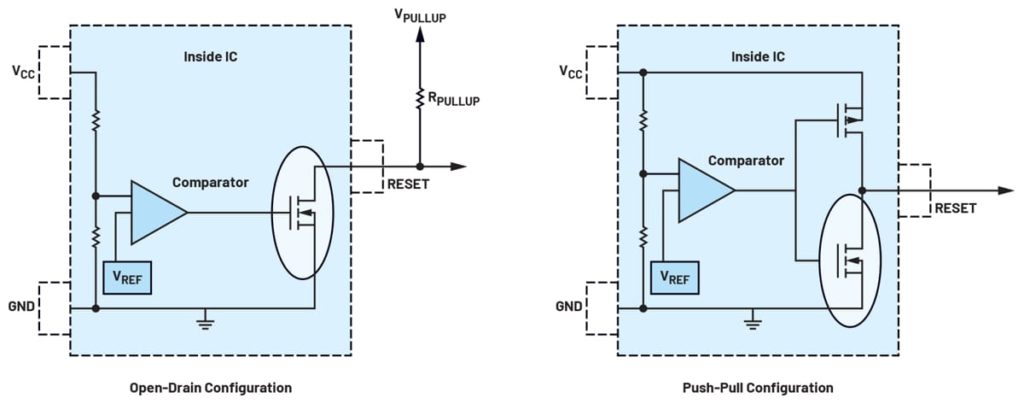

Do obsługi sygnału RESET najczęściej stosowane są dwie topologie wyjścia: wyjście z otwartym drenem oraz push-pull. Obie w roli tranzystora ściągającego do masy wykorzystują element NMOS MOSFET.

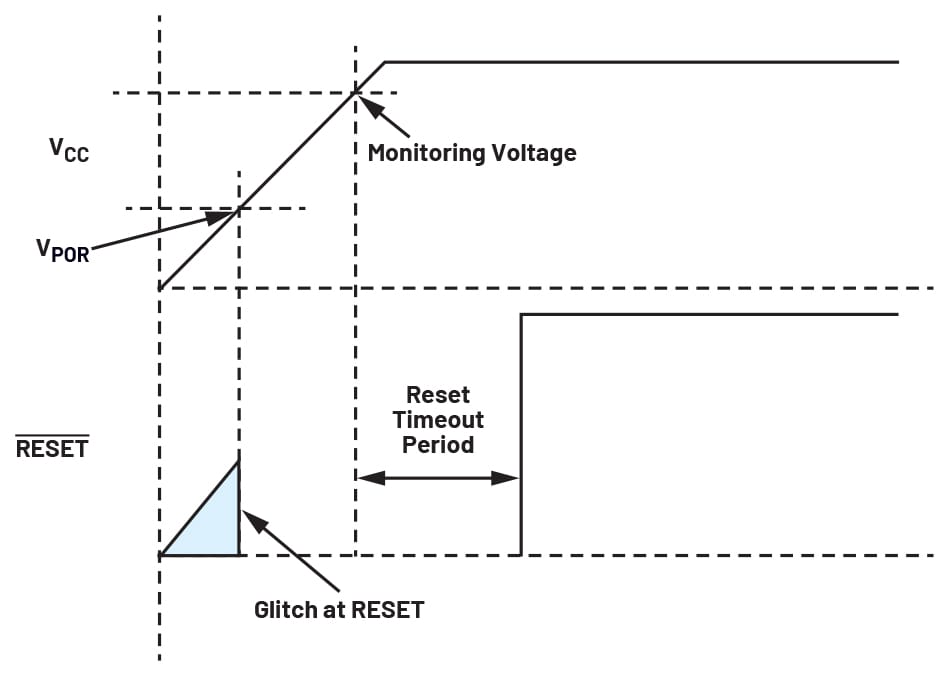

Podczas uruchamiania zasilania, gdy napięcie jest jeszcze poniżej progu VPOR, w układzie nie ma wystarczająco wysokiego napięcia, żeby wysterować tranzystor wyjściowy. Oznacza to, że układ nie kontroluje napięcia na linii reset. Napięcie na tej linii rośnie proporcjonalnie do napięcia, do którego podciągany jest sygnał (VPULLUP) i dopiero po przekroczeniu progu VPOR wewnętrzny MOSFET jest w stanie ściągnąć sygnał do prawidłowego napięcia, tj. zazwyczaj do masy.

Rys. 1. Wyjście RESET w konfiguracjach otwartego drenu i push-pull

Rys. 2. Napięcie VPOR w przykładowej dokumentacji układu monitora

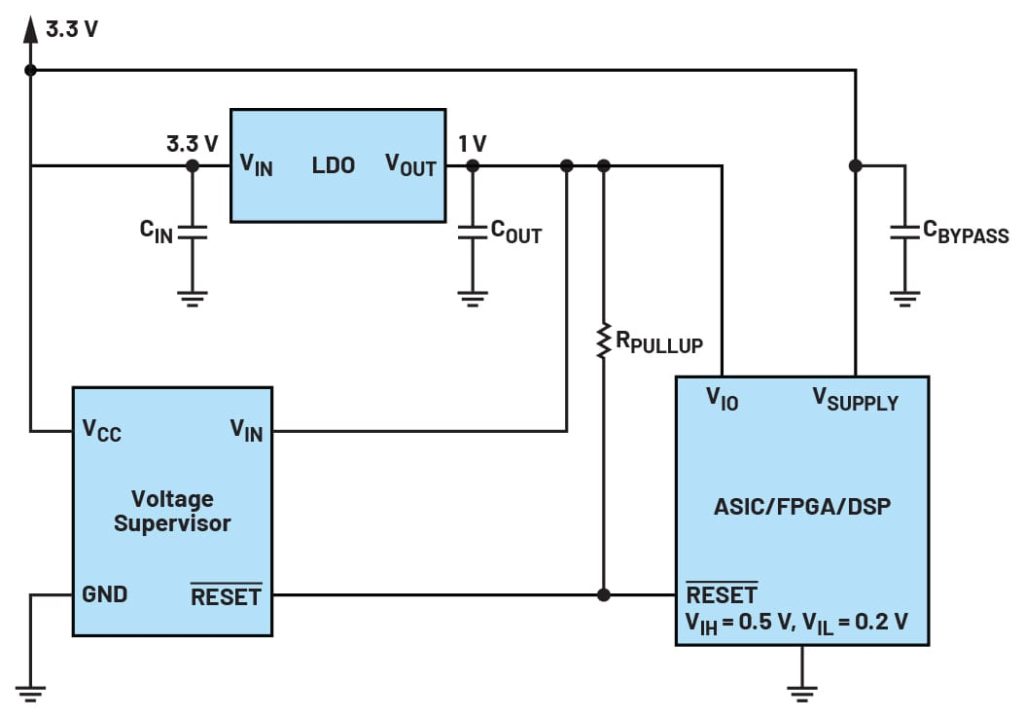

Układy monitorowania zasilania można też używać do pomiaru napięcia układów FPGA, ASIC, czy procesorów DSP, gdzie napięcia zasilania mogą wynosić nawet poniżej 1 V. Dodatkowo, w niskonapięciowych procesorach układy wejść/wyjść są bardzo wrażliwe na zmiany poziomów logicznych, a stan wysoki może być wykrywany nawet od napięcia 0,5 V (por. rysunek 3).

Podczas uruchamiania układ FPGA, ASIC lub DSP musi być w stanie resetu do momentu stabilizacji napięcia na wszystkich szynach zasilania. W momencie, gdy sygnał RESET jest niestabilny, a więc gdy napięcie zasilania jest poniżej progu, może to wprowadzić układ w stan nieustalony. Dopiero, gdy próg VPOR zostanie przekroczony, wyjście jest przełączane w stan RESET i układ jest prawidłowo resetowany.

Rys. 3. Połączenie monitora z niskonapięciowym układem ASIC/FPGA/DSP

Rys. 4. Sygnały zasilania przy nieokreślonym stanie pinu RESET

Podczas, gdy branża elektroniki wyraźnie zmierza ku coraz niższym napięciom układów półprzewodnikowych, producenci również pracują nad zminimalizowaniem efektu niestabilności sygnału reset w monitorach napięcia. Korzystając z tradycyjnych rozwiązań można jedynie obniżać napięcie VPOR, ale całkowita eliminacja efektu wymaga przyjęcia całkowicie nowego podejścia.

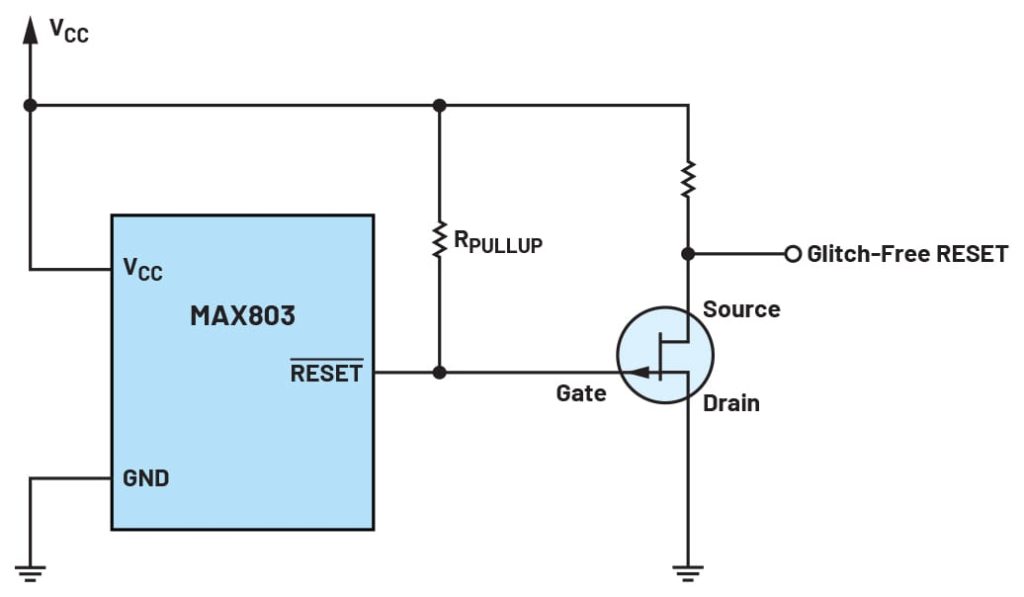

Aktualnie inżynierowie systemów korzystają z tradycyjnego monitora w połączeniu z zewnętrznym obwodem, co ma symulować funkcję uruchamiania resetu przy zerowym napięciu, (tzw. „glitch-free”, co można też tłumaczyć jako bezzwłocznie). Po dodaniu tranzystora JFET w układzie wtórnika źródłowego wyjście układu będzie odbiciem wyjścia układu monitora (czyli bramki JFET-a) minus napięcie progowe tranzystora. To powoduje ok. 1 V spadku napięcia pomiędzy bramką tranzystora i wyjściem, co eliminuje potencjalny wzrost napięcia na linii RESET przed uruchomieniem reszty obwodów.

Rys. 5. Tradycyjny monitor z dołączonym zewnętrznym tranzystorem JFET typu P eliminującym niepożądany wzrost napięcia na linii

Prawdziwe układy „glitch-free” działają w ten sposób, że wyciągają prąd z linii RESET, co wymusza potencjał zerowy nawet przy zasilaniu 0 V. Przykład takiego układu oraz jego pracy widzimy na rysunku 6. Układy MAX16161/MAX16162 nie wymagają w dodatku żadnych zewnętrznych elementów, co sprawia, że są niewielkie i stosunkowo niedrogie.

Podsumowanie

Układy nadzorujące napięcie pracujące przy napięciu zero nie są już tylko koncepcją teoretyczną. Projektanci mają już do dyspozycji stabilnie pracujące układy generujące sygnał resetu nawet przy bardzo niskim napięciu, co pozwala korzystać z nich przy szynach zasilania nawet poniżej 1 V. Przykładami takich konstrukcji są MAX16161/MAX16162 – niewielkie, energooszczędne układy scalone, które pobierają prąd spoczynkowy jedynie 825 nA. Pomaga to dodatkowo zwiększyć czas pracy systemu na baterii.

Rys. 6. Schemat aplikacyjny układu MAX16162 oraz wykresy sygnałów w układzie

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii  Mieszacze aktywne – ćwiczenie z serii ADALM

Mieszacze aktywne – ćwiczenie z serii ADALM