Projektowanie płytek drukowanych o wysokiej wierności dla wielokanałowych układów formowania wiązki — część 2: Izolacja

W części 2 artykułu przeanalizowano wpływ izolacji linii transmisyjnych na wydajność układów scalonych formujących wiązkę, a także omówiono wybór odpowiedniej topologii linii transmisyjnej dla danego wymagania izolacji.

Wprowadzenie

Dobra izolacja między kanałami ma kluczowe znaczenie dla utrzymania wydajności układów scalonych formujących wiązkę (BFIC). Redukcja wytłumienia i listków bocznych w zastosowaniach związanych z matrycami fazowanymi wiąże się z koniecznością ustawienia wzmocnienia międzykanałowego. Różnice rzędu 30 decybeli nie są tu niczym niezwykłym. Jak pokazano w części 1, chipy nowoczesnych układów BFIC mają zazwyczaj wiele równoległych ścieżek RF, które są prowadzone do pinów rozmieszczonych na tej samej krawędzi i/lub w tym samym rogu obudowy. Często spotykamy rozwiązania, w których wszystkie wejścia (lub wyjścia) są rozmieszczone również na tej samej krawędzi. W rezultacie wyzwaniem jest poprowadzenie wielu linii RF do i z tych blisko rozmieszczonych pinów na płytkach drukowanych (PCB) przy zachowaniu wystarczającej izolacji między liniami.

W tej części omówiono wpływ stopnia izolacji między liniami transmisyjnymi na wydajność układów BFIC, ogólne wytyczne dotyczące wyboru najlepszej topologii linii transmisyjnej w oparciu o wymagania aplikacji w zakresie izolacji i geometrii układów BFIC. Będzie też mowa o tym, jak najlepiej rozmieścić linie transmisyjne w pobliżu układu BFIC. Jednostką wymiarów podawanych w artykule są milsy (1000 milsów odpowiada 1 calowi). Aby przeliczyć wymiar w milsach na milimetry, należy pomnożyć go przez 0,0254.

Izolacja: między liniami transmisyjnymi

Dwie sąsiednie lnie transmisyjne znajdujące się na jednej płytce drukowanej będą charakteryzowały się pewnym wzajemnym sprzężeniem elektrycznym i/lub sprzężeniem przez pole elektryczne i magnetyczne (EM). Skutkuje to skończoną wartością izolacji. W praktyce spotykamy wiec duże różnice wydajności izolacji między topologiami linii omówionymi w części 1. Linie umieszczone na górnej warstwie mają zazwyczaj gorszą izolację niż linie zagrzebane ze względu na sprzężenie za pośrednictwem pola. Poza wybraną topologią linii, dominującymi czynnikami wpływającymi na izolację jest częstotliwość robocza, odległość między liniami oraz długość równoległego trasowania linii. Ponadto, aby w przypadku stosowania topologii zagrzebanej, takiej jak linia paskowa, zachować dobrą izolację, wszelkie przejścia do warstwy górnej muszą być zaprojektowane bardzo starannie.

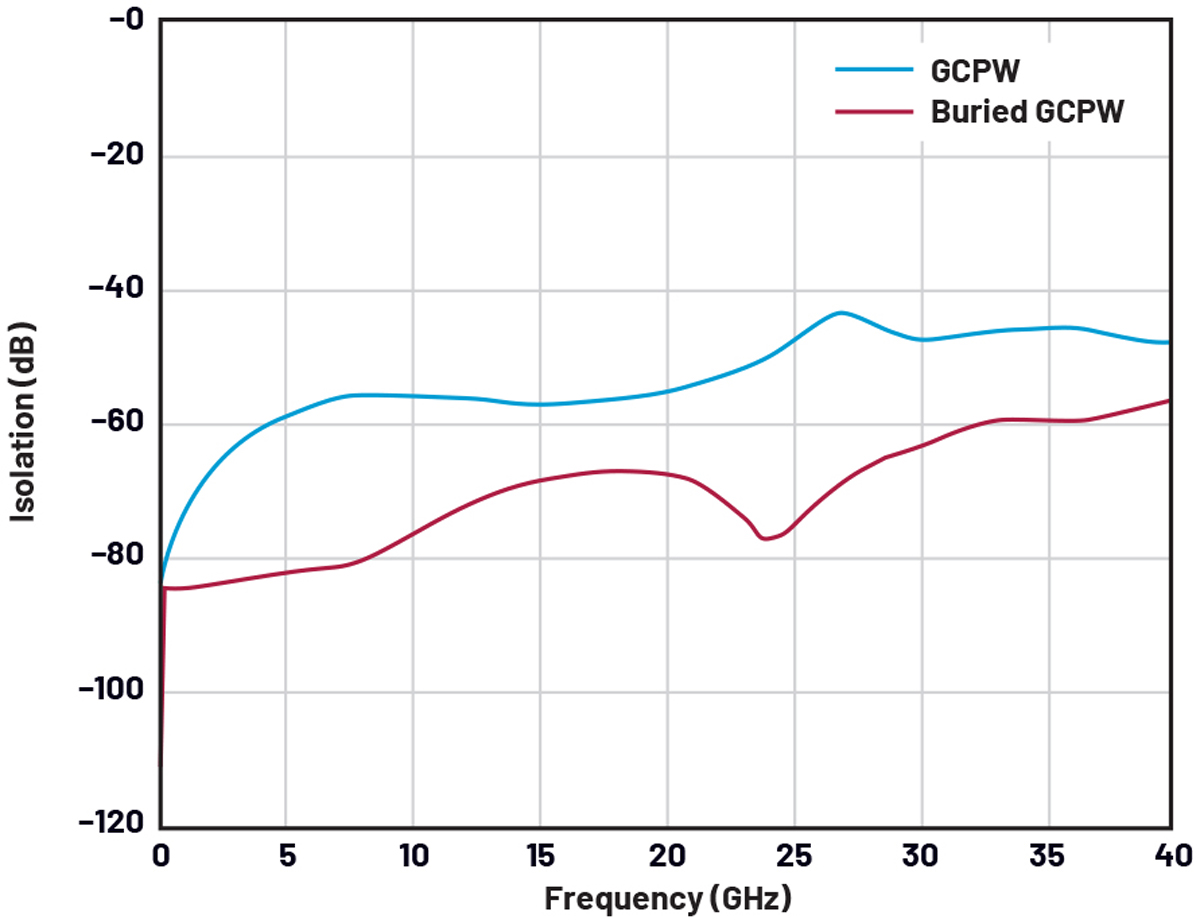

Na rysunku 1 przedstawiono symulację Keysight RFPro EM izolacji w funkcji częstotliwości dla dwóch par topologii linii transmisyjnych: uziemionego falowodu współpłaszczyznowego (GCPW) i zagrzebanego GCPW. Odległość między środkami każdej pary linii transmisyjnych została ustawiona na 60 milsów, a długość linii prowadzonych równolegle na 200 milsów. Do odgrodzenia każdej linii po obu stronach zastosowano przelotki uziemiające o średnicy 6 milsów, rozmieszczone w odległości 25 milsów od środka do środka. GCPW ma gorszą symulowaną izolację niż zagrzebany falowód GCPW. Oczywiście w przypadku, gdy izolacja ma kluczowe znaczenie, należy wybrać topologię zagrzebaną.

Rys. 1. Symulowana izolacja GCPW i zagrzebanego GCPW

GCPW versus zagrzebane GCPW: jaka różnica może wynikać z izolacji 15 dB

Słaba izolacja między liniami transmisyjnymi na płytce drukowanej może być szczególnie problematyczna w zastosowaniach, w których w poszczególnych ścieżkach występuje duża różnica między poziomami sygnałów. Jeśli w systemie z matrycą fazowaną dwa sąsiednie bloki o zmiennej amplitudzie i fazie (VAP) działają z minimalnym i maksymalnym tłumieniem, pasożytnicze sprzężenie sygnału pogorszy liniowość funkcji regulacji wzmocnienia VAP w ścieżce o większym tłumieniu. Zachowanie to zaobserwowano w układzie ADAR3001, 4-wejściowym, 4-wyjściowym BFIC (podobnym do pokazanego na rysunku 1 w części 1 artykułu), na płytce drukowanej z liniami transmisyjnymi GCPW. Płytka PCB została przeprojektowana z zastosowaniem zagrzebanych GCPW w celu zwiększenia izolacji między liniami.

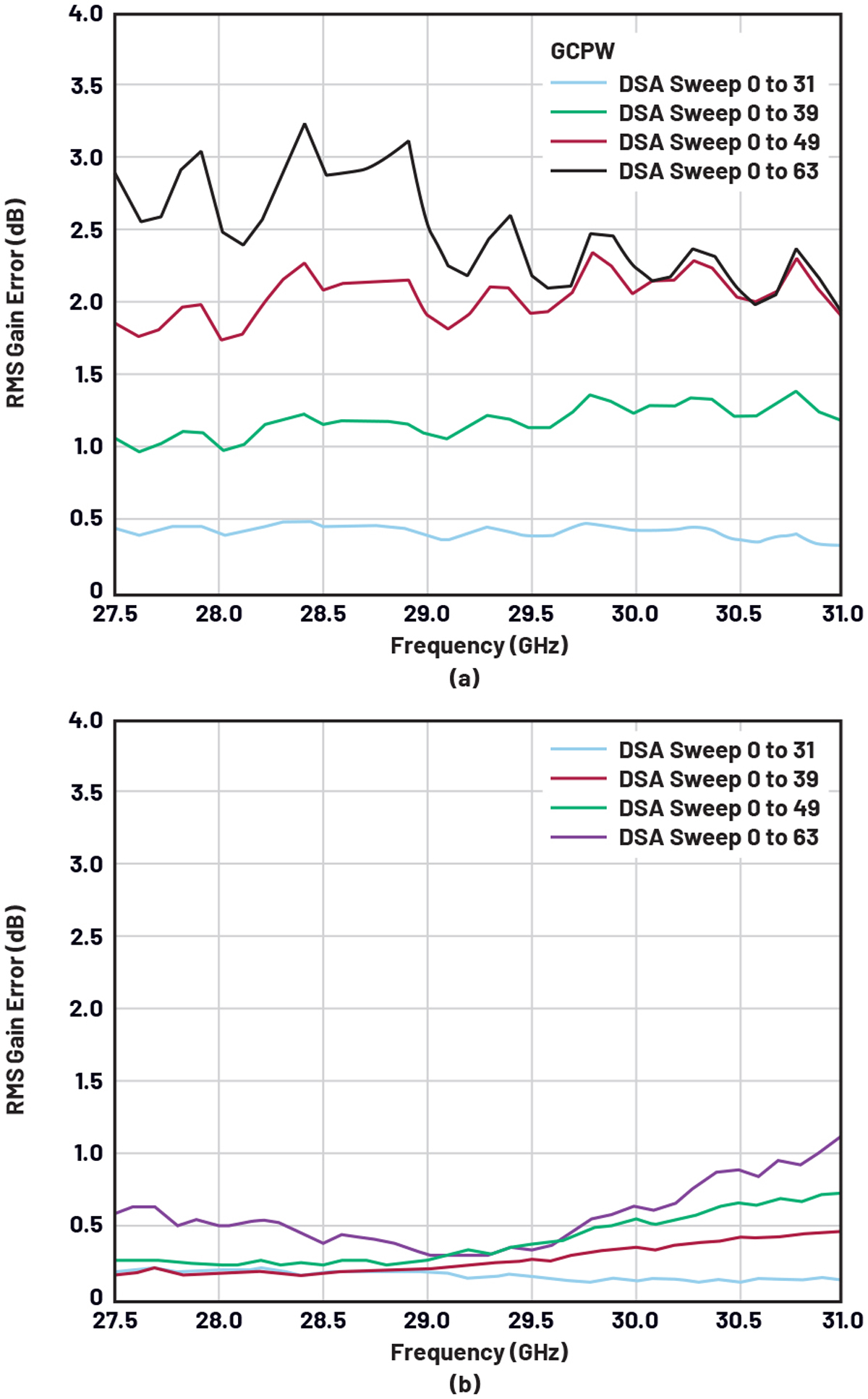

Błąd wzmocnienia RMS jest abstrakcyjną wartością charakterystyczną, która jest wskaźnikiem nieliniowości regulacji wzmocnienia. W tym przypadku błąd wzmocnienia RMS został zmierzony dla obu wersji płytki drukowanej. Na rysunku 2a pokazano błąd wzmocnienia RMS oryginalnej płytki drukowanej z GCPW, natomiast na rysunku 2b pokazany jest błąd wzmocnienia RMS przeprojektowanej płytki drukowanej z zagrzebanym GCPW. Na rysunku 2a błąd wzmocnienia RMS jest znacznie większy, gdy cyfrowy tłumik krokowy (DSA) VAP jest sprawdzany w całym zakresie. Jest to zjawisko oczekiwane, ponieważ aplikacja jest najbardziej podatna na słabą izolację, gdy różnica między tłumieniami DSA jest największa.

Wyższa izolacja między liniami w zagrzebanym GCPW znacznie poprawiła błędy wzmocnienia RMS. Jest to zgodne z symulacjami i odzwierciedla rzeczywiste wydajność układu BFIC. Wyniki te pokazują, że nawet umiarkowana poprawa izolacji o 15 dB może mieć przy 30 GHz ogromny wpływ na zmierzoną wydajność.

Rys. 2. Błędy RMS układu BFIC na płytce drukowanej z: a) liniami GCPW w porównaniu z płytką drukowaną z b) zagrzebanymi liniami GCPW

Izolacja dwóch równoległych linii paskowych

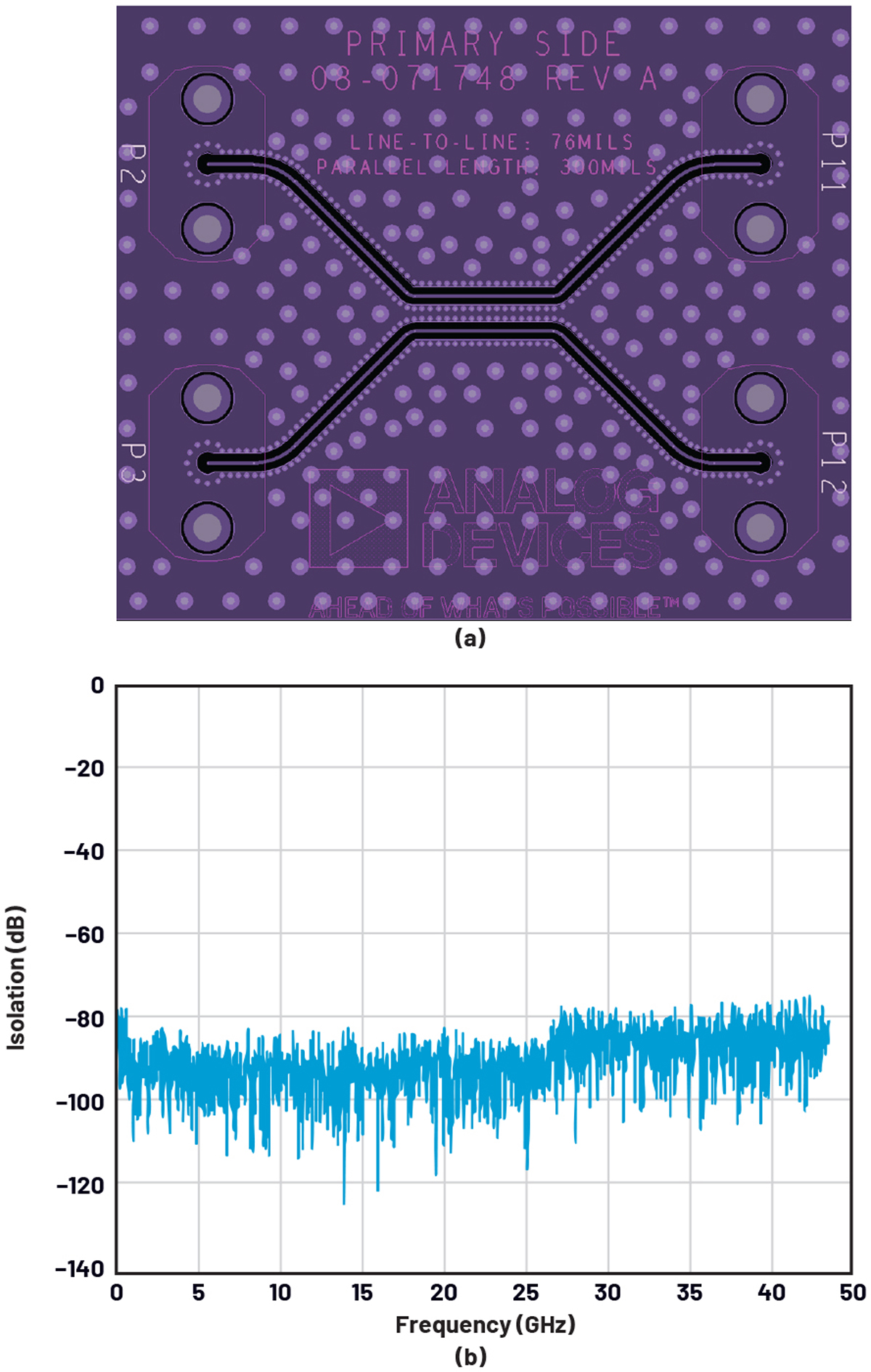

Ogólnie przyjmuje się, że topologia linii paskowej zapewnia najlepszą izolację spośród wymienionych topologii. Aby zweryfikować to założenie, wykonano płytkę eksperymentalną, pozwalającą sprawdzić, jak będzie się zmieniała izolacja w funkcji częstotliwości przy użyciu topologii linii paskowej. Zastosowano projekt linii paskowej o szerokości 8 milsów, poprowadzonej na warstwie 2 z 8-milsowymi dielektrykami Rogers 4003C (warstwa 1 do warstwy 2) i 8-milsowym 4450T (warstwa 2 do warstwy 3). Odległość między środkami pary linii wynosiła 76 mil, a długość równoległego odcinka to 300 milsów. Odległości te zostały wybrane w celu przybliżonego odwzorowania średniego rozstawu między pinami RF wielu układów BFIC oraz późniejszego przebiegu linii przed rozgałęzieniem do złączy koncentrycznych lub innych elementów. Każda linia miała własne ogrodzenie z przelotek o średnicy 10 milsów i rozstawie 18 milsów między środkami. Na rysunku 3a pokazano układ linii paskowej na warstwie 2 (nie pokazano płaszczyzn uziemienia warstwy 1 i warstwy 3, które otaczają linię paskową po obu stronach dielektryków Rogers). Wynik pomiaru izolacji przedstawiono na rysunku 3b i wyraźnie dowodzi on, że nieprzerwana linia paskowa z ciasnym ogrodzeniem przelotek zapewnia optymalną wydajność i powinna być stosowana tam, gdzie wymagania dotyczące izolacji są bardzo wysokie. Podczas projektowania przelotek należy zwrócić szczególną uwagę przy przechodzeniu do górnej warstwy w celu połączenia z elementami.

Rys. 3. Layout płytki eksperymentalnej z linią paskową (widoczna warstwa 2) oraz b) wyniki pomiaru izolacji płytki

Wykres izolacji jest zaszumiony, ponieważ izolacja pary linii jest na granicy możliwości pomiarowych wektorowego analizatora sieci (VNA). Średnia izolacja dla wszystkich częstotliwości jest lepsza niż –80 dB. Spadek izolacji występujący przy około 26 GHz wynika z działania analizatora VNA.

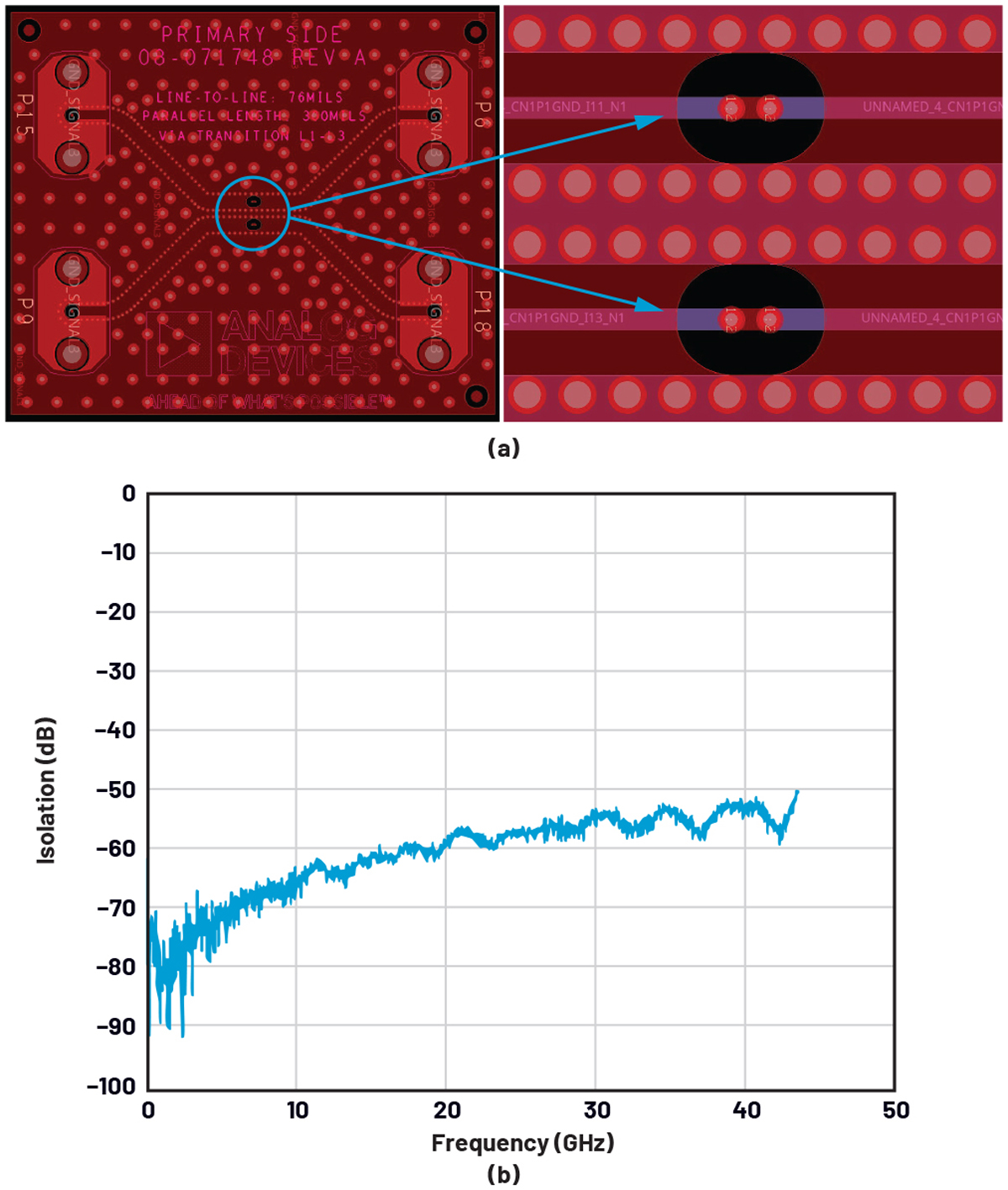

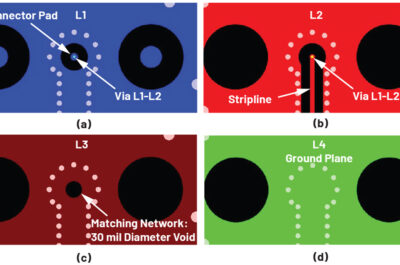

Izolacja dwóch równoległych linii paskowych z przelotkami back-to-back L1–L2

Na tej samej płytce eksperymentalnej, przedstawionej wyżej, zaprojektowano kolejną parę linii paskowych o takich samych atrybutach jak poprzednio (geometria linii, rozmieszczenie przelotek, odstępy między liniami i długość przebiegu równoległego), ale do każdej linii dodano parę przelotek przejściowych (lub przelotki typu back-to-back między warstwą 1 a warstwą 2). Zabieg ten miał na celu sprawdzenie, w jakim stopniu pogarsza się izolacja podczas przejścia do warstwy górnej, jak pokazano po lewej stronie na rysunku 4a. W górnej warstwie utrzymano trasowanie na krótkim, 14-milsowym odcinku między środkami przelotek. W powiększeniu pokazano to po prawej stronie rysunku 4a.

Izolację zmierzono na tych liniach paskowych z przelotkami przejściowymi typu back-to-back (przelotki między warstwą 1 a warstwą 2) i stwierdzono jej pogorszenie w porównaniu z liniami bez przelotek przejściowych, co pokazano na rysunku 4b. Eksperyment ten podkreśla znaczenie starannego projektowania przejść przy przechodzeniu do wyższej warstwy w celu łączenia elementów.

Rys. 4. a) Layout płytki eksperymentalnej z parą linii paskowych z przelotkami przejściowymi umieszczonymi tyłem do siebie – widok z daleka (po lewej) i zbliżenie (po prawej), b) zmierzona izolacja płytki eksperymentalnej z przelotkami przejściowymi

Wskazówki dotyczące trasowania wielu wejść/wyjść RF

Wiele układów scalonych, w szczególności formujących wiązki RF, charakteryzuje się dużą liczbę wejść/wyjść RF. Utrudnia to wyprowadzanie od nich ścieżek przy zachowaniu dobrej wydajności RF. Oprócz starannego doboru i zaprojektowania topologii linii transmisyjnej, kluczem do utrzymania wydajności RF, a w szczególności izolacji, jest prawidłowe uziemienie poprzez zastosowanie ogrodzenia przelotkami aż do samego układu.

Którą linię transmisyjną zastosować

Decyzja o wyborze linii transmisyjnej powinna opierać się przede wszystkim na wymaganiach dotyczących izolacji oraz geometrii układu BFIC. Na przykład, jeśli izolacja musi wynosić tylko około -40 dB, można bezpiecznie zastosować linię transmisyjną GCPW. Jeśli izolacja musi wynosić około –65 dB, konieczne jest zastosowanie linii paskowej. Następnie należy rozważyć geometrię układu BFIC, przede wszystkim rozmiar każdego pinu, odstęp między pinami oraz odległość między pinami RF. Na przykład, jeśli układ BFIC ma obudowę BGA o średnicy kulki lutowniczej 5,5 milsów/0,22 mm, odstęp między pinami 10 milsów/0,4 mm oraz odległości 30 milsów/1,2 mm między najbliższymi pinami RF, a wymagana jest izolacja –65 dB lub lepsza, geometria BFIC mogłaby obsługiwać symetryczną linię paskową o przybliżonych wymiarach: szerokość linii 6 milsów, dielektryk o grubości 6 milsów (powyżej i poniżej linii) oraz 10-milsowa odległość boczna od masy, przy założeniu stałej dielektrycznej o wartości ok. 3. Ogólna zasada dotycząca linii paskowej mówi, że boczna odległość od masy powinna być równa około dwukrotnej szerokości linii. Mniejsze odległości między pinami RF zaczynają wpływać na impedancję linii. Mniejsze odległości między pinami RF wymagałyby mniejszej szerokości, natomiast większa odległość między pinami RF pozwoliłaby na zastosowanie szerszej linii. Jak opisano w 1. części artykułu, to drugie rozwiązanie jest lepsze, ponieważ istnieje większa szansa na osiągnięcie 50 Ω podczas produkcji.

Trasowanie w pobliżu elementu

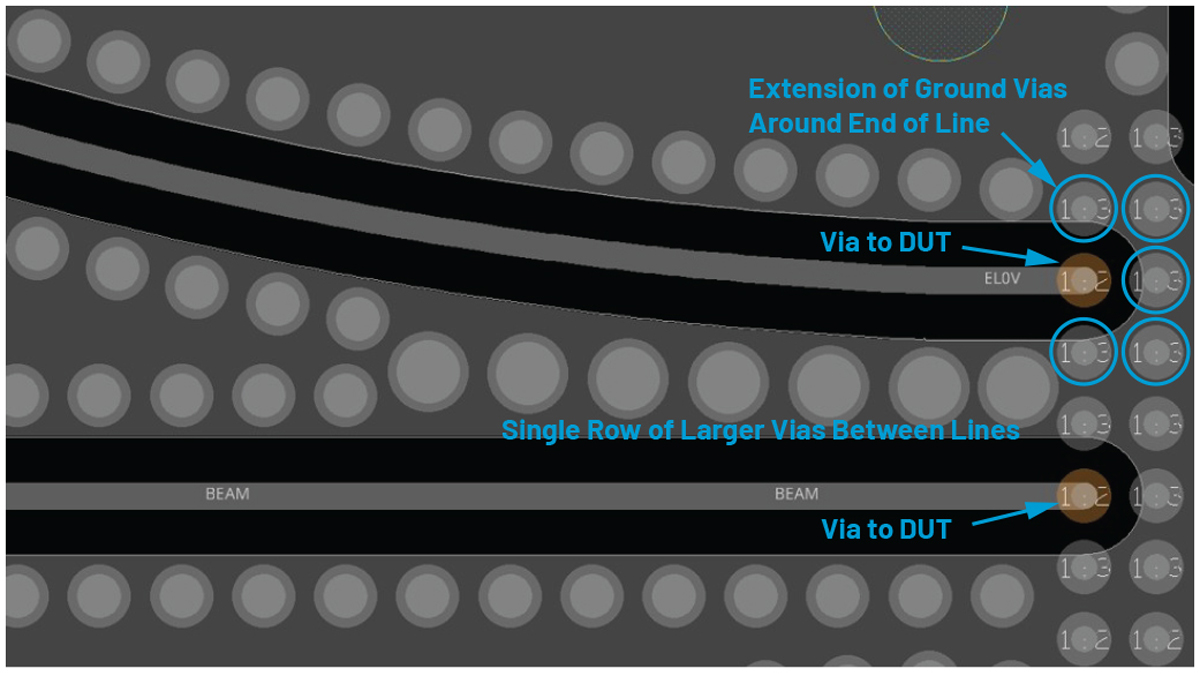

W przypadku stosowania linii paskowej należy zachować ostrożność podczas przejścia prowadzącego do pinu elementu umieszczonego na górnej warstwie, ponieważ jeśli nie zostaną zastosowane odpowiednie przelotki uziemiające, przejście to może znacznie pogorszyć izolację. Aby uzyskać najwyższą izolację, ściana uziemiająca przelotek powinna rozciągać się wokół końca linii paskowej w miejscu przejścia do elementu, jak pokazano na rysunku 5. Rozwiązanie takie pozwala wydłużyć krytyczną ścianę uziemiającą niezbędną do uzyskania najlepszej izolacji. Element powinien mieć również piny uziemiające, wypustki i/lub płytkę uziemiającą otaczające pin sygnałowy. Powinny ponadto z grubsza pokrywać się z wydłużonymi przelotkami uziemiającymi.

Rys. 5. Przelotki biegnące wokół linii transmisyjnej prowadzącej do układu i przechodzące do pojedynczego rzędu przelotek między liniami

Piny wejść/wyjść RF znajdujące się w niewielkiej odległości od siebie mogą nie zapewniać wystarczającej powierzchni do zachowania tego samego ogrodzenia przelotek dla każdej linii transmisyjnej na całej długości układu. W zależności od dostępnej powierzchni, typowe opcje ogrodzenia przelotek to:

- Użycie mniejszych przelotek, jeśli nie naruszają one zasad producenta dotyczących proporcji grubości dielektryka.

- Rozmieszczenie przelotek w układzie zygzakowatym w miejscach o ograniczonej powierzchni, o ile brak przelotki na jednej z linii połączenia układu nie pogorszy izolacji.

- Zastosowanie pojedynczego rzędu przelotek między liniami, przy zastosowaniu większego rozmiaru przelotek i zachowaniu takiej samej odległości między krawędziami otworów przelotek. W przypadku mniejszych przelotek pozwala to zachować odpowiednią izolację (rys. 5).

- Zastosowanie pojedynczego rzędu przelotek między liniami, używając przelotek o tym samym rozmiarze, gdy przestrzeń między liniami jest bardzo ograniczona.

Decyzja o tym, kiedy i jak przeprowadzić rozgałęzienie, zależy w dużej mierze od wzajemnego położenia pinów wejścia/wyjścia RF w układzie.

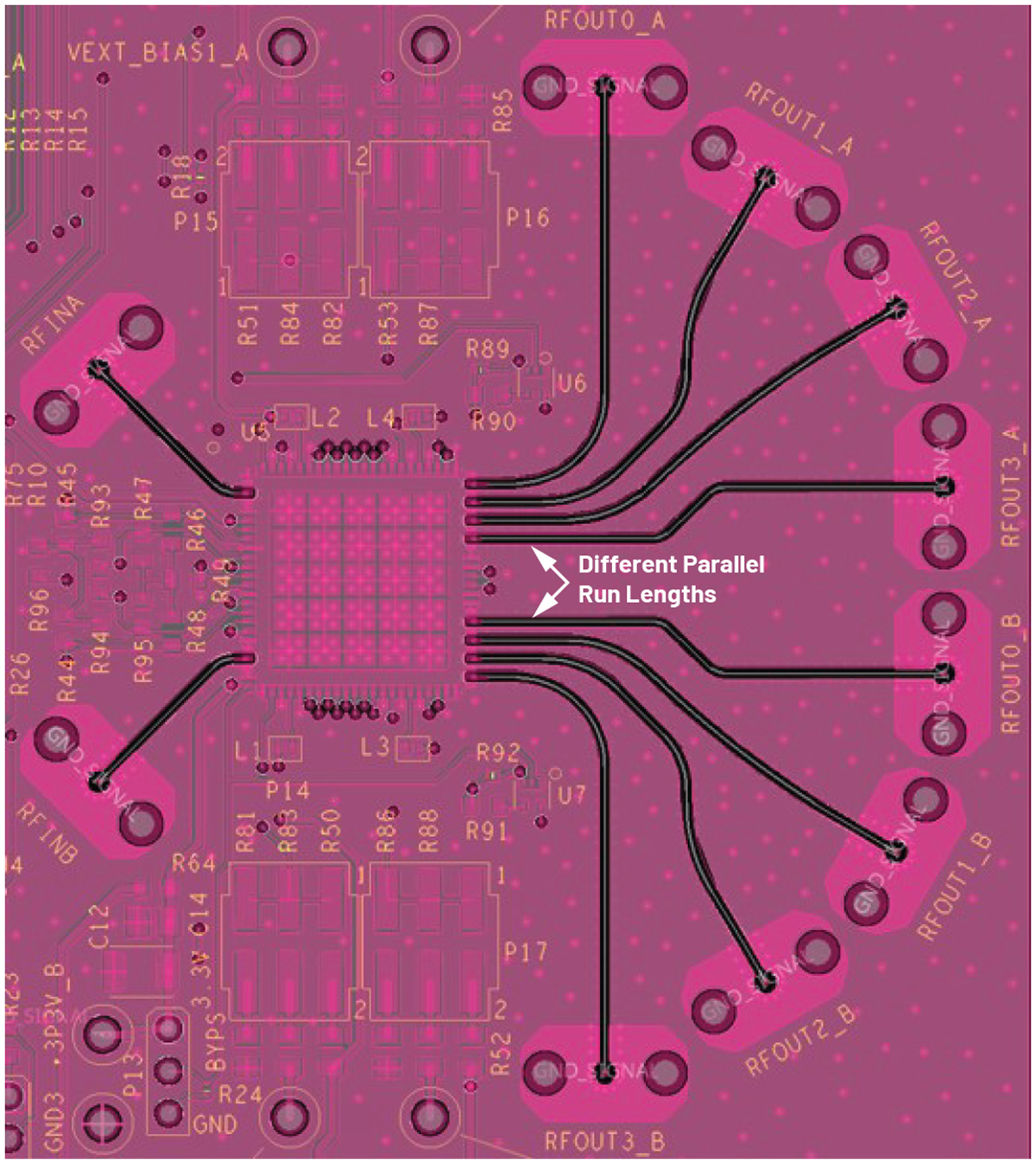

Ogólna zasada mówi, że rozgałęzienie powinno nastąpić tak szybko, jak to możliwe, aby zredukować równoległe przebiegi i tym samym utrzymać izolację na jak najwyższym poziomie. Jak widać na rysunku 5, rozgałęzienie może nastąpić natychmiast, ponieważ względne położenie pokazanych pinów wejść/wyjść RF (oraz pinów, które nie są pokazane). Jednak na rysunku 6 pokazano rozgałęzienie elementu 2-kanałowego z 8 wyjściami, w którym każdy kanał ma jako stopień wyjściowy przełącznik 1:4, który steruje czterema liniami transmisyjnymi o różnych długościach połączeń równoległych. W tym przypadku rozgałęzienie było również ograniczone przez trasowanie wejść/wyjść innych niż RF oraz powiązane obwody po północnej i południowej stronie układu, co ograniczało miejsce i sposób trasowania ośmiu linii transmisyjnych.

Rys. 6. Rozgałęzienie ośmiu wyjść RF z układu dwukanałowego

Wnioski

Pojawienie się wielokanałowych układów formujących wiązki wysokiej częstotliwości oraz innych układów scalonych RF sprawia, że projektowanie płytek drukowanych staje się coraz większym wyzwaniem zarówno pod względem dokładności linii transmisyjnych i przejść (omówione w części 1), jak i utrzymania wysokiej izolacji międzykanałowej niezbędnej do zachowania wydajności urządzenia (omówione w części 2). Projekty linii transmisyjnych RF przechodzą obecnie wymuszoną migrację od uziemionych falowodów koplanarnych na powierzchni do zagrzebanych linii paskowych. Ale nawet w przypadku projektów z zagrzebanymi liniami paskowymi, należy zachować ostrożność pozwalającą utrzymać izolację między sąsiednimi ścieżkami, stosując gęsto rozmieszczone przelotki, które całkowicie otaczają piny elementu. Ponadto, w utrzymaniu wysokiej izolacji pomocne jest szybkie rozgałęzienie ścieżek prowadzących do układu i położonych blisko siebie, które zapewnia ich odpowiednią separację.

Tłumaczenie i opracowanie: Jarosław Doliński

Projektowanie płytek drukowanych o wysokiej wierności dla wielokanałowych układów formowania wiązki — część 1: Straty odbiciowe

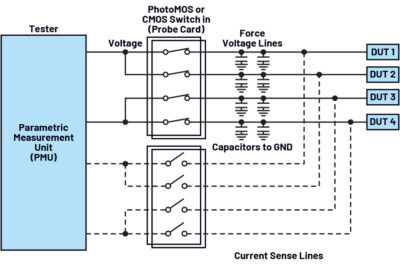

Projektowanie płytek drukowanych o wysokiej wierności dla wielokanałowych układów formowania wiązki — część 1: Straty odbiciowe  Wymiana przełączników PhotoMOS w automatycznych urządzeniach testujących

Wymiana przełączników PhotoMOS w automatycznych urządzeniach testujących  Global Electronics Association i Altium wprowadzają pierwsze wspólne certyfikaty w zakresie projektowania PCB

Global Electronics Association i Altium wprowadzają pierwsze wspólne certyfikaty w zakresie projektowania PCB