Seminarium Mentor Graphics – Wsparcie dla DDRx w HyperLynx

Mentor Graphics razem z firmą Gamma Sp. z o.o., autoryzowanym partnerem w Polsce organizuje bezpłatne seminarium poświęcone narzędziu do symulacji signal/power integrity – HyperLynx.

Formuła seminarium przewiduje prezentacje możliwości poszczególnych pakietów HyperLynx na konkretnych przykładach schematów czy layoutów – głownie pod kątem projektowania szybkich magistral do pamięci DDRx.

Organizatorzy zakładają, że każdy uczestnik po seminarium będzie w stanie samodzielnie przetestować omawiane przykłady analiz na własnych projektach, lub przykładach które udostępnimy po seminarium. W tym celu można otrzymać w pełni funkcjonalną miesięczną wersję HyperLynxa-a do testów jeszcze przed seminarium.

Bloki tematyczne seminarium:

-

Przegląd klasycznych metod analiz Signal Integrity z wykorzystaniem LineSim HyperLynx w kontekście DDRx

-

testowanie jakości sygnału w połączeniach pod kątem odbić i dystorsji na skutek nieciągłości impedancji ścieżki sygnałowej lub drodze powrotnej dla prądu.

-

optymalizacja jakości sygnału za pomocą funkcji – sweep parameters.

-

testowanie przesłuchów pomiędzy sąsiadującymi ścieżkami spowodowanych wzajemną pojemnością i indukcyjnością.

-

badanie emisji.

-

-

Zastosowanie BoardSim HyperLynx dla weryfikacji jakości połączeń gotowego layoutu (post layout) na przykładzie sygnałów magistrali adresowej DDRx:

-

analiza poszczególnych połączeń oraz eksport do LineSim w celu poszukiwania rozwiązania problemu.

-

analiza całościowa (batch analysis) w celu weryfikacji założonej jakości sygnałów oraz emisji dla wybranych klas połączeń lub całego pcb.

-

-

Analiza Post Layout z wykorzystaniem DDR Wizard;Wstęp do HyperLynx Power Integrity:

-

analiza AC Decoupling w kontekście wyboru prawidłowej strategii blokowania napięć zasilających;

-

oraz analiza DC Drop umozliwiająca wczesne wykrywanie problemów z dystrybucją napięć zasilania w obrębie testowanej pcb.

-

Seminarium odbędzie się 21 listopada 2013 r. w Warszawie (biurowiec Golden Floor Plaza w Warszawie przy Al. Jerozolimskich 123A). Osoby zainteresowane proszone są o rejestrację pod adresem. W razie wszelkich dodatkowych pytań odnośnie seminarium, można kontaktować się z firmą Gamma (adres adam@gamma.pl).

Hardware Forum 2026 – spotkanie dla projektantów elektroniki militarnej i dual use

Hardware Forum 2026 – spotkanie dla projektantów elektroniki militarnej i dual use  Evertiq Expo Kraków 2026 – wydarzenie, które rośnie razem z branżą elektroniki

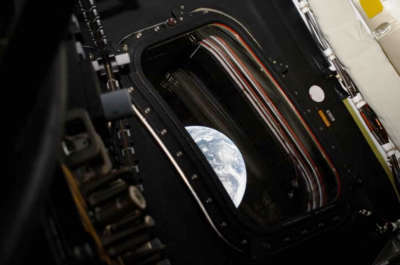

Evertiq Expo Kraków 2026 – wydarzenie, które rośnie razem z branżą elektroniki  Technologia Infineon sprawdziła się w kosmosie podczas misji Artemis II

Technologia Infineon sprawdziła się w kosmosie podczas misji Artemis II