Terasic DE0-Nano – miniaturowy zestaw startowy z FPGA dla początkujących

Układy FPGA oferują konstruktorom ogromne możliwości – niezwykle elastyczny, w pełni konfigurowalny sprzęt i duże zasoby logiczne – ale są „trudniejsze” do użycia niż mikrokontroler ATmega i środowisko Arduino. O tym, że te trudności łatwo pokonać przekonują się szybko ci, którzy podejmują próby wykonania projektów w FPGA, w czym bardzo pomagają takie zestawy jak Terasic DE0-Nano.

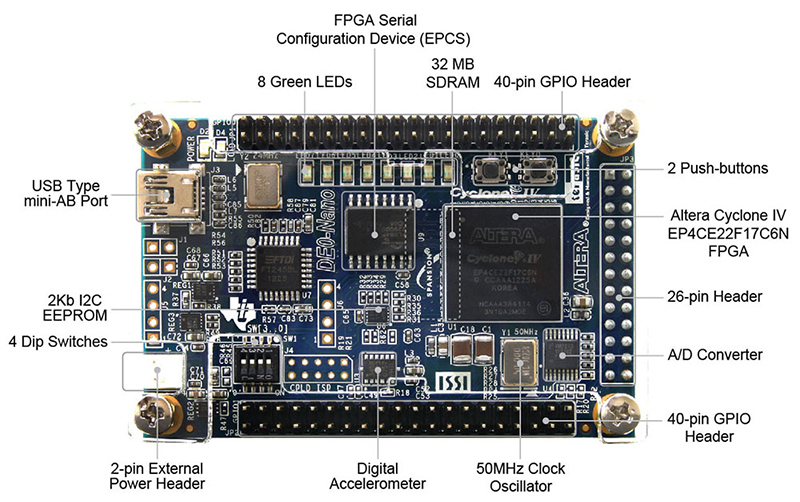

Zestaw Terasic DE0-Nano charakteryzuje się niewielkimi wymiarami i niską ceną, jednocześnie oferując duże zasoby logiczne układu FPGA z rodziny Altera Cyclone IV seria E, kilka elementów peryferyjnych oraz zintegrowany w zestawie programator-konfigurator zgodny z USB Blasterem firmy Altera. Wygląd płytki zestawu pokazano na fotografii 1.

Fot. 1. Wygląd zestawu startowego Terasic DE0-Nano

Jak widać, płytka drukowana zestawu jest osłonięta od góry przed bezpośrednim dotykiem za pomocą frezowanej płytki wykonanej z transparentnego tworzywa sztucznego. Zapobiega ona możliwości przypadkowego dotknięcia podzespołów przez użytkownika, co może powodować nieprawidłową pracę zestawu, grozi także jego uszkodzeniem wywołanym ładunkami elektrostatycznymi. Kształt transparentnej płytki osłonowej zapewnia dostęp użytkownika do DIP-switcha oraz mikroswitchy, zapewniono także wygodny dostęp do dwóch złącz szpilkowych typu gold-pin, na które wyprowadzono linie GPIO układu FPGA.

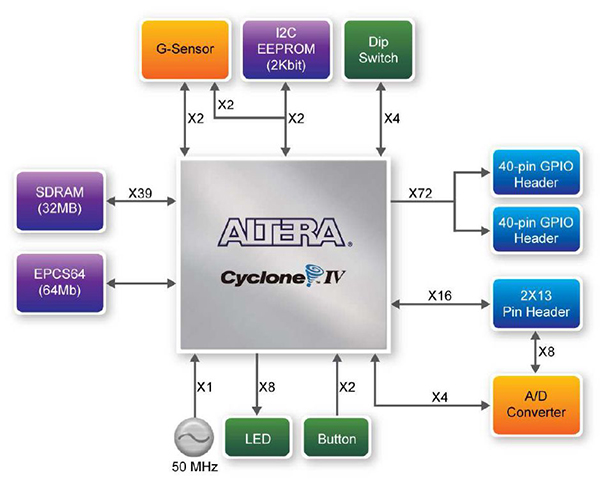

Schemat blokowy zestawu Terasic DE0-Nano pokazano na rysunku 2.

Rys. 2. Schemat blokowy zestawu Terasic DE0-Nano

Na rysunku 3 pokazano elementy peryferyjne zestawu dostępne dla użytkownika, które są ulokowane na górnej stronie PCB.

Rys. 3. Elementy wyposażenia zestawu Terasic DE0-Nano widoczne od strony górnej PCB

Rolę interfejsu użytkownika w prezentowanym zestawie spełniają:

- 4-pozycyjny DIP-switch,

- 2 mikroswitche,

- 8 zielonych LED.

Dwie dodatkowe LED sygnalizują dołączenie napięcia zasilającego oraz pracę interfejsu USB Blaster. Kolejne elementy peryferyjne widoczne na rysunku 3 to:

- generator sygnału zegarowego o częstotliwości 50 MHz,

- akcelerometr MEMS 3D (ADXL345),

- 12-bitowy, 8-kanałowy przetwornik A/C (ADC128S022) o maksymalnej częstotliwości próbkowania 200 kHz.

Projekty inteligentnych sterowników przetwornic buck z tranzystorami GaN — część 1: Zagadnienia i pomiary

Projekty inteligentnych sterowników przetwornic buck z tranzystorami GaN — część 1: Zagadnienia i pomiary  Prof. Ryszard Tadeusiewicz: Sztuczna inteligencja wykorzystująca seks w komputerze

Prof. Ryszard Tadeusiewicz: Sztuczna inteligencja wykorzystująca seks w komputerze  Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)