Mikrokontrolery firmy NXP (Jennic) do aplikacji w systemach komunikacji radiowej

Bezprzewodowa transmisja danych jest obecnie technologią powszechnie spotykaną w każdej dziedzinie techniki. O jej popularności świadczyć może ilość oraz różnorodność obszarów, w których występuje.

Wśród licznych aplikacji korzystających z tego rodzaju komunikacji wymienić można między innymi systemy zdalnego sterowania, systemy telemetryczne, sieci czujnikowe, systemy komunikacji głosowej, automatykę budynkową, urządzenia medyczne, robotykę i wiele innych. Tak duża liczba zastosowań jest przyczyną nieustannie rosnącego zapotrzebowania na kolejne, coraz nowocześniejsze i bardziej zaawansowane rozwiązania z zakresu komunikacji bezprzewodowej. Jednym z wiodących producentów w tej dziedzinie jest powstała w 1996 roku firma Jennic. W 2010 roku firma ta została przejęta przez NXP Semiconductors, w ofercie którego obecnie znajduje się cała gama dotychczasowych produktów firmy Jennic.

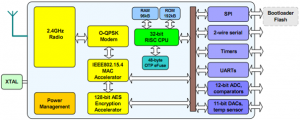

Podstawowym produktem firmy Jennic są tak zwane mikrokontrolery „bezprzewodowe” (wireless microcontrollers). Nazwa ta pochodzi od zintegrowanych w strukturze układów bloków funkcjonalnych umożliwiających realizację komunikacji radiowej (w tym m.in. kompletny transceiver radiowy na pasmo ISM). Pierwszym układem z tej grupy jest mikrokontroler JN5139. Jego budowę wewnętrzną przedstawiono na rys. 1.

Rys. 1. Schemat blokowy mikrokontrolera JN5139

Klasyczna część mikrokontrolera zbudowana jest z 32-bitowego procesora o architekturze RISC, pamięci (192 kB ROM, 96 kB RAM oraz dodatkowych 48 B wykorzystywanych do procesu szyfrowania danych w standardzie AES), interfejsów komunikacyjnych (SPI, I2C, UART), peryferiów cyfrowych (układy licznikowe), peryferiów analogowych (12-bitowego przetwornika A/C, komparatora analogowego, 11-bitowego przetwornik C/A, czujnika temperatury) oraz wyprowadzeń ogólnego przeznaczenia (do 21). Część układu odpowiedzialna za bezprzewodową transmisję danych składa się z obwodu nadawczo-odbiorczego dla pasma 2.4 GHz, modemu O-QPSK, kontrolera dla standardu komunikacyjnego IEEE802.15.4 oraz bloku szyfrującego. Elementy te pozwalają na osiągnięcie prędkości transmisji do 250 kb/s, czułości odbiornika na poziomie -97 dBm i mocy nadajnika 3 dBm. Pobór prądu przez mikrokontroler z aktywnym transceiverem radiowym w trybie odbiorczym powoduje pobór prądu na poziomie 37 mA, natomiast w trybie nadawczym 38 mA. Ograniczenie zużycia energii jest możliwe poprzez wykorzystanie jednego z dwóch trybów pracy o niskim poborze prądu: Sleep Mode lub Deep Sleep.

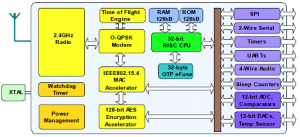

Drugim mikrokontrolerem w ofercie firmy Jennic jest układ JN5148, którego schemat blokowy przedstawiono na rys. 2.

Rys. 2. Schemat blokowy mikrokontrolera JN5148

Jego budowa jest zbliżona do JN5139, jednak w porównaniu z nim JN5148 cechuje się nowszą konstrukcją. Producent zintegrował w układzie dodatkowe peryferia: watchdog, interfejs audio I2S oraz interfejs debuggowania i programowania JTAG. Zoptymalizowana została ponadto część radiowa mikrokontrolera poprzez dodanie do niej funkcji umożliwiającej szacowanie odległości między węzłami sieci (technologia Time of Flight). Wprowadzone usprawnienia nie tylko zwiększyły funkcjonalność układu JN5148 w odniesieniu do JN5139, ale wpłynęły też na jego lepsze osiągi. Pobór prądu układu JN5148 został zmniejszony do 15 mA w trybie nadawczym i do 17,5 m w trybie odbiorczym. Jednocześnie transmisja danych może przebiegać ze znacznie wyższą prędkością – do 667 kb/s. Zestawienie porównawcze mikrokontrolerów JN5139 i JN5148 przedstawiono w tab. 1.

Tab. 1. Porównanie mikrokontrolerów „radiowych” firmy Jennic (NXP)

| JN5139 | JN5148 | |

| Procesor | 32-bit RISC | |

| Częstotliwość taktowania CPU | 16 MHz | 4 – 32 MHz |

| Pamięć • ROM • RAM |

192 kB |

128 kB |

| Peryferia | SPI UART Timer I2C 21 x GPIO ADC (rozdzielczość 12 b) DAC (rozdzielczość 11 b) |

SPI UART Timer I2C 21 x GPIO ADC (rozdzielczość 12 b) DAC (rozdzielczość 12 b) I2S Watchdog |

| Sposób programowania | bootloader | bootloader, JTAG |

| Czułość odbiornika | -97 dBm | -95 dBm |

| Moc nadajnika | 3 dBm | 2.5 dBm |

| Prędkość transmisji | 250 kb/s | 250 kb/s 500 kb/s 667 kb/s |

| Zasilanie | 2,2 V – 3,6 V | 2,0 V – 3,6 V |

| Zakres temperatury pracy | od -40°C do +85°C | |

| Obudowa | QFN56 (8 mm x 8 mm) | |

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii  Firma Nordic Semiconductor wprowadza adaptacyjne monitorowanie stanu baterii dla urządzeń IoT

Firma Nordic Semiconductor wprowadza adaptacyjne monitorowanie stanu baterii dla urządzeń IoT