Układy FinFET w technologii 14 nm firmy Samsung

Samsung stawia kolejny krok w rozwoju 14-nanometrowej technologii produkcji układów scalonych z tranzystorami FinFET. Przy współpracy z firmami ARM, Cadence, Mentor i Synopsys, koreańskiemu producentowi udało się przygotować produkcyjne maski układów klasy SoC wykonane w technologii jego autorstwa. Samsung podpisał także z firmą ARM umowę na opracowanie fizycznego rdzenia IP i bibliotek elementów w swojej technologii.

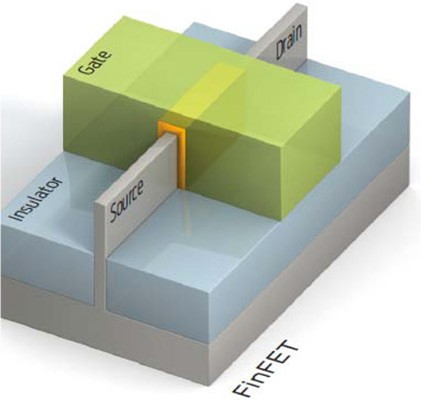

Tranzystory FinFET są traktowane jako przyszłość mikroelektroniki po dojściu do granic rozwoju planarnych tranzystorów polowych. Są one coraz częściej wykorzystywane przez producentów układów scalonych, głównie ze względu na ograniczony statyczny pobór prądu wynikający z mniejszych upływności oraz perspektywy dalszej miniaturyzacji. Opracowanie układów kasy SoC wykorzystujących te tranzystory, produkowanych w technologii 14 nm to kolejny krok w rozwoju technik projektowania i produkcji układów scalonych, mogący wpłynąć m.in. na rynek urządzeń mobilnych.

W ramach procesu rozwojowego Samsung, wraz z partnerami, przygotował kilka różnych układów, od pełnej implementacji procesora z rdzeniem Cortex-A7, aż po pamięci SRAM i analogowe układy IP.

Testowy chip procesora z rdzeniem Cortex-A7 został zaimplementowany przede wszystkim przez firmę Cadence. Cadence dostarczył kompletny proces projektowy RTL to sign-off, opierając się na zestawie narzędzi przetestowanym dokładnie na projektach 20 nm. Ścisła współpraca z Samsungiem i ARM pozwoliła dopasować te narzędzia do technologii 14 nm. Firma ARM wykorzystała narzędzia Cadence do opracowania bibliotek 14-nanometrowych modułów FinFET. Narzędzia Cadence użyte został także do przygotowania tapeoutu rdzenia procesora w 14-nm procesie produkcyjnym opracowanym przez firmę Samsung, a także integrację i weryfikację na poziomie czipu.

Samsung wykorzystał także narzędzia firmy Synopsys, zoptymalizowane pod kątem układów FinFET, do implementacji innych modułów IP, m.in. energooszczędnych pamięci SRAM mogących pracować z zasilaniem bliskim napięcia progowego.

Dzięki dostępnemu już zestawowi Process Design Kit (PDK), projektanci mogą rozpocząć pracę w nowej technologii dzięki modelom, zestawom reguł projektowych i plikom technologicznym, opracowanym w oparciu o wyniki uzyskane przy testach wcześniejszych 14-nm czipów FinFET firmy Samsung. PDK wyposażony jest w procesy projektowe (design flows), moduły automatycznego rutowania i inne narzędzia obsługujące nowe struktury układów i połączenia lokalne.

Więcej informacji: Soyter Sp. z o.o., Klaudyn, ul. Ekologiczna 14/16, 05-080 Izabelin, http://www.soyter.pl.

Polska chce zwiększyć znaczenie sektora półprzewodników. Toczą się prace nad krajową polityką w tym obszarze

Polska chce zwiększyć znaczenie sektora półprzewodników. Toczą się prace nad krajową polityką w tym obszarze  Medicalgorithmics wesprze nowego partnera z Korei Południowej w ekspansji na rynku amerykańskim

Medicalgorithmics wesprze nowego partnera z Korei Południowej w ekspansji na rynku amerykańskim  PGZ i Frankenburg Technologies pogłębiają strategiczną współpracę w obszarze nowoczesnych systemów obronnych

PGZ i Frankenburg Technologies pogłębiają strategiczną współpracę w obszarze nowoczesnych systemów obronnych