Altera Cyclone V SoC: dwurdzeniowy mikroprocesor Cortex-A9 i FPGA w jednym układzie

Konfigurowalna matryca logiczna w układach Cyclone V SoC jest konfigurowana z wykorzystaniem mechanizmów dotychczas wykorzystywanych w układach FPGA firmy Altera, producent przewidział ponadto możliwość jej częściowej rekonfiguracji w trybie FPP (Fast Passive Parallel, maksymalna częstotliwość taktowania 125 MHz, szerokość magistrali danych 8 lub 16 bitów) oraz w trybie CvP (Configuration via Protocol, z wykorzystaniem magistrali PCIe). Rekonfiguracja częściowa umożliwia implementację w układach Cyclone V SoC projektów partycjonowanych, co w niektórych przypadkach pozwoli zminimalizować koszt implementacji własnych bloków peryferyjnych w FPGA.

Prezentowane układy wyposażono także w wewnętrzny system generacji sygnałów zegarowych, bazujący na programowanych PLL (w zależności od typu układu jest 5 lub 6, dodatkowo 3 generatory z PLL służą do taktowania rdzenia HPS), za którego pomocą można wygenerować precyzyjne sygnały zegarowe o częstotliwości do 550 MHz, przy czym możliwość ułamkowego ustalania współczynników powielania powoduje, że dobranie częstotliwości sygnału do wymogów aplikacji jest proste. Budowa systemu taktującego FPGA wspomaga mechanizmy oszczędzania energii, a system programowania fazy sygnałów zegarowych umożliwia optymalizację częstotliwością dużych projektów.

Układy Cyclone V SoC – podobnie jak pozostałe FPGA z oferty Altery – wyposażono w bloki konfigurowalnych pamięci, rodzielone na dwa rodzaje zasobów:

- bloki M10K (o pojemności 10 kb każdy), przy których zintegrowano system ECC (Error Correction Code),

- bloki pamięci rozproszonej MLAB (Memory Logic Array Block ), każdy o pojemności 640 bitów, które są ekstrahowane podczas syntezy logicznej z bloków ALM (można w ten sposób wykorzystać do 25% komórek ALM).

W poszczególnych rodzinach Cyclone V SoC zintegrowano następujące liczby bloków M10K/MLAB:

- Cyclone V SE: 1400…5570/138…621,

- Cyclone V SX: 1400…5570/138…621,

- Cyclone V ST: 3970…5570/480…621.

Tab. 3. Rodzaje pamięci obsługiwanych przez kontroler FPGA

Tab. 4. Rodzaje pamięci obsługiwanych przez interfejs HPS

Opracowane przez ARM rdzenie Cortex-A9 (w wersji MPCore) charakteryzują się wydajnością dochodzącą do 2,5 MIPS/MHz, co przy maksymalnej dopuszczalnej częstotliwości ich taktowania wynoszącej 800 MHz daje ogromną moc obliczeniową wynoszącą nawet 2 GMIPS/rdzeń. Standardowym wyposażeniem tego rdzenia – poza FPU – są koprocesory NEON (wspomaganie obliczeń dla aplikacji multimedialnych) oraz Jazelle (sprzętowe wspomaganie interpreterów Javy), a także 2 zespoły pamięci cache L1 (po 32 kB) oraz 512 kB pamięci cache L2.

Rys. 4. Budowa bloku procesorowego HPS w układach Cyclone V SoC

Rdzenie wraz z otoczeniem, w skład którego wchodzą także m.in. lokalny interfejs pamięci DDS SDRAM z obsługą ECC, kontroler pamięci NAND Flash, programowalny system DMA (8-kanałowy), dwa interfejsy USB-OTG, dwa bloki MAC Ethernet (1 Gb/s), synchroniczne interfejsy SD/MMC, tworzą blok HPS (Hard Processor System – rysunek 4). Każdy z rdzeni wyposażono oczywiście w blok sprzętowego monitorowania jego pracy ETR, wokół HPS zintegrowano także peryferia charakterystyczne dla standardowych systemów mikroprocesorowych, jak na przykład: bloki timerów, UART-y, interfejsy Flash SPI/QSPI itp.).

Rys. 5. Blok HPS komunikuje się z FPGA za pomocą specjalnego interfejsu dwukierunkowego

Niebagatelnym wyzwaniem stojącym przed konstruktorami układów Cyclone V SoC było opracowanie sposobu komunikacji rdzeni mikroprocesorowych z rekonfigurowalnym otoczeniem zaimplementowanym w strukturze FPGA. Do tego celu służy szerokopasmowy, dwukierunkowy mostek komunikacyjny HPS-to-FPGA (rysunek 5), który bazuje na 32-/64-/128-bitowym interfejsie komunikacyjnym AMBA AXI-3 opracowanym przez ARM. Jego konstrukcja umożliwia kontrolowany dostęp do 6 bloków-masterów zaimplementowanych w FPGA do systemowej pamięci SDRAM. Interfejs ten może być także wykorzystywany do konfigurowania FPGA przez wbudowany mikroprocesor.

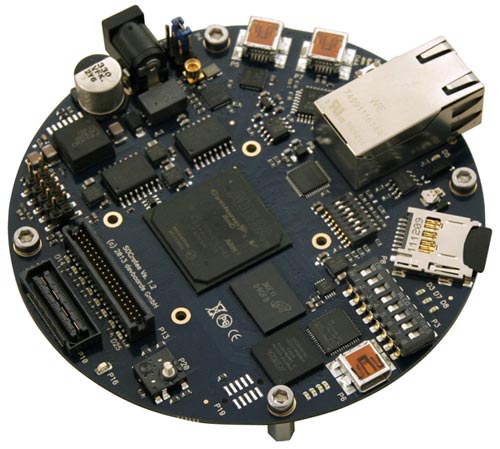

Fot. 6. Wygląd zestawu SoCrates

Układy SoC firmy Altera są stosunkowo nowe na rynku, ale już jest dostępny efektowny (i efektywny) zestaw startowy SoCrates (fotografia 6), który wyposażono w układ z rodziny Cyclone V SE (5CSEBA6U23C7N). Układ ten ma wbudowane 11 0000 LE, 41509 bloków ALM, 112 bloków DSP, 224 multiplikatory 18×18 bitowe, obudowa BGA672, dwurdzeniowy procesor Cortex-A9, wyposażono go ponadto w 288 wyprowadzeń FPGA i 181 wyprowadzeń części procesorowej.

Otoczenie układu SoC w zestawie SoCrates przypomina klasyczne komputery embedded, w jego skład wchodzą m.in.: cyfrowy czujnik temperatury, zegar czasu rzeczywistego, 1 GB pamięci DDR3 (w konfiguracji 32-bitowej), interfejs Ethernet 1 Gb/s, 1 kanały USB-OTG 2.0, a także interfejsy komunikacyjne CAN, SPI, I2C i UART z konwersją na USB. Użytkownik ma do dyspozycji złącze TFT-TP, złącze kamery CCD z interfejsem LVDS, 5-pozycyjny joystick, łącznie 12 diod LED oraz 78 linii GPIO. Integralną częścią zestawu SoCrates jest także programator-konfigurator FPGA zgodny z alterowskim USB-Blasterem, który jest natywnym interfejsem dla środowiska projektowego FPGA Quartus II.

Producent przygotował dla tego zestawu także dystrybucję systemu operacyjnego Linux, dzięki czemu użytkownicy mogą „od ręki” zacząć weryfikację przydatności układów SoC w systemach embedded.

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii  Mieszacze aktywne – ćwiczenie z serii ADALM

Mieszacze aktywne – ćwiczenie z serii ADALM