Tajniki XMC1100: 32-bitowy Cortex-M0 na 32 MHz

Mikrokontrolery XMC1100 firmy Infineon cieszą się w naszym kraju sporym zainteresowaniem, które ma szanse zaowocować – już w niedalekiej przyszłości – także popularnością. Są to „pełnokrwiste” Corteksy wyposażone w najprostszy rdzeń z tej rodziny – M0 – charakteryzujące się relatywnie prostą budową, ale wyposażone w pomysłowe bloki peryferyjne.

Mikrokontroler z rodziny XMC1100 jest „sercem” zestawu startowego XMC2go, których 50 sztuk mamy do rozlosowania wśród uczestników konkursu.

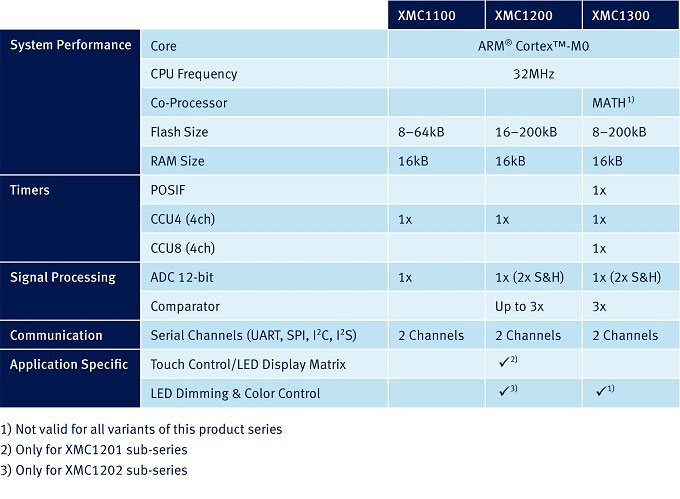

Mikrokontrolery XMC1100 należą do rodziny mikrokontrolerów XMC1000, w skład której wchodzą trzy podrodziny: XMC1100, XMC1200 i XMC1300 (ich podstawowe cechy zestawiono w poniższej tabeli). Wszystkie podrodziny wyposażono w 32-bitowy rdzeń Cortex-M0, taktowany z maksymalną częstotliwością zegarową 32 MHz. Praca mikrokontrolera może być monitorowana za pomocą jednego z dwóch, 1-liniowych interfejsów: SWD (Serial Wire Debug) lub SPD (Single Pin Debug), te same interfejsy można wykorzystać do programowania pamięci Flash mikrokontrolera.

| Firma Infineon przygotowała i bezpłatnie udostępniła pakiet bibliotek dla edytorów SCH i PCB pakietu Altium Designer. Publikujemy je na dole strony do pobrania. |

Zestawienie podstawowych cech mikrokontrolerów XMC1000

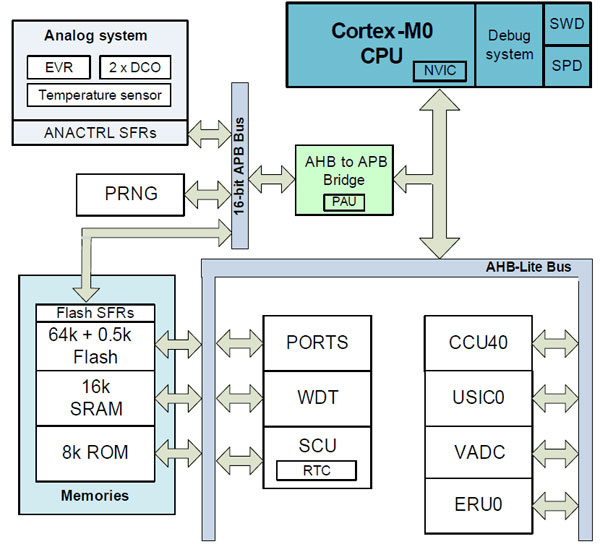

Prezentowane w artykule mikrokontrolery – podrodzina XMC1100 – charakteryzują się najprostszą budową w rodzinie XMC1000, ale nie oznacza to, że odbija się to na ich wewnętrznym wyposażeniu. Poza elementami standardowymi dla otoczenia rdzenia Cortex-M0 (jak na przykład timery: SysTick oraz WDT, kontroler przerwań NVIC, pamięci Flash/RAM czy jednotaktowy multiplikator sprzętowy), wyposażono je w:

- progarmowalny moduł konfiguracji przerwań Event Request Unit (ERU), który nieco dokładniej przedstawimy w dalszej części artykułu,

- dwa moduły komunikacyjne Universal Serial Interface Channels (USIC), które mogą pracować jako UART, dwukanałowy SPI lub QSPI (master/slave), a także jako I2C (master/slave), I2S lub LIN,

- 12-bitowy przetwornik A/C z 12-kanałowym multiplekserem analogowym,

- 4-kanałowy timer-licznik CCU4 z możliwością generacji PWM,

- licznik RTC oraz System Control Unit (SCU),

- wbudowany w strukturę czujnik temperatury (TSE),

- sprzętowy generator liczb pseudolosowych (PRNG), który zapewnia szybką generację losowych 16-bitowych danych.

- Schemat blokowy mikrokontrolerów XMC1100 pokazano na rysunku 1.

Rys. 1. Schemat blokowy mikrokontrolerów XMC1100

Mikrokontrolery z prezentowanej w artykule serii są dostarczane w kilku wersjach obudów, począwszy od łatwych w montażu TSSOP16 i TSSOP38, do VQFN40 i VQFN24.

O ile sam rdzeń w prezentowanych mikrokontrolerach i jego otoczenie nie budzi specjalnych emocji, to producent zadbał o dopieszczenie kilku szczegółów, dzięki którym XMC1000 wyróżniają się na rynku.

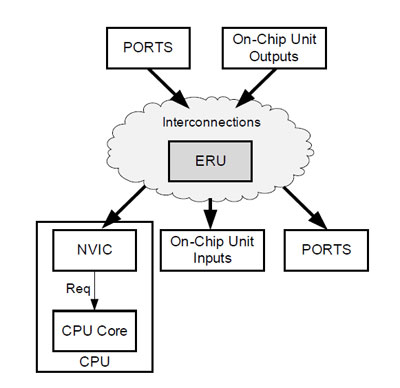

Rys. 2. Schemat przepływu sygnałów przerwań w mikrokontrolerach XMC1000

| Czytelnicy zainteresowani poznaniem mikrokontrolerów XMC1000 w praktyce mogą skorzystać z bezpłatnych środowisk programistycznych DAvE lub ARM-MDK. |

Jednym z udoskonalonych w nich elementów jest interfejs kontrolera przerwań NVIC, który nosi nazwę ERU od Event Request Unit. Jest to konfigurowalny blok pośredniczący pomiędzy źródłami przerwań i kontrolerem NVIC oraz blokami peryferyjnymi, które są przystosowane np. do wyzwalania za pomocą sygnałów pochodzących z systemu obsługi przerwań (rysunek 2).

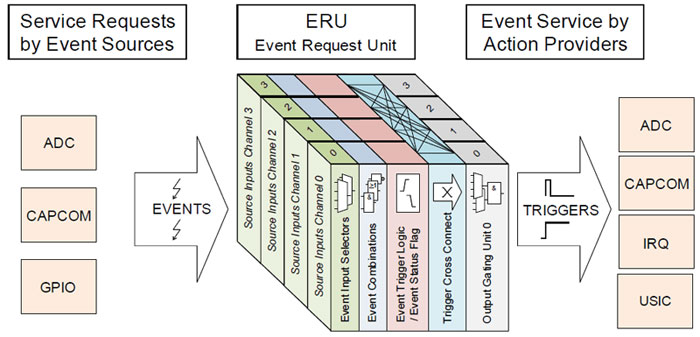

Na rysunku 3 pokazano schemat blokowy ERU, na którym widać pięć konfigurowalnych warstw (od lewej strony rysunku):

- selektory zdarzeń, które służą do wyboru źródła sygnału przerwania spośród: przetwornika ADC, linii GPIO i timera CCU4 (na rysunku oznaczony jako CAPCOM),

- funkcje logiczne umożliwiające wzajemne powiązanie sygnałów przerwań,

- blok selekcji zbocza wywołującego przerwanie oraz rejestr flag przerwań, monitorowanych programowo,

- warstwa krosująca sygnały przerwań/flagi statusu przerwań,

- warstwa sterująca włączaniem i wyłączaniem sygnałów przerwań i wyzwalających, o konfiguracjach ustalonych w czterech warstwach konfiguracyjnych.

Rozwiązanie zaproponowane przez firmę Infineon pozwala odciążyć CPU i NVIC od obsługi ciągu zdarzeń typu: „wyzwolenie pomiaru ADC po odmierzeniu zadanego czasu” i podobnych, co zdecydowanie upraszcza pisanie aplikacji, w której mikrokontroler interaktywnie współpracuje z otoczeniem.

Rys. 3. Schemat blokowy ERU z widocznymi warstwami konfiguracji przerwań i flag statusów

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii