Mikrokontrolery AVR XMEGA w praktyce, część 17. Interfejs SPI

SPI (Serial Peripheral Interface) jest jednym z trzech najważniejszych interfejsów komunikacyjnych, obok I2C oraz UART. Jest to interfejs typu full-duplex, czyli możliwe jest jednoczesne wysyłanie i odbieranie danych. SPI to interfejs synchroniczny, a więc jednym z przewodów przesyła się sygnał zegarowy, synchronizujący wszystkie układy. Możliwe jest połączenie wielu układów. Najczęściej w sieci mamy jeden układ typu master, który wysyła polecenia do układów slave i odczytuje z nich dane. Tylko master może rozpocząć transmisję i to on może generować sygnał zegarowy. Sieci SPI multi-master są rzadko spotykane.

Jak działa SPI?

Magistrala SPI składa się najczęściej z czterech linii. Są to:

- MOSI (master out, slave in) – linia łącząca wyjście danych z mastera i wejścia slave’ów,

- MISO (master in, slave out) – linia łącząca wyjście danych slave i wejście mastera,

- SCK (serial clock) – sygnał zegarowy, synchronizujący układy na magistrali,

- CS (chip select) – sygnał informujący slave o rozpoczęciu transmisji; sygnał ten jest zanegowany, co oznacza się poziomą kreską nad literami CS; uaktywnienie slave’a następuje po wystąpieniu stanu niskiego na linii, a stan wysoki układ slave deaktywuje.

Różni producenci stosują różne nazwy. Zdarzają się skrócone wersje SO i SI lub po prostu O oraz I.

Budowę interfejsu SPI przedstawiono na rysunku 1. Jest on oparty na rejestrach przesuwnych. Są to układy składające się z szeregu przerzutników D, synchronizowanych jednym sygnałem zegarowym. W momencie wystąpienia odpowiedniego zbocza zegara, bit zapisany w przerzutniku 1 przesyłany jest do przerzutnika 2, z 2 do 3, z 3 do 4, itd. Do przerzutnika 1 wpisywany jest stan logiczny doprowadzony na wejście łańcucha, natomiast wyjście ostatniego przerzutnika jest wyjściem całego rejestru. Co by było, gdyby wyjście połączyć z wejściem? W takiej sytuacji, dane „kręciły by się w kółko”. Konstrukcja taka zwana jest rejestrem pierścieniowym i ma zastosowanie w SPI.

Zarówno master i slave mają rejestr przesuwny, składający się najczęściej z 8 przerzutników, przechowujących 1 bajt danych. Master posiada generator sygnału zegarowego, który steruje pracą wszystkich przerzutników. Linie MISO i MOSI tworzą pierścień, jednak dane pomiędzy masterem i slavem nie kręcą się w kółko w nieskończoność. Co osiem taktów zegara, a więc kiedy zostanie przesłany pełny bajt, zarówno master jak i slave mogą zmienić zawartość swoich rejestrów, przed kolejnym cyklem 8 taktów zegara.

Wynika z tego ważny wniosek – aby master odczytał dane ze slave’a, musi w tym samym czasie coś mu wysyłać. Na ogół są to same zera, jednak należy o tym pamiętać, że SPI jest interfejsem full-duplex.

Wyjaśnienia może wymagać jeszcze bufor trójstanowy na wyjściu ze slave’a. Jest on niezbędny ze względu na to, że do magistrali SPI można podłączyć wiele układów, ale nadawać może tylko jeden z nich. W sytuacji kiedy master dezaktywuje slave’a, bufor trójstanowy odłącza wyjście rejestru przesuwnego od magistrali i slave udaje, że go nie ma. Dzięki temu inny slave może przesyłać dane, bez obawy o konflikt pomiędzy nadajnikami.

Rys. 1. Budowa interfejsu SPI

Najczęściej spotykaną topologią sieci jest magistrala liniowa (patrz rysunek 2). Wszystkie układy są równolegle połączone do linii MISO, MOSI oraz SCK, a więc wszystkie układy „słyszą”, co się dzieje na magistrali. Skąd slave’y wiedzą, który z nich ma być odbiornikiem transmisji? Do tego służą oddzielne linie CS, po jednej dla każdego układu slave. W stanie spoczynkowym, na wszystkich liniach CS występuje stan 1 – wtedy wszystkie układy są nieaktywne, a ich wyjścia MISO są ustawione w stan wysokiej impedancji. Master wybiera żądany układ slave ustawiając stan 0 na odpowiedniej linii CS. W sieci o takiej topologii mogą pracować różne układy SPI, niezależnie od ich producenta czy przeznaczenia.

Rys. 2. Układy SPI połączone w magistralę liniową

Czasami spotyka się układy SPI połączone w łańcuszek (niektórzy mówią głuchy telefon – czasami jest to bardzo trafne określenie takiego połączenia). Wyjście MOSI mastera jest połączone z wejściem slave’a 1, wyjście slave 1 łączy się z wejściem slave 2, itp., a wyjście ostatniego slave łączy się z wejściem MISO mastera. Taką sytuację przedstawia rysunek 3. Sygnały SCK oraz CS są połączone do wszystkich slave’ów równolegle.

Takie rozwiązania stosuje się, gdy mamy do czynienia z wieloma układami tego samego typu. Dobrym przykładem są tu sterowniki wyświetlaczy LED oparte na rejestrach przesuwnych. Można ich łączyć dziesiątki lub nawet setki. Innym przykładem, choć nieco odbiegającym od tematyki SPI, jest interfejs JTAG.

Rys. 3. Układy SPI połączone w magistralę łańcuchową (daisy chain)

SPI nie precyzuje, czy dane mają być wysyłane od najstarszego czy najmłodszego bitu. Możemy sami to ustawić, w zależności od tego, co wymaga konkretny układ slave. Możemy również sprecyzować, czy dane mają być przesuwane w rejestrach po wystąpieniu zbocza rosnącego czy opadającego sygnału zegarowego SCK. Przykładowe konfiguracje i przebiegi sygnałów przedstawiono na rysunku 4.

Rys. 4. Tryby przesyłania danych

Dominik Leon Bieczyński

Bezpieczeństwo AI pod presją. Cisco publikuje raport „State of AI Security 2026”

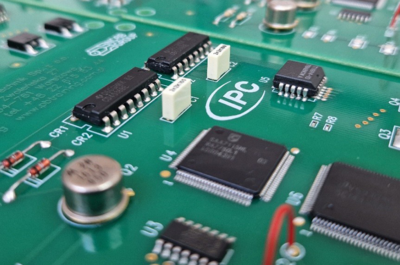

Bezpieczeństwo AI pod presją. Cisco publikuje raport „State of AI Security 2026”  IPC-A-610 i IPC-J-STD-001: Nierozłączny duet w profesjonalnej produkcji elektroniki

IPC-A-610 i IPC-J-STD-001: Nierozłączny duet w profesjonalnej produkcji elektroniki  Nie ma rzeczy niemożliwych: polska elektronika na ISS

Nie ma rzeczy niemożliwych: polska elektronika na ISS