AD9361: Analog(owy) sposób na SDR

Firma Analog Devices jest jednym z niewielu producentów, którzy mają kompleksową ofertę podzespołów dla takich aplikacji i na bazie wieloletnich doświadczeń zaoferowała odbiorcom zintegrowane tory nadawczo-odbiorcze, tworzące rodzinę Agile Transceiver.

|

Firma Analog Devices uruchomiła specjalną stronę w swoim portalu internetowym, która jest poświęcona zagadnieniom SDR. jest ona dostępna pod adresem. Hasłem przewodnim tej strony jest nietypowe rozwinięcie akronimu SDR: Software Defined Revolution, co pokazuje dostrzegany przez Analog Devices potencjał tej technologii. |

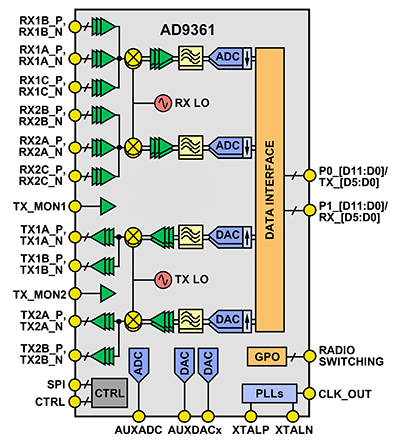

Są to kompletne transceivery (nadajniki + odbiorniki) dla aplikacji SDR, w których zintegrowano wszystkie elementy – od wzmacniaczy wejściowych (tor odbiorczy) i driverów wyjściowych (tor nadawczy) aż po przetworniki A/C i C/A, co znakomicie upraszcza budowę urządzeń nadawczo-odbiorczych. Schemat blokowy układu AD9361 (w układzie zintegrowano 2 tory nadawcze i 2 tory odbiorcze) pokazano na rysunku 5. Obecnie w rodzinie Agile Transceiver dostępny jest jeszcze jeden układ – AD9364 – który jest 1-kanałowym transceiverem, uproszczonym funkcjonalnym odpowiednikiem AD9361.

Rys. 5. Schemat blokowy 2-kanałowego transceivera SDR – AD9361 firmy Analog Devices

Jak widać, w układzie AD9361 zintegrowano zarówno tory wejściowe i wyjściowe (działające w pasmie do 6 GHz przy szerokości kanału od 200 kHz do 56 MHz), mieszacze oraz generatory lokalne zasilające je sygnałami o programowanej częstotliwości, filtry decymacyjne, filtry FIR, przetworniki A/C i C/A wykorzystywane w transceiverze oraz przetworniki pomocnicze (10-bitowe C/A i 12-bitowy A/C). Konfiguracja i zmiana ustawień układu AD9361 odbywa się za pomocą interfejsu SPI, dane do/z przetworników sygnałowych może się odbywać magistralami pracującymi w standardzie napięciowym CMOS lub LVDS.

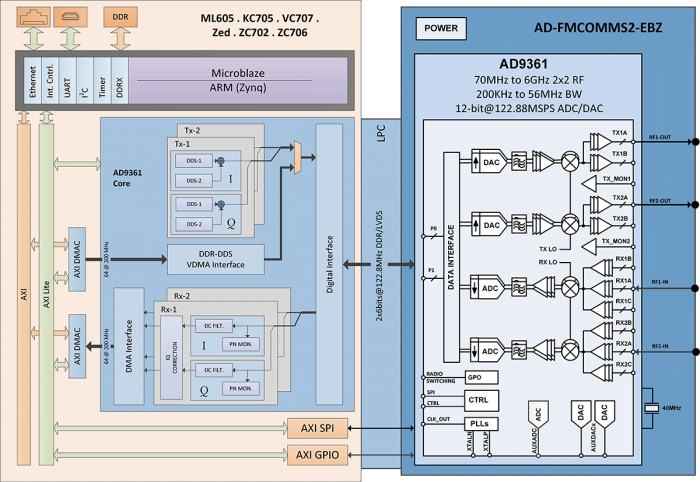

Fot. 6. Schemat blokowy transcievera SDR wykonanego na układzie AD9361 i układzie SoC firmy Xilinx

Układy AD9361 i AD9364 realizują funkcję transceiverów SDR, ale wykonanie kompletnego urządzenia nadacz-odbiorczego wymaga zastosowania systemu DSP, który z przetworzonych na postać cyfrową sygnałów I i Q odtworzy przesyłane dane lub sygnał (w torze odbiorczym), lub przygotuje cyfrową postać sygnałów I i Q w zależności od danych jakie mają być przesyłane (w torze nadawczym). Schemat blokowy systemu, który spełnia rolę kompletnego nadajnika-odbiornika pokazano na rysunku 6, rolę systemu DSP spełnia w nim układ SoC (System-on-Chip)) firmy Xilinx, w którym zintegrowano mikroprocesor oraz matrycę FPGA. W układzie FPGA zaimplementowano rdzeń IP, który udostępnia rejestry układu AD9361 w systemie DSP, tworząc dwa sprzętowe tory nadawcze i dwa odbiorcze.

Fot. 7. Wygląd płytki radiowej AD-FMCOMMS3-EBZ z transceiverem AD9361 (standard mechaniczny FMC)

Żeby ułatwić konstruktorom rozpoczęcie prac nad własnymi systemami SDR, firma Analog Devices opracowała i produkuje zestawu startowe ze scalonymi transceiverami SDR, wygląd płytki AD-FMCOMMS3-EBZ z układem AD9361 pokazano na fotografii 7.

Zestaw ten przedstawimy w kolejnym artykule.

Andrzej Gawryluk

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii