STM32F7-DISCOVERY (STM32F746G-DISCOVERY) – test pierwszego zestawu z mikrokontrolerem STM32F7 (Cortex-M7)

Mikrokontrolery STM32F7 (wyposażone w rdzeń Cortex-M7) dojrzewały dość długo w ofercie STMicroelectronics, ale ich rynkowe narodziny mamy za sobą: do sprzedaży trafiło 19 typów nowych mikrokontrolerów, których podstawowe cechy i parametry zebrano w tabeli 1.

Tab. 1. Zestawienie dostępnych typów mikrokontrolerów STM32F7 i najważniejszych elementów ich wyposażenia (kolorem zaznaczono mikorkontroler użyty w zestawie STM32F746G-DISCOVERY)

| Typ | Flash [kB] | SRAM [kB] | Timery 16-bitowe | Timery 32-bitowe | ADC | Licbczba GPIO | DAC | Interfejsy | Obudowa |

| STM32F745IE | 512 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 140 | 2×12-bit | 6 x SPI | BGA 176 LQFP 176 |

| STM32F745IG | 1024 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 140 | 2×12-bit | 1 x SDIO;2 x CAN;2 x SAI;2 x USB OTG;4 x I2C;4 x UART;4 x USART;6 x SPI;Ethernet MAC | BGA 176 LQFP 176 |

| STM32F745VE | 512 | 320 | 12×16-bit | 2×32-bit | 16×12-bit | 82 | 2×12-bit | 2 x I2C;2 x SAI;6 x SPI | LQFP 100 |

| STM32F745VG | 1024 | 320 | 12×16-bit | 2×32-bit | 16×12-bit | 82 | 2×12-bit | 1 x SDIO;2 x CAN;2 x I2C;2 x I2S;2 x USB OTG;4 x UART;4 x USART;6 x SPI;Ethernet MAC | LQFP 100 |

| STM32F745ZE | 512 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 114 | 2×12-bit | 2 x SAI;6 x SPI | LQFP 144 |

| STM32F745ZG | 1024 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 114 | 2×12-bit | 1 x SDIO;2 x CAN;2 x USB OTG;4 x I2C;4 x UART;4 x USART;6 x SPI;Ethernet MAC | LQFP 144 |

| STM32F746BE | 512 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 168 | 2×12-bit | 1 x CEC;1 x SDIO;2 x CAN;2 x SAI;2 x USB OTG;4 x I2C;4 x UART;4 x USART;6 x SPI;Ethernet MAC | LQFP 208 |

| STM32F746BG | 1024 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 168 | 2×12-bit | 1 x CEC;1 x SDIO;2 x CAN;2 x SAI;2 x USB OTG;4 x I2C;4 x UART;4 x USART;6 x SPI;Ethernet MAC | LQFP 208 |

| STM32F746IE | 512 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 140 | 2×12-bit | 1 x CEC;1 x SDIO;2 x CAN;2 x SAI;2 x USB OTG;4 x I2C;4 x UART;4 x USART;6 x SPI;Ethernet MAC | BGA 176 LQFP 176 |

| STM32F746IG | 1024 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 140 | 2×12-bit | 1 x CEC;1 x SDIO;2 x CAN;2 x SAI;2 x USB OTG;4 x I2C;4 x UART;4 x USART;6 x SPI;Ethernet MAC | BGA 176 LQFP 176 |

| STM32F746NE | 512 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 168 | 2×12-bit | 1 x CEC;1 x SDIO;2 x CAN;2 x SAI;2 x USB OTG;4 x I2C;4 x UART;4 x USART;6 x SPI;Ethernet MAC | TFBGA 216L 0.8 |

| STM32F746NG | 1024 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 168 | 2×12-bit | 1 x CEC;1 x SDIO;2 x CAN;2 x SAI;2 x USB OTG;4 x I2C;4 x UART;4 x USART;6 x SPI;Ethernet MAC | TFBGA 216L 0.8 |

| STM32F746VE | 512 | 320 | 12×16-bit | 2×32-bit | 16×12-bit | 82 | 2×12-bit | 1 x CEC;2 x SAI;3 x I2C;4 x I2C;4 x SPI;4 x UART;4 x USART | LQFP 100 |

| STM32F746VG | 1024 | 320 | 12×16-bit | 2×32-bit | 16×12-bit | 82 | 2×12-bit | 1 x SDIO;2 x I2C;2 x I2S;2 x SAI;2 x USB OTG;4 x UART;4 x USART;6 x SPI;Ethernet MAC | LQFP 100 |

| STM32F746ZE | 512 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 114 | 2×12-bit | 1 x CEC;1 x SDIO;2 x CAN;2 x SAI;2 x USB OTG;4 x I2C;4 x UART;4 x USART;6 x SPI;Ethernet MAC | LQFP 144 WLCSP 143L 0.4 |

| STM32F746ZG | 1024 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 114 | 2×12-bit | 1 x CEC;1 x SDIO;2 x CAN;2 x SAI;2 x USB OTG;4 x I2C;4 x UART;4 x USART;6 x SPI;Ethernet MAC | LQFP 144 WLCSP 143L 0.4 |

| STM32F756BG | 1024 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 168 | 2×12-bit | 1 x CEC;1 x SDIO;2 x CAN;2 x SAI;2 x USB OTG;4 x I2C;4 x UART;4 x USART;6 x SPI;Ethernet MAC | LQFP 208 |

| STM32F756IG | 1024 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 140 | 2×12-bit | 1 x CEC;1 x SDIO;2 x CAN;2 x SAI;2 x USB OTG;4 x I2C;4 x UART;4 x USART;6 x SPI;Ethernet MAC | BGA 176 LQFP 176 |

| STM32F756NG | 1024 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 168 | 2×12-bit | 1 x CEC;1 x SDIO;2 x CAN;2 x SAI;2 x USB OTG;4 x I2C;4 x UART;4 x USART;6 x SPI;Ethernet MAC | TFBGA 216L 0.8 |

| STM32F756VG | 1024 | 320 | 12×16-bit | 2×32-bit | 16×12-bit | 82 | 2×12-bit | 1 x CEC;1 x SDIO;2 x CAN;2 x SAI;2 x USB OTG;4 x I2C;4 x UART;4 x USART;6 x SPI;Ethernet MAC | LQFP 100 |

| STM32F756ZG | 1024 | 320 | 12×16-bit | 2×32-bit | 24×12-bit | 114 | 2×12-bit | 1 x CEC;1 x SDIO;2 x CAN;2 x SAI;2 x USB OTG;4 x I2C;4 x UART;4 x USART;6 x SPI;Ethernet MAC | LQFP 144 WLCSP 143L 0.4 |

Rdzenie układów prezentowanych w tabeli są przystosowane do taktowania sygnałem zegarowym o maksymalnej częstotliwości 216 MHz, co pozwala uzyskać mikrokontrolerom wypadkową wydajność obliczeniową 1082 CoreMark i prędkość wykonywania programu 462 DMIPS. Przy tak dużej wydajności producentowi udało się utrzymać – charakterystyczny dla większości współczesnych mikrokontrolerów – niewielki pobór mocy, szacowany pobór prądu przez CPU nie przekracza 420 μA/MHz.

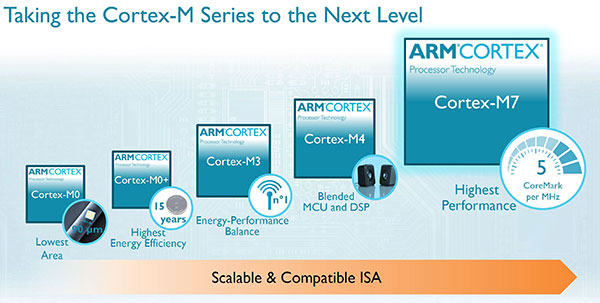

Przypomnijmy, że od strony technicznej Cortex-M7 to rozbudowana wersja rdzenia Cortex-M4, wyposażona w szybką pamięcią SRAM TCM (dla danych i instrukcji programu) oraz cache dla danych i instrukcji (rysunek 1). Dodatkowo zastosowano w tym rdzeniu zaawansowany 6-poziomowy mechanizm przetwarzania potokowego z predykcją oraz sprzętowym wsparciem superskalarnego wykonywania programu.

Rys. 1. Rdzeń Cortex-M7 jest najwydajniejszy w rodzinie Cortex-M, głównie dzięki zastosowaniu w nim rozwiązań pochodzących wprost z mikroprocesorów

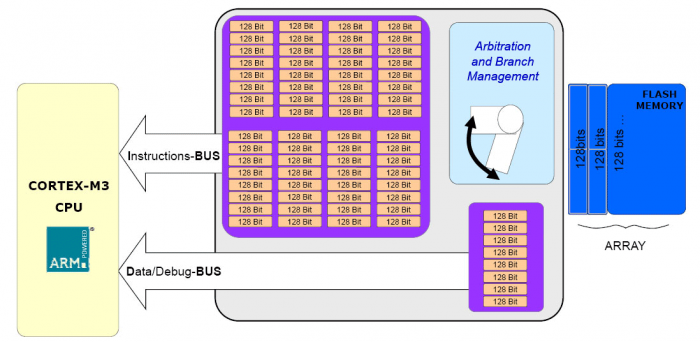

Ważnym udoskonaleniem wprowadzonym w rdzeniu Cortex-M7 jest nowa magistrala służąca do komunikacji CPU z blokami peryferyjnymi, który ma wpływ na wypadkową prędkość pracy mikrokontrolera: Master AXI (AXIM). Zapewnia ona łączenie kilku kanałów magistrali AHB w jeden, bardzo szybki kanał dwukierunkowej komunikacji rdzenia z otoczeniem (w rdzeniach Cortex-M4 rdzeń komunikuje się z otoczeniem za pomocą „standardowych” interfejsów-magistral AHB). Rozwiązania zastosowane przez firmę ARM w rdzeniu Cortex-M7 pozwalają na szybszy niż w przypadku poprzedników dostęp rdzenia do zawartości pamięci SRAM i Flash, oczywiście przy założeniu, że konstrukcja pamięci umożliwia bezpośredni odczyt danych z relatywnie wysoką częstotliwością (dla typowych pamięci nieulotnych za taką uchodzi 70…90 MHz). Żeby uniknąć efektu „wąskiego gardła” w dostępie do zawartości pamięci Flash, producenci stosują różne rozwiązania: w mikrokontrolerach STM32 pobieranie danych z pamięci Flash jest buforowane za pomocą sprzętowego akceleratora ART (Adaptive Real-Time). Jego działanie polega m.in. na dekompozycji 128-bitowych słów przechowywanych w pamięci Flash na słowa 16- lub 32-bitowe (rysunek 2), które są kolejkowane w lokalnej (wbudowanej w ART) pamięci cache. Według informacji publikowanych przez producenta, mechanizmy usprawniające dostęp do zawartości Flash spowodowały, że nie ma konieczności używania podczas odczytu wait-state’ów dotychczas istotnie zmniejszających realną prędkość transferu danych.

Rys. 2. Budowa i ilustracja działania akceleratora ART

Producent opracowując mikrokontrolery STM32F7 zadbał o wyposażenie ich w bogaty zestaw elementów peryferyjnych, w skład którego wchodzą wszystkie interfejsy znane z poprzednich generacji mikrokontrolerów oraz kilka nowych rozwiązań, w tym m.in.:

- zmodyfikowany podsystem generacji sygnałów zegarowych, pozwalający na modyfikację częstotliwości taktowania bloków peryferyjnych bez konieczności zmiany ustawień taktowania CPU,

- dwukanałowy transceiver I2S z obsługą SPDIF oraz 3 półdupleksowe kanały wejściowe SPDIF, interfejsy USB-OTG z wydzielonym zasilaniem, co pozwala korzystać z tego interfejsu także przy zasilaniu mikrokontrolera napięciem 1,8 V,

- dwa interfejsy QSPI, które sprzętowo realizują transmisję danych z pamięciami wyposażonymi w 1-, 4- lub 8-bitowe interfejsy komunikacyjne.

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii