[4] [Smart IoT] SAM L21 – 32-bit Cortex-M0+

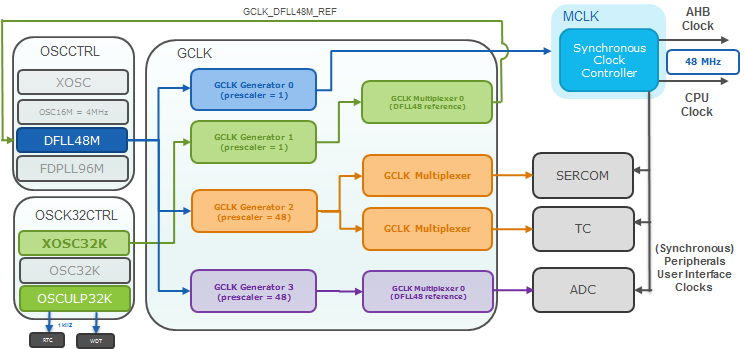

Budowa zegara

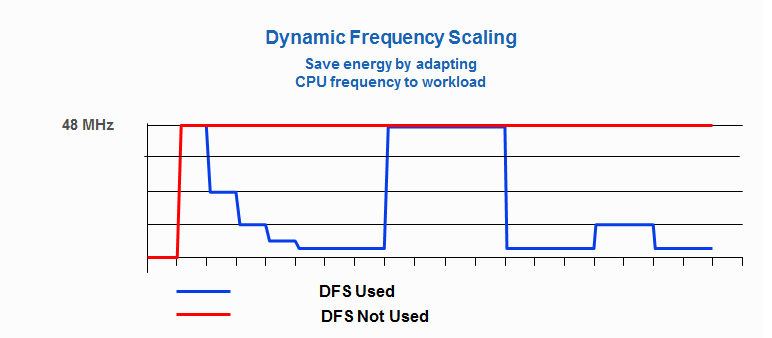

Kolejny element architektury, który został wykonany w nieco inny sposób, to budowa systemu zegara. Znajduje się tu do dziewięciu generator/clock domain, które mogą być konfigurowane oraz przełączane niezależnie przez system bądź użytkownika. Pozwala to na dużą elastyczność taktowania poszczególnych peryferiów, zwłaszcza w stanach uśpienia. A sam CPU może pracować z różną częstotliwością w zależności od wymagań aplikacji (Dynamic Frequency Scaling).

Rys. 5. Budowa zegara w SAM L21

Rys. 6. Dynamic Frequency Scaling

Źródło taktowania może pracować także w trybie on-demand (flaga ONDEMAND). Oznacza to, że jest ono automatycznie zatrzymywane, w przypadku gdy nie jest ono potrzebne, a potem automatycznie włączane, gdy jego praca jest wymagana.

System eventów

Kolejnym elementem, który, odpowiednio wykorzystany może znacząco wpłynąć na sumaryczne zużycie energii jest system eventów. Wielu inżynierów zna go doskonale z układów serii Atxmega. Teraz został on zaimplementowany także w układach z Cortex-M0+.

Event system pozwala na współdziałanie peryferiów bez udziału CPU. Dodatkowo ma bardzo ciekawą właściwość. Otóż czas reakcji na event jest w 100% przewidywany. Poniżej graf obrazujący współdziałanie wybranych peryferiów bez udziału CPU.

Rys. 7. System eventów

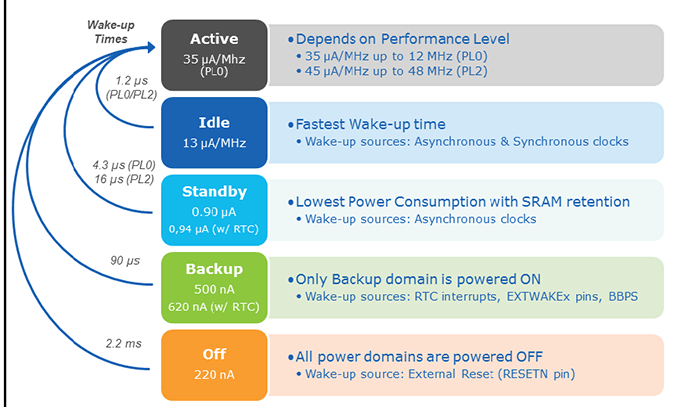

Stany uśpienia

W ramach rodziny SAML21 wprowadzono możliwość wprowadzania mikrokontrolera w jeden z kilku stanów uśpienia. Poniższy graf przedstwia przybliżone pobory prądów oraz czasy wybudzeń do stanu aktywnego. Można odczytać także źródła, które są w stanie wybudzić układ z danego stanu uśpienia.

W trybie active CPU wykonuje kod, wszystkie zegary są dostępne, a pobór prądu zależy w dużej mierze od Performance Level (PL). SAML21 może pracować w jednym z dwóch performance level. Gdy pracuje w najniższym, czyli PL0, napięcie zasilania logiki jest redukowane, i jego poziom jest dostosowywany w zależności od częstoliwości pracy. W przypadku PL2 regulator napięcia dostarcza najwyższe możliwe napięcie, pozwalając na pracę z maksymalną częstotliowścią. Zmiany PLx można dokonywać w trakcie pracy mikrokontrolera. W trybie Idle zegar CPU jest wyłączony, różnie AHBx oraz APBx są wyłączone, ale mogą zostać uruchomione jeśli któreś z peryferiów będzie tego wymagać.

W trybie Standby wszystkie zegary, oprócz ULP32K sa wyłączone. Jednak peryferia mogą realizować swoje zadania, jeśli w rejestrze konfiguracyjnym danego peryferia ustawiono flagę RUNSTDBY. Dodatkowo można tę pracę powiązać ze wcześniej wspomnianym ustawieniem flagi ONDEMAND, która decyduje o pracy źródła taktowania. W trybe Backup zasilana jest tylko domena BACKUP, do której, między innymi, należy RTC, BOD.

Rys. 8. Stany uśpienia

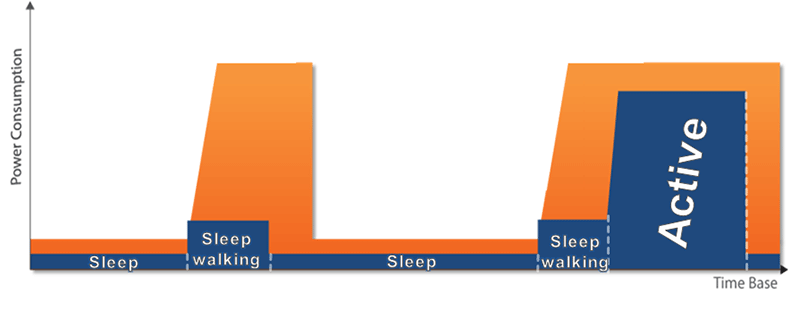

SleepWalking

Kolejną funkcjonalnością przeniesioną z AVR jest SleepWalking. Funkcjonalność ta daje możliwość, aby wybrane peryferia mogły wysłać żądanie wystawienia sygnału zegara, aby wykonać zadanie bez udziału CPU, w trybie Standby. W przypadku SAML21 zostało to wzbogacone o współpracę z power domain. Oznacza to, że zasilanie do danej power domain będzie dostarczone, gdy któryś z elementów tego potrzebuje do pracy. Kiedy zadanie jest wykonane, mikrokontroler może zostać wybudzony do stanu aktywnego, bądź tez pozostać w Standby, tak jak pokazuje to poniższy rysunek.

Rys. 9. SleepWalking

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii