Altera MAX10 – przyjazne FPGA z bezpłatnym środowiskiem projektowym

Układy FPGA z rodziny Altera MAX10 są tanimi platformami sprzętowymi o cechach układów SoC (System-on-Chip), w których – dzięki dużym i przemyślanym zasobom logicznym – można zintegrować nie tylko własną „logikę” ale także kompletny 32-bitowy mikrokontroler…

Produkowane przez Alterę układy FPGA z rodziny MAX10 są dostępne na rynku od kilku miesięcy, pojawiły się już także zestawy ewaluacyjne i startowe z tymi układami. Nazwa rodziny – MAX10 – sugeruje przynależność prezentowanych układów do grupy CPLD (Complex Programmable Logic Devices), podobnie jak starsze układy – MAX V, MAX II czy MAX7000. O klasyfikacji do grup CPLD lub FPGA decyduje budowa wewnętrzna układów PLD, dlatego układy Altera MAX10 określamy mianem (podobnie jak producent) FPGA, raczej słusznie odbierając podprogową sugestię, że prefiks MAX w nazwie ma za zadanie poinformować użytkowników, że układy Altera MAX10 należą do rozwiązań przystępnych pod względem kosztów.

W odróżnieniu od dotychczas produkowanych przez Alterę układów FPGA, rodzina Altera MAX10 cechuje się kilkoma nowatorskimi rozwiązaniami, które ułatwią ich aplikowanie w rozwiązaniach, w których istotna jest miniaturyzacja, ograniczenie poboru mocy i ochrona własności intelektualnej zaimplementowanej w projekcie.

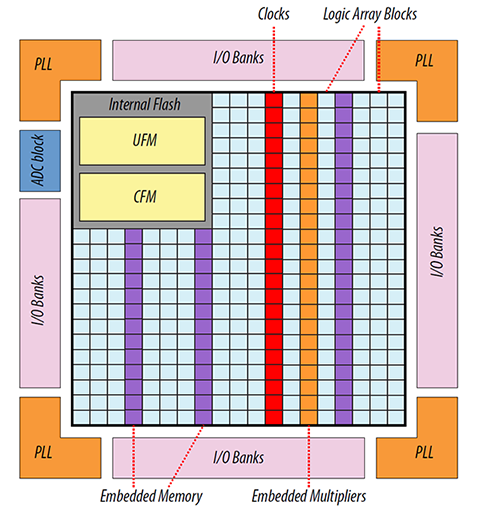

Rys. 1. Ogólny schemat blokowy układów Altera MAX10

Schemat blokowy układów Altera MAX10 pokazano na rysunku 1. Ich architektura bazuje na promowanej przez Alterę „Generacji 10”, przy czym po uważnym przejrzeniu szczegółów wyraźnie widać, że większość rozwiązań twórcy prezentowanych układów zaczerpnęli z popularnych, dobrze zweryfikowanych na rynku, układów Cyclone IV. Na schemacie widać, że poza klasycznymi zasobami powszechnie implementowanymi w FPGA różnych producentów, układy MAX10 wyposażono w elementy rzadko spotykane:

- wbudowany przetwornik ADC,

- wewnętrzną pamięć Flash.

Wymienione elementy – w połączeniu z dużymi zasobami konfigurowalnymi – nadające układom Altera MAX10 cechy SoC. Dzięki wbudowaniu w Altera MAX10 pamięci Flash nie wymagają one zewnętrznej pamięci konfigurującej, co obniża koszt wykonania urządzenia, zmniejsza jego wymiary i minimalizuje ryzyko nieuprawnionego dostępu do zawartości pamięci Flash (np. w celu pobrania konfiguracji układu FPGA). Stało się tak dzięki zintegrowaniu pamięci nieulotnej Flash-NOR ze strukturą rekonfigurowalną. Pamięć ta jest podzielona na dwa podstawowe obszary, widoczne na rysunku 1:

- pamięć konfigurującą CFM, w której jest przechowywany obraz konfiguracji FPGA. Większość dostępnych typów układów z serii Altera MAX10 (poza tymi o najmniejszych zasobach logicznych – patrz tabela 1) wyposażono w dwa banki wewnętrznej pamięci konfiguracyjnej, dzięki czemu można dokonywać błyskawicznej „rekonfiguracji” sprzętu, bez konieczności zatrzymywania pracy całego systemu.

- pamięć Flash dla aplikacji użytkownika (UFM – User Flash Memory), dostępna w układzie za pośrednictwem magistrali Avalon Memory-Mapped, o maksymalnej pojemności dochodzącej do niemal 6 Mb. Pamięć ta może być używana jako równoległa z taktowaniem do 116 MHz i maksymalnej szerokości słowa 32 bity lub jako szeregowa, z maksymalną częstotliwością taktowania wynoszącą ok. 7,25 MHz.

Tab. 1. Zestawienie najważniejszych cech poszczególnych typów układów MAX10

| Zasoby | Typ układu | |||||||

| 10M02 | 10M04 | 10M08 | 10M16 | 10M25 | 10M40 | 10M50 | ||

| Liczba elementów logicznych (LE) [x1k] |

2 |

4 |

8 |

16 |

25 |

40 |

50 |

|

| Pojemność pamięci RAM użytkownika M9K [kb] |

108 |

189 |

378 |

549 |

675 |

1260 |

1638 |

|

| Pojemność pamięci Flash UFM [kb] |

96 |

1248 |

1376 |

2368 |

3200 |

5888 |

5888 |

|

| Liczba multiplikatorów 18×18 |

16 |

20 |

24 |

45 |

55 |

125 |

144 |

|

| Liczba PLL |

2 |

2 |

2 |

4 |

4 |

4 |

4 |

|

| Maksymalna liczba GPIO |

160 |

246 |

250 |

320 |

360 |

500 |

500 |

|

| LVDS | Dedykowane nadajniki |

9 |

15 |

15 |

22 |

24 |

30 |

30 |

| Nadajniki emulowane |

73 |

114 |

116 |

151 |

171 |

241 |

241 |

|

| Dedykowane odbiorniki |

73 |

114 |

116 |

151 |

171 |

241 |

241 |

|

| Liczba pamięci konfiguracji Flash |

1 |

2 |

2 |

2 |

2 |

2 |

2 |

|

| Liczba przetworników ADC |

– |

1 |

1 |

1 |

2 |

2 |

2 |

|

| Kontroler EMIF |

SRAM |

SRAM |

SRAM |

SRAM, DDR3-SDRAM, DDR2-SDRAM, LPDDR2 |

SRAM, DDR3-SDRAM, DDR2-SDRAM, LPDDR2 |

SRAM, DDR3-SDRAM, DDR2-SDRAM, LPDDR2 |

SRAM, DDR3-SDRAM, DDR2-SDRAM, LPDDR2 |

|

Obydwie pamięci nieulotne są podzielone na sektory, które można programować niezależnie od siebie, co zwiększa ich trwałość, która i tak jest duża – producent deklaruje minimalna liczbę cykli kasowanie-zapis wynoszącą 10000 w pełnym zakresie temperatur oraz trwałość zapisanych danych nie krótszą niż 20 lat przy temperaturze otoczenia nie wyższej niż +85oC.

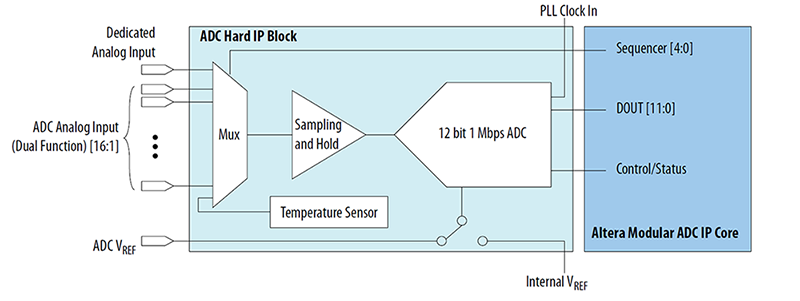

Wbudowane w układy MAX10 przetworniki ADC charakteryzują się rozdzielczością 12 bitów i częstotliwością próbkowania 1 MHz. Schemat blokowy ilustrujący budowę ADC pokazano na rysunku 2.

Rys. 2. Schemat blokowy ADC wbudowanego w układy MAX10

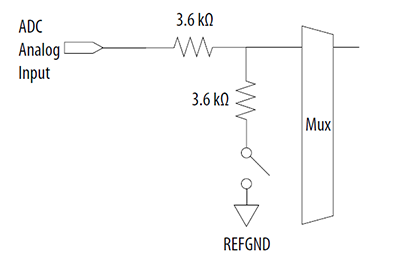

W zależności od wersji układu i zastosowanej obudowy, są one wyposażone w jeden lub dwa przetworniki ADC (SAR), o łącznej liczbie kanałów wejściowych wynoszącej maksymalnie 18. Układy są wyposażone w jedno lub dwa dedykowane wejścia analogowe, pozostałe linie wejściowe mogą być wykorzystywane z puli uniwersalnych I/O. Sygnał taktujący ADC jest generowany przez zdefiniowane przez producenta (pośród dostępnych w danym typie układu) wewnętrzne syntezery z PLL. Interesującym zabiegiem producenta, praktycznie niespotykanym w rozwiązaniach konkurencyjnych, jest wyposażenie kanałów wejściowych w programowany dzielnik napięcia, który umożliwia pomiar napięć o wartości – teoretycznie – dwukrotnie większej niż napięcie zasilania ADC (rysunek 3), w praktyce napięcie wejściowe ADC nie może być wyższe niż 3,6 VDC w układach zasilanych pojedynczym napięciem (z wbudowanym stabilizatorem zasilającym rdzeń FPGA). Przetwornik wyposażono ponadto w półprzewodnikowy (diodowy) czujnik temperatury, który jest dołączony do jednego z wejść przetwornika ADC. Podczas pomiaru temperatury przetwornik domyślnie jest taktowany sygnałem zegarowym o częstotliwości 50 kHz.

Rys. 3. Budowa linii wejściowej przetwornika ADC w układach MAX10

Rys. 4. Schemat blokowy interfejsu pamięci zewnętrznej EMIF wbudowanego w układy MAX10

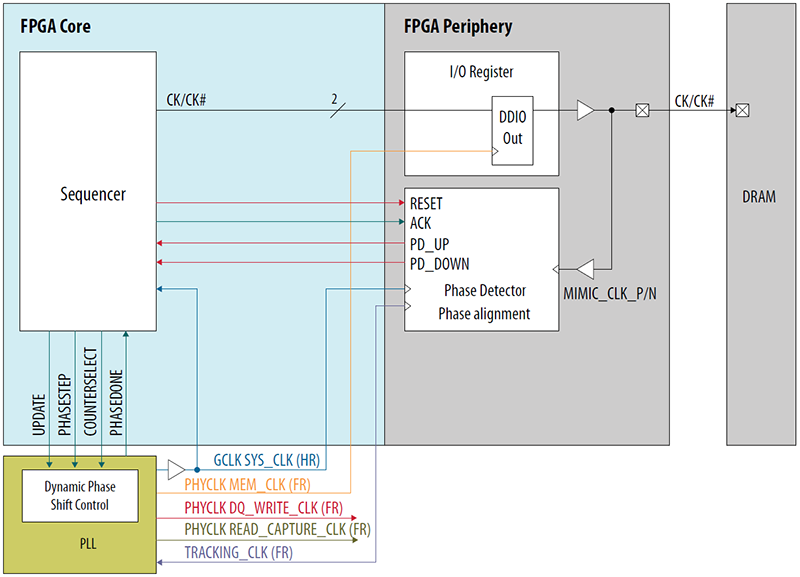

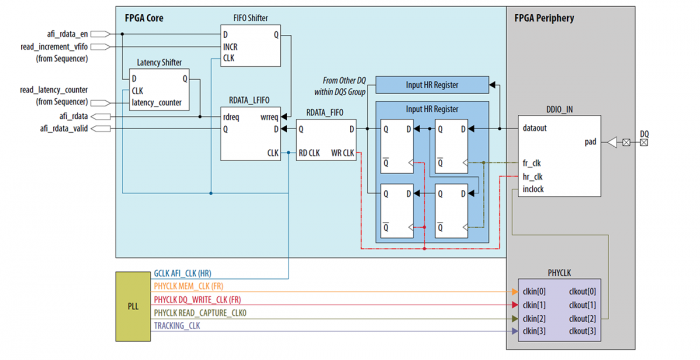

Kolejną rzeczą, na którą warto zwrócić uwagę w układach MAX10, jest wbudowana warstwa sprzętowa interfejsu zewnętrznej pamięci (EMIF, rysunek 4), który w trzech najmniejszych układach z rodziny obsługuje pamięci SRAM, w pozostałych także pamięci SDRAM: DDR3, DDR2 i LPDDR2. Ze względu na dużą częstotliwość taktowania interfejsu pamięci zewnętrznej (do 303 MHz w przypadku pamięci DDR3/DDR3L), producent przewidział możliwość dynamicznej modyfikacji fazy sygnału taktującego, która jest sprzętowo modyfikowana w zależności od napięcia zasilającego i temperatury w taki sposób, aby zminimalizować straty czasu podczas cykli zapisu/odczytu danych. Schemat blokowy układu korekcji fazy sygnału zegarowego pokazano na rysunku 5.

Rys. 5. Schemat blokowy systemu korekcji sygnału zegarowego taktującego interfejs zewnętrznej pamięci dołączanej do układów MAX10

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii