[7] [Smart IoT] W walce o wydajność – układy z Cortex-M7

Układy z Cortex-M7 są stosowane wszędzie tam, gdzie wymagana jest duża wydajność mikrokontrolera, większa niż zapewniana przez Cortex-M0+, m.in. w bramach komunikacyjnych, translatorach protokołów, centralkach systemów zarządzania. Do tego typu produktów Atmel rekomenduje stosowanie nowych, bardzo wydajnych serii SAM S70 oraz SAM E70, pracującej w oparciu o Cortex-M7. Odpowiednikiem tych platform, dedykowanym na rynek automotive są rodziny SAM V70 oraz SAM V71.

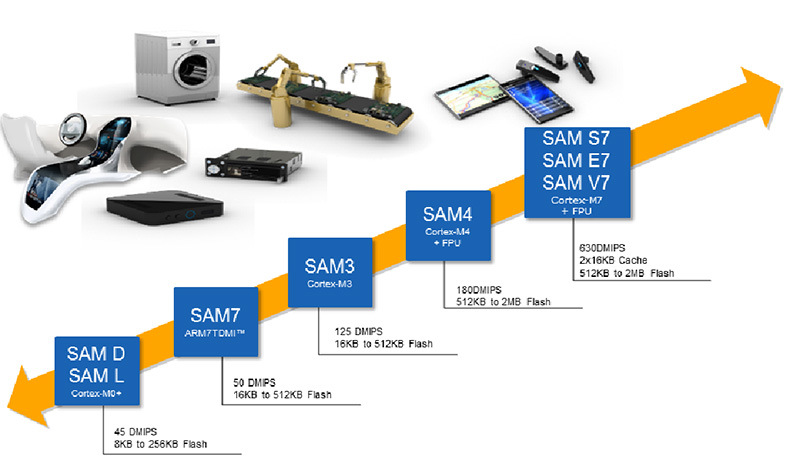

Rys. 1. Podział mikrokontrolerów ze względu na wydajność rdzeni

Cortex-M7 dołącza do innych rdzeni od ARM, zastosowanych przez Atmel w swoich mikrokontrolerach. Układy pracują z częstotliwością 300MHz osiągają wynik 1500 CoreMarks. Dostępne jest DSP oraz double precision FPU (Floating Point Unit).

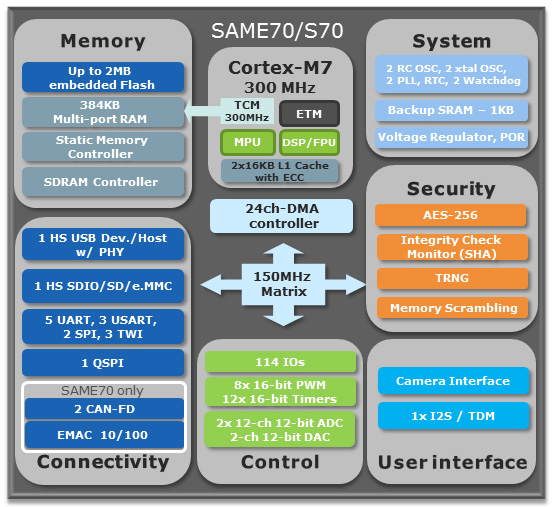

Rys. 2. Schemat blokowy serii SAME70/S70

Poniższy diagram prezentuje blokowa budowę serii SAM E70. Układy z SAM S70 mają bardzo zbliżoną budowę, brakuje tam jedynie bloków z CAN oraz Ethernet.

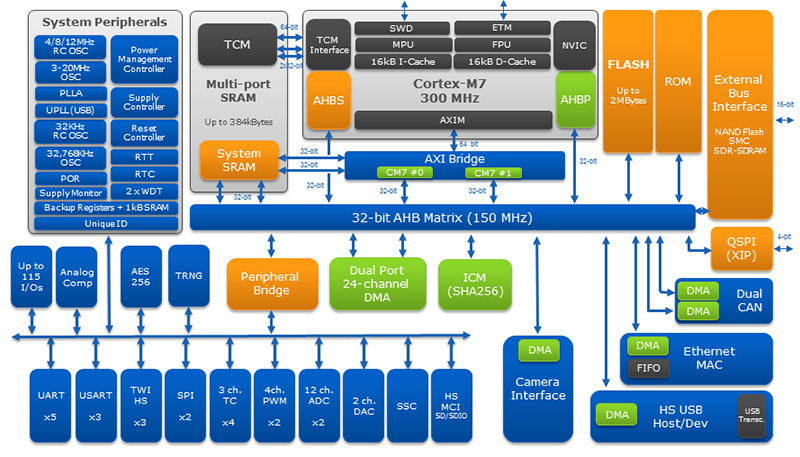

Rys. 3. Budowa serii SAM E70

Jak widać dostępna jest wbudowana pamięć flash, do 2 MBytes. Dostępne są także interfejsy QSPI (Quad SPI), gdzie podłączona może być zewnętrzna, dodatkowa pamięć flash. A także EBI 16-bit (External Bus Interface), z wbudowanymi Static Memory Controller oraz SDR-SDRAM Controller. Zaimplementowano także pamięć ROM, gdzie znajduje się bootloader SAM-BA (SAM Bootloader Assistant), który daje możliwość przeprogramowania pamięci flash z wykorzystaniem interfejsu UART lub USB. Dostępne jest także 1kB pamięci backup SRAM.

W normalnym trybie pracy pamięć ta zasilana jest z VDDCORE, w trybie backup zasilanie przełączane jest automatycznie na VDDIO.

Rozbudowana pamięć SRAM

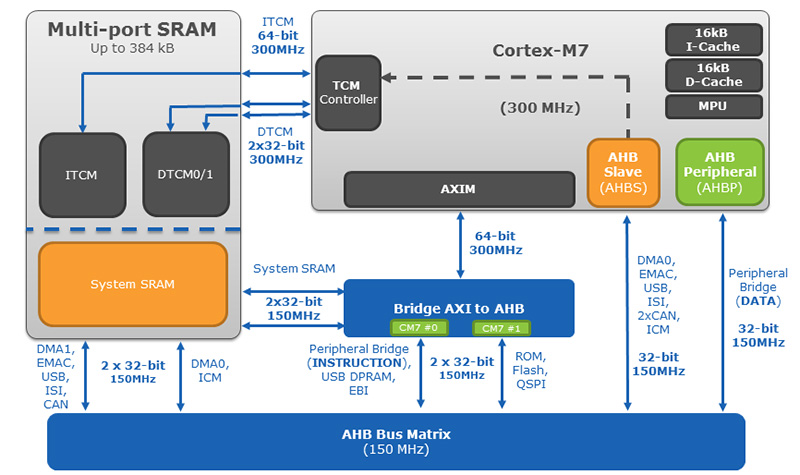

Programista ma także do dyspozycji do 384kB pamięci SRAM. Ten fragment architektury został bardzo rozbudowany. Z pamięci tej korzystać może zarówno system jak i interfejs TCM (Tightly Coupled Memory), co pozwala na wykonywanie kodu deterministycznego oraz szybką obróbkę danych. Kod z TCM wykonywany jest z pełną szybkością 300MHz. Pamięć SRAM ma wyprowadzone cztery interfejsy, dwa dedykowane dla rdzenia Cortex-M7 oraz dwa dostępne poprzez AHB Bus Matrix, gdzie podłączyć się mogą peryferia. Taka budowa ma optymalizować przepustowość oraz minimalizować opóźnienia.

Rys. 4. Budowa pamięci SRAM

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii