Akcelerator grafiki 2D na FPGA i STM32F429

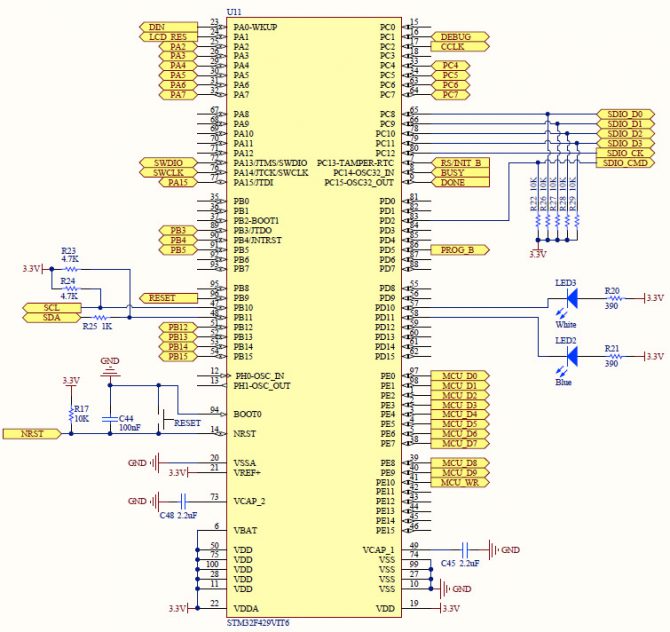

Mikrokontroler

Mikrokontroler jest w tym projekcie uzupełnieniem FPGA. Łatwo jest zauważyć przeciwne końce niektórych linii sygnałowych. Przykładowo, przypisałem całą 10-bitową szynę danych i sygnał WR do portu E.

Dzięki temu będę mógł ustawić dane oraz sygnał strobujący WR w jednej operacji zapisu do portu. Przycisk reset jest tylko po to, abym w razie potrzeby mógł ponownie uruchomić płytkę.

Sygnały SDIO są zmapowane do wyjść peryferyjnych SDIO mikrokontrolera, co pozwala łatwo zapisywać i odczytywać karty SD. Sygnały SCAl i SDA interfejsu I2C są podłączone do układu peryferyjnego I2C#2 mikrokontrolera. Przeznaczyłem dwie diody LED do sygnalizowania statusu i innych funkcji ogólnego przeznaczenia. 18 spośród pinów GPIO jest wyprowadzonych na zewnętrzne gniazdo wyjściowe, dzięki czemu mogę w celach testowych podłączyć urządzenia peryferyjne, takie jak joystic. Wyprowadzone piny nie są przypadkowe – zostały wybrane tak, aby móc obsłużyć różne układy peryferyjne umieszczone na płytce, które mogłyby być przydatne na etapie projektowania.

Można zauważyć brak oscylatora – ten mikrokontroler go nie potrzebuje. Jeśli tylko dokładność 1% jest dopuszczalna, można wykorzystać wewnętrzny zegar dużej szybkości (HSI) 16 MHz doprowadzony do pętli PLL, która generuje zegar 180 MHz taktujący rdzeń. Tolerancja 1% moim zdaniem jest wystarczająca, zatem używam HSI.

W odróżnieniu od skomplikowanych wymagań zasilania FPGA, zasilanie mikrokontrolera jest bardzo proste. Odsprzężenie (nie pokazane na obrazku) jest zgodne z wytycznymi ST – ceramiczny kondensator dla każdego wyprowadzenia i dodatkowy kondensator „chemiczny” 4,7 uF. Kondensatory elektrolityczne zaliczają się do chemicznych, zatem takich użyłem. Osobiście preferuję tantalowe ze względu na ich niską rezystancję szeregową, ale nie miałem akurat żadnego pod ręką.

Debugowanie i programowanie odbywa się przez interfejs SWD, dwuprzewodowy protokół zaprojektowany jako bardziej efektywny następca JTAG. Sygnały SWDIO i SWCLK są wyprowadzone na złącze debugujące, dzięki czemu można je podłączyć bezpośrednio do taniego i skutecznego debuggera ST-Link/v2.

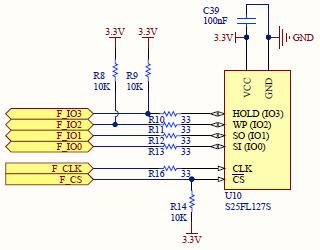

Pamięć Flash

Pamięć Flash to najszybszy układ peryferyjny na tej płytce, który będzie pracował z częstotliwością zegara 100 MHz. W tym zakresie mogą zdarzyć się problemy z integralnością sygnałów spowodowane przez przestrzały lub zbyt niski poziom sygnału, odbicia, a nawet wszystkie te zjawiska naraz – jeśli nie będę ostrożny. Z tego powodu wszystkie linie wejścia/wyjścia i linie zegara mają szeregowy rezystor terminujący 33 Ω, który ma tłumić odbicia, zanim będą w stanie popsuć sygnał użyteczny. Te linie będą również bardzo krótkie na płytce PCB.

Skąd wynika wartość 33 Ω? Niestety, to tzw. reguła kciuka. Nie mam żadnego przyrządu, który pozwalałby zmierzyć i wybrać odpowiednią wartość, więc zaczynam od 33 Ω. Jeśli pojawią się problemy, wyciągnę podręczny oscyloskop i ocenię, czy rezystancję należy zwiększyć.

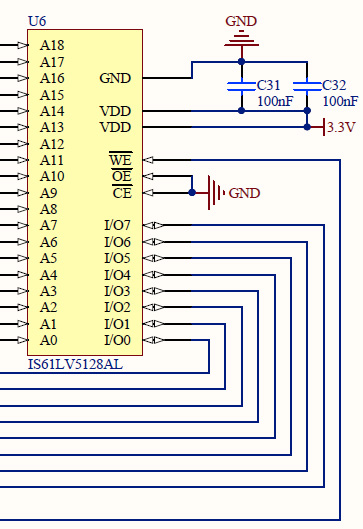

Pamięć SRAM

Układy pamięci nie są zbyt interesujące. To jedynie dwie szyny, kilka sygnałów sterujących i zasilanie. Aby oszczędzić wyprowadzenia, podłączyłem piny CS oraz OE bezpośrednio do masy – według dokumentacji jest to dozwolone. Muszę jedynie sterować sygnałem WE, gdy chcę zapisać dane.

Linie adresu i danych będą się zmieniały co najwyżej z częstotliwością 50 MHz, ale linia WE będzie przełączana z częstotliwością 100 MHz. Nie przejmuję się liniami adresowymi ani danych, dopóki będą one krótkie i pozbawione przelotek – przy 50 MHz nie powinny sprawiać problemów. Po dłuższym namyśle doszedłem do wniosku, że powinienem zostawić chociaż miejsce na rezystor terminujący 33 Ω na linii WE. Gdybym miał okazję tworzyć nową wersję płytki, zrobiłbym to.

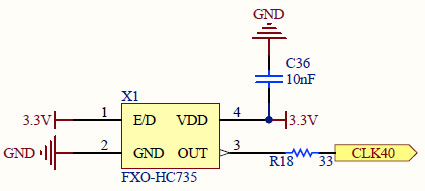

Oscylator

Oscylatora nie trzeba uruchamiać zewnętrznym układem – zacznie on sam pracować w momencie, gdy zostanie zasilony. W moim projekcie umieściłem rezystor terminujący 33 Ω również na linii zegara, choć to zapewne przesada. Zegar jest krytycznym elementem i zapewnia działanie całej reszty systemu, zatem warto przewidzieć dodatkowe zabezpieczenie.

Ekran LCD

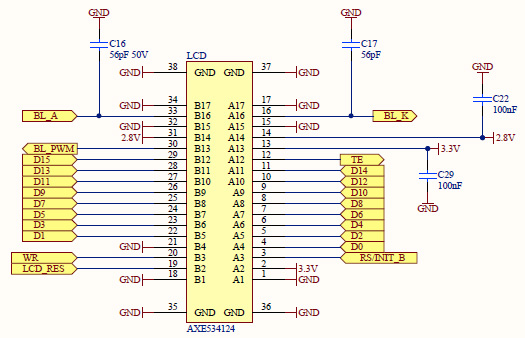

Schemat podłączenia ekranu LCD powinien być znajomy dla każdego, kto czytał moje artykuły dotyczące inżynierii wstecznej lub halogenowego pieca lutowniczego.

Wszystkie sygnały kontrolne są podłączone do FPGA – poza LCD_RES, który jest sygnałem resetującym sterowanym przez mikrokontroler. Nie ma sensu obciążać układu FPGA obsługą sekwencji resetującej wyświetlacz, tym zadaniem najlepiej zajmie się mikrokontroler.

Podświetlenie LED

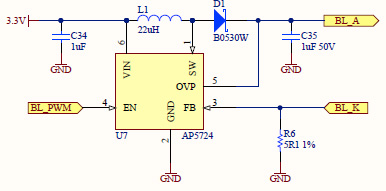

Podświetlenie ekrany LED składa się z sześciu białych diod LED połączonych szeregowo. Do ich zasilania potrzebna jest przetwornica podwyższająca napięcie, która uzyska poziom odpowiadający sumie spadków napięć na poszczególnych diodach LED.

Układ AP5724 firmy Diode Inc. Jest dedykowanym sterownikiem podświetlenia pracującym w trybie prądowym, który zawiera przetwornicę podwyższającą napięcie. Wystarczy dodać kilka zewnętrznych elementów, takich jak opornik służący do pomiaru prądu, a sterownik zapewni stabilny prąd wyjściowy tak długo, jak pin EN jest w stanie wysokim. Zaletą tego rozwiązania jest brak potrzeby dostarczania sygnału z modulacją PWM do wejścia EN, aby kontrolować jakość podświetlenia – ponieważ ekran LCD ma funkcję, która robi to za nas. Takie rozwiązanie pozwala zaoszczędzić jedno wyprowadzenie i układ czasomierza mikrokontrolera.

Zatrzask

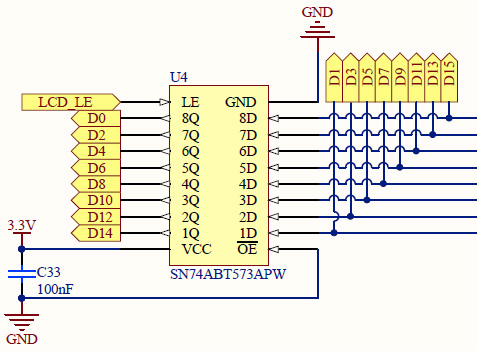

Zatrzask jest umieszczony między FPGA a wyświetlaczem LCD, pozwalając za pomocą 8 pinów FPGA wysterować 16-bitową magistralę.

Gdy sygnał LE jest w stanie wysokim, zatrzask jest przezroczysty. Dane przechodzą z wejść D do wyjść Q. Kilka nanosekund po wyłączeniu sygnału LE zatrzask przestaje reagować na wejścia i wysterowuje wyjścia ostatnimi zapamiętanymi wartościami.

Trik polega na tym, aby zapisać bezpośrednio pierwszym 8 bitów danych, następnie zablokować zatrzask, po czym zapisać kolejnych 8 bitów. Jak wynika ze schematu, w wyniku tej operacji wszystkie 16 bitów zostanie poprawnie wysterowanych. Dodatkowo pomaga przy tym fakt, że FPGA pozwala na wystawienie dowolnego bitu na dowolnym wyjściu. Dzięki temu mogę dopracować projekt tak, aby linie danych biegły równolegle na płytce PCB bez żadnych przelotek.

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii