Nanocounter – dokładny miernik częstotliwości wykorzystujący układy FPGA, STM32 oraz aplikację Android

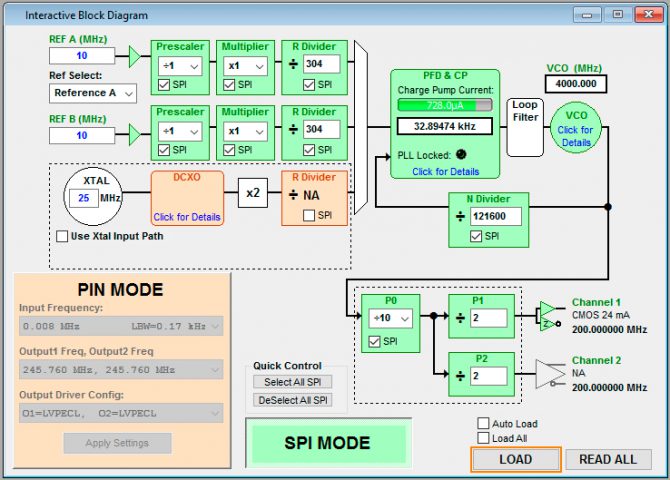

Alternatywna dla SPI są piny Ax oraz Yx pozwalają wybrać na stałe jedną z gotowych konfiguracji AD9553. Zwarcie wszystkich pinów do masy oznacza wybranie interfejsu SPI jako aktywnego trybu konfiguracji i daje dostęp do większej liczby opcji. Układ AD9553 ma dwa oddzielne wejścia oraz pin pozwalający na wybór jednego z nich. Wykorzystują tą funkcję do podłączenia wbudowanego oscylatora TCXO oraz zewnętrznego źródła referencyjnego. Kolejne wyprowadzenie GPIO mikrokontrolera pozwala przełączać się między nimi.

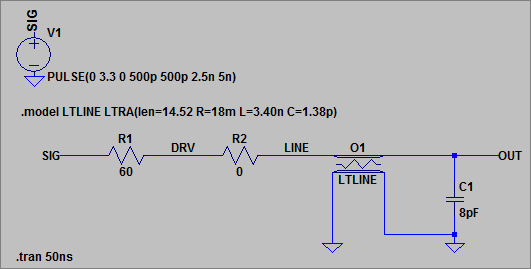

Wyjście sygnału LVCMOS o częstotliwości 200 MHz jest dołączone do pinu 27. Zostawiłem miejsce na płytce dla szeregowego rezystora terminujące na wypadek, gdyby trzeba było stłumić dzwonienie na wyjściu. Najlepszym sposobem sprawdzenia, czy pojawią się problemy z integralnością sygnału na wysokich częstotliwościach jest symulacja linii transmisyjnej za pomocą programu LTSPICE.

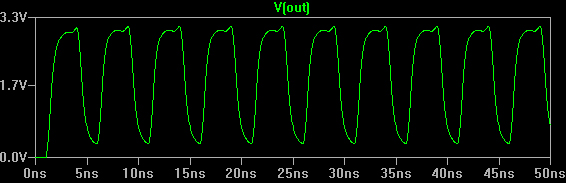

Przeprowadziłem symulację. Przewidywany kształt sygnału wyglądał dobrze, zatem opornik R8 pozostanie zwarciem. Elementy C29, C30 oraz R11 tworzą zewnętrzna część filtru pętli fazowej. Dobór odpowiednich wartości tych elementów jest opisany w karcie katalogowej AD9553, jednak znacznie lepiej jest użyć darmowego programu symulacyjnego dla AD9553 dostarczonego przez Analog Devices. Jest to dość skromna aplikacja, która ma swoje ograniczenia i czasami ulega awariom, ale zapewnia taką funkcjonalność, która pozwala wybaczyć jej wszystkie wady.

Trudność w projektowaniu filtra pętli PLL polega na doborze wartości kondensatorów i opornika z szeregu standardowego. Po spędzeniu długiego czasu z tym narzędziem wybrałem wartości widoczne powyżej. Miałem już wcześniej kupione oporniki 1800 Ω o tolerancji 1%, więc nietrudno było wybrać egzemplarz o niemal dokładnie pożądanej wartości.

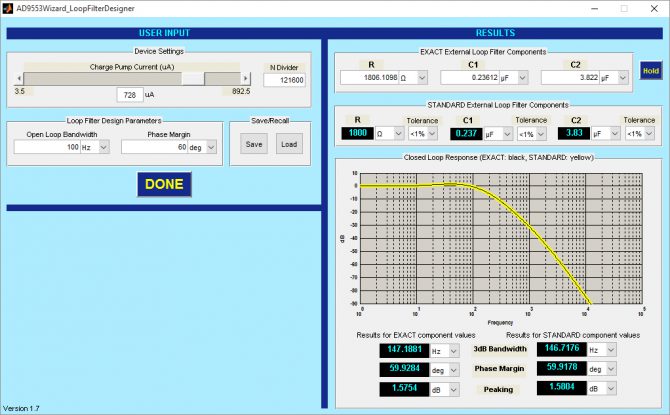

Z kondensatorami było trudniej. Najpierw wybrałem takie kondensatory X5R, które akurat miałem do dyspozycji, aby wartości dla filtru pętli wpadały w ich 20% zakres tolerancji. Spędziłem sporo czasu mierząc je, aż wybrałem ręcznie dwa bardzo zbliżone do wymaganych wartości. Przebrałem około 20 sztuk dla obu wartości 0,22 uF oraz 4,7 uF, zanim znalazłem egzemplarze mieszczące się w zakresie 1% od nominalnych wyznaczonych wartości. Gdy skończyłem, program do projektowania filtru pętli stworzył bardzo użyteczny interaktywny schemat blokowy:

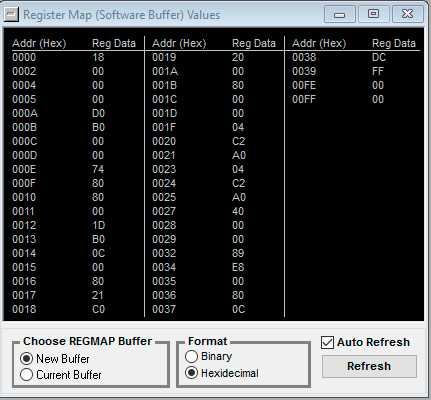

Ten interaktywny diagram zawiera wartości podane przez aplikację do projektowania filtru. Pozwala wprowadzić poprawki do konfiguracji wejścia i wyjścia, a następnie generuje odpowiednią konfigurację rejestrów programowanych przez SPI.

Trudno jest przecenić wartość tego narzędzia – Analog Devices należą się duże podziękowania za dostarczenie go, co pozwoliło zaoszczędzić godziny przeglądania kart katalogowych i not aplikacyjnych – oraz możliwość popełnienia błędów.

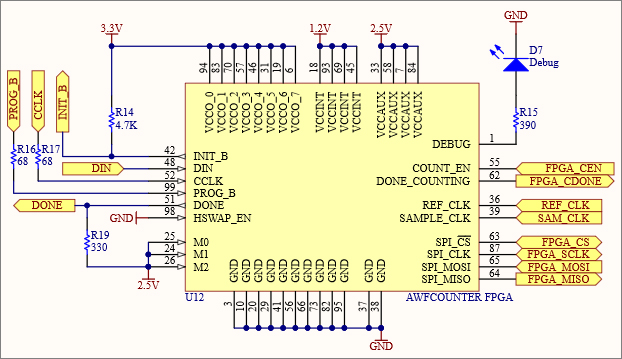

Układ FPGA

Wybrałem model FPGA Xilinx Spartan 3 XC3S50-5, aby zrealizować zasadniczy cel projektu – wysoką szybkość. Jest to starszy model, niż aktualna generacja Spartan 6, ale używałem jej już wcześniej w projekcie akceleratora grafiki FPGA. Ponadto mam ponad 400 sztuk i muszę je jakoś wykorzystać. Wcześniej kupiłem 450 nowych i nierozpakowanych sztuk na przecenie na Ebayu. Tak wyglądają:

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii