Nanocounter – dokładny miernik częstotliwości wykorzystujący układy FPGA, STM32 oraz aplikację Android

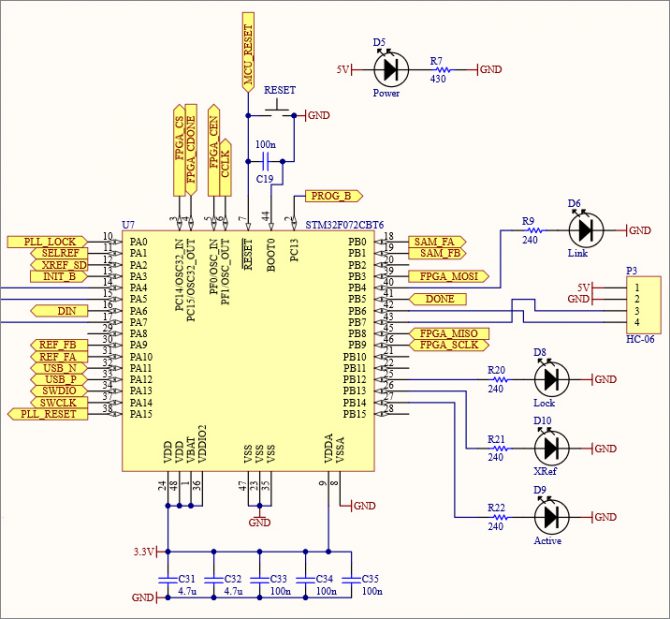

Liczba wejść/wyjść nie jest w tym projekcie problemem. Potrzebuję tylko dwóch wejść zegara oraz kilku linii sterujących dla mikrokontrolera: FPGA_CS, FPGA_SCLK, FPGA_MOSI i FPGA_MISO tworzą interfejs SPI umożliwiający komunikację z mikrokontrolerem.

Wejście FPGA_CEN uruchamia zliczanie od następnego zbocza narastającego. FPGA_CDONE jest sygnałem wyjściowym, który przechodzi w stan wysoki po zakończeniu bramkowania. Idea polega na tym, że mikrokontroler będzie używał interfejsu SPI do załadowania wartości licznika bramki i następnie ustawi wejście FPGA_CEN w stan wysoki. Gdy licznik dojdzie do 0, FPGA_CDONE przejście ze stanu niskiego do wysokiego, po czym mikrokontroler za pomocą interfejsu SPI odczyta dwie wartości liczników zliczających. FPGA przejdzie wówczas w stan oczekiwania do chwili, aż pojawi się kolejne zbocze narastające na wejściu FPGA_CEN.

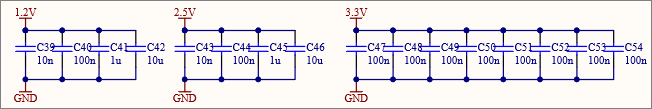

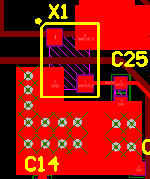

Stosuję się do zaleceń firmy Xilinx odnośnie odsprzęgania, co oznacza dość dużą liczbę kondensatorów, które trzeba umieścić w pobliżu układu.

To być może przesada, ale kondensatory są tanie i nie mam zamiaru testować systemu niestabilnego z powodu niewystarczającego odsprzęgania.

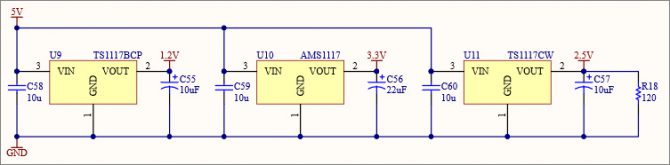

Ponieważ reszta płytki pracuje z napięciem 3,3 V, będę potrzebował trzech źródeł zasilania dla FPGA.

Zasilanie 1,2 V jest wykorzystywane przez wewnętrzne układy logiczne FPGA. Zasilanie 2,5 V to dodatkowe źródło, które służy głównie do optymalizacji różnych funkcji FPGA, jak przełączanie wejść i wyjść. Zasilanie 3,3 V jest przeznaczone dla sterowników sygnałów wyjściowych.

Ten model FPGA nie zachowuje projektu po wyłączeniu zasilania. Po włączeniu zasilania trzeba nieco się namęczyć z wyborem pinów programujących, aby załadować strumień bitów do rdzenia przez uruchomieniem układu. Piny INIT_B, DIN, CCLK, PROG_B oraz DONE po lewej stronie schematu służą do programowania FPGA i są obsługiwane przez mikrokontroler.

Tryb programowania, nazwany przez Xilinx „Slave Serial” jest nadzorowany przez mikrokontroler. Przechowuję plik programujący w pamięci Flash mikrokontrolera i wczytuję go do FPGA jako pierwszą czynność po resecie. Pewne problemy wynikają z faktu, że niektóre piny programujące FPGA używają napięcia referencyjnego 2,5 V i nie tolerują 3,3 V. Na szczęście Xilinx dostrzegł to ograniczenie i opublikował instrukcję programowania układu Spartan 3 za pomocą kontrolera z napięciem 3,3 V pod tytułem XAPP453.

Debugowanie pracującego FPGA jest ekstremalnie trudne, zatem staram się przeprowadzić symulację każdej funkcji, zanim zabiorę się za jakiekolwiek narzędzie do projektowania obwodu. Podłączyłem pin DEBUG do diody LED, która może służyć jako wskaźnik w przypadku debugowania w ostatniej chwili.

Mikrokontroler

Do realizacji projektu wybrałem model STM32F072CBT6 w obudowie LQPF z 48. wyprowadzeniami. Liczba dostępnych wejść / wyjść jest wystarczająco do potrzeb projektu. Model 072 zawiera 128 kB pamięci Flash i 16 kB SRAM. Duża pojemność pamięci Flash była kluczowym czujnikiem decydującym o wyborze, ponieważ pamięć musi pomieścić plik binarny FPGA, który zajmuje około 60 kB.

Przydatnym dodatkiem jest obsługa warstwy fizycznej USB dostępna w układzie. Podłączę linie danych USB na wypadek, gdybym chciał ich użyć w przyszłości. Podobnie do innych modeli F0, ten pracuje z zegarem 48 MHz i uzyskuje ten zegar z wewnętrznej pętli PLL napędzanej wbudowanych oscylatorem o częstotliwości 8 MHz.

Zastosowania większości linii wejścia/wyjścia jest jasne. Widoczne są wyprowadzenia sterujące FPGA, PLL oraz LTC6957, a także linie danych USB i wejścia programujące SWD. Zainstalowałem kompletne 20-pinowe złącze SWD, które będzie podłączone bezpośrednio do programatora ST-Link/v2.

Dostępnych jest kilka diod LED sygnalizujących status. Rola diody power jest oczywista. Dioda link będzie informowała o aktywności łącza Bluetooth. Dioda lock zaświeci się w momencie, gdy pętla PLL chwyci. Dioda xref będzie informować o wyborze zewnętrznego sygnału referencyjnego, a dioda active zaświeci się, gdy FPGA będzie aktywnie zliczać.

Łączność Bluetooth zapewnia tani i prosty w użyciu moduł HC-06, którego już używałem w tym projekcie.

Płytka HC-06 może połączyć się z urządzeniem z systemem Android bez pomocy mikrokontrolera. Gdy połączenie zostanie nawiązane, można je traktować jako prosty interfejs UART 9800/8/N/1.

Schemat płytki

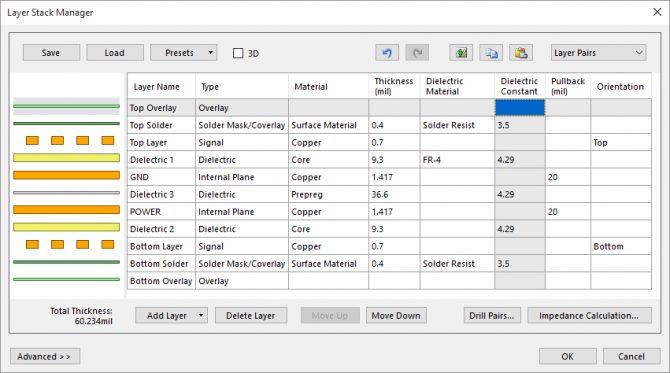

Po opracowaniu zadowalającego projektu układu czas zastanowić się nad schematem płytki. Zdecydowałem, że będzie to płytka czterowarstwowa o następującej strukturze:

Głównym powodem wyboru czterech warstw zamiast tańszego rozwiązania z dwiema warstwami jest obecność układów wysokich szybkości – zarówno analogowych, jak i cyfrowych. Chciałem uzyskać ciągłą i niezakłóconą płaszczyznę masy pod górną warstwą sygnałową, aby poprawić integralność sygnałową i móc kontrolować impedancję ścieżek. Plusem jest też prostsze prowadzenie ścieżek wokół FPGA oraz możliwość poprowadzenia wszystkich linii zasilania przez warstwę wewnętrzną.

Chcę skorzystać z usług produkcji prototypów takich firm, jak PCBWay, ITead, Seeed i podobnych. Muszę zatem ograniczyć wymiary płytki do 10 x 10 cm, ponieważ większe rozmiary oznaczają gwałtowny wzrost ceny w przypadku płytki czterowarstwowej.

Większość sygnałów, wliczając w to wszystkie 50 ścieżek o kontrolowanej impedancji, biegnie na górnej warstwie, natomiast dolna warstwa służy do prowadzenia dodatkowych sygnałów. Duże obszary wypełnione miedzią z wieloma przelotkami do płaszczyzny masy są umieszczone w pobliżu każdego z wrażliwym elementów, aby zapewnić ścieżkę do masy o niskiej impedancji i o niskim poziomie szumów.

Elementy cyfrowe – głównie FPGA i mikrokontroler – są tak rozmieszczone, aby ścieżki powrotne ich sygnałów przechodzące przez płaszczyznę masy nie przebiegały pod układami analogowymi. Co więcej, masa obudowy dla złączy BNC jest odizolowana od masy PCB.

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii