Pierwsze kroki z zestawem FPGA Lattice MachXO2 Pico Development Kit [1]

Sprzętowy blok funkcji wbudowanych

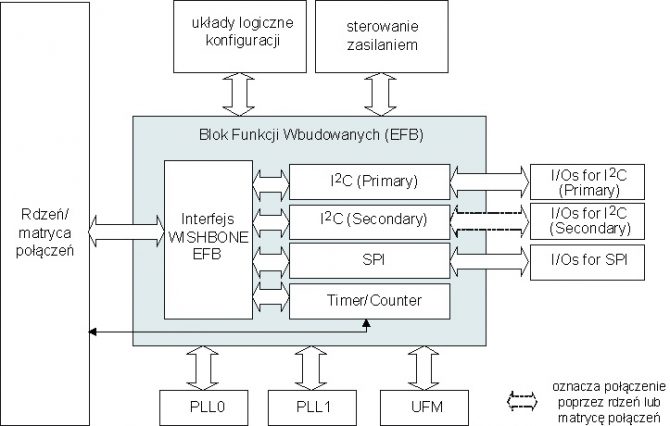

Wszystkie układy rodziny MachXO2 posiadają sprzętowy blok funkcji wbudowanych EFB. W ramach tego bloku dostępne są dwa kontrolery magistrali I2C, jeden kontroler SPI oraz układ czasowo/licznikowy (rysunek 6). Dodatkowo poprzez blok EFB można zmieniać ustawienia pętli PLL w czasie pracy systemu, uzyskać dostęp do pamięci konfiguracji Flash oraz pamięci użytkownika UFM a także sterować trybami oszczędzania energii. Komunikacja z blokiem EFB odbywa się poprzez standardowy interfejs Wishbone, który zostanie krótko omówiony w dalszej części kursu.

Każdy z dwóch dostępnych, w ramach bloku EFB, kontrolerów I2C charakteryzuje się następującymi właściwościami: praca zarówno jako układ Master jak i Slave, dostępne adresowanie 7- i 10-bitowe, wsparcie dla arbitrażu w sytuacji gdy na magistrali pracuje więcej układów typu Master, wydłużanie okresu sygnału zegarowego w przypadku współpracy z wolniejszymi układami I2C, maksymalna szybkość przesyłu danych wynosząca 400 kHz. Pierwszy kontroler I2C współpracuje z dedykowanymi końcówkami zewnętrznymi układu PLD, podczas linie magistrali drugiego kontrolera mogą być dowolnie konfigurowane przez użytkownika. Kontroler SPI również może pracować w trybach Master oraz Slave, zapewnia w pełni dupleksowy transfer danych, umożliwia pracę w trybie z sygnalizacją błędu (możliwość zgłoszenia przerwania do CPU), ma podwójnie buforowany rejestr danych, dysponuje możliwością programowania polaryzacji oraz fazy sygnału zegarowego oraz umożliwia transfer danych z bitem LSB lub MSB jako pierwszym.

Z kolei układ czasowo licznikowy może m. in. spełniać funkcje: układu dozorującego typu watchdog, szybkiego generatora PWM, źródła sygnału zegarowego o programowanej częstotliwości oraz źródła sygnału przerwania (przeładowanie licznika, osiągnięcie określonej wartości zliczeń).

Inne właściwości układów MachXO2

Układy MachXO2 charakteryzują się również możliwością podłączenia do systemu bez wyłączania zasilania (hot socketing, hot-swapping). Wynika to ze szczególnego sposobu projektowania zapewniającego przewidywalne zachowanie układu w czasie włączenie i zaniku zasilania. Inną cechą jest wbudowany oscylator CMOS, który może być źródłem częstotliwości taktującej. Ma on dokładność na poziomie 5% i częstotliwość wybieraną spośród kilkudziesięciu predefiniowanych wartości (inną częstotliwość można uzyskać wykorzystując pętlę PLL). Dodatkowo każdy egzemplarz układów MachXO2 został wyposażony w unikalny 64-bitowy numer seryjny (TraceID), przy czym 8 bitów tego kodu może być zaprogramowanych przez użytkownika. Odczyt kodu możliwy jest poprzez blok EFB i interfejs Wishbone.

Konfiguracji układów PLD MachXO2 można dokonać na kilka sposobów: poprzez wewnętrzne (przez blok EFB) zaprogramowanie pamięci Flash, przez interfejs JTAG oraz poprzez interfejsy SPI i I2C bloku EFB. Podczas procesu rozruchu systemu (włączenia zasilania) lub w odpowiedzi na polecenie przesłane interfejsem JTAG zawartość pamięci konfiguracji Flash jest kopiowana do komórek pamięci SRAM odpowiadającej bezpośrednio za konfigurację logiki programowalnej układu PLD. Poprzez interfejs JTAG możliwy dostęp zarówno do pamięci konfiguracji Flash jak i do pamięci SRAM. Zapewniona jest również ochrona przed nieuprawnionym odczytem obydwu pamięci (security and one-time programmable mode).

Lattice oferuje także opracowaną przez siebie technologię TransFR (Transfer Field Reconfiguration) umożliwiającą wymianę konfiguracji logiki bez przerywania pracy systemu (w rzeczywistości technologia minimalizuje czas i skutki przerwania pracy systemu). Wykorzystuje ona fakt, że pamięć konfiguracji Flash może być programowana w dowolnym momencie przez zewnętrzny interfejs JTAG. Przed skopiowaniem zawartości Flash do komórek pamięci SRAM, wejścia/wyjścia układu PLD przełączane są w bezpieczny stan zdefiniowany przez użytkownika, następnie kopiowana jest zawartość pamięci (odbywa się właściwa konfiguracja) i system wznawia pracę.

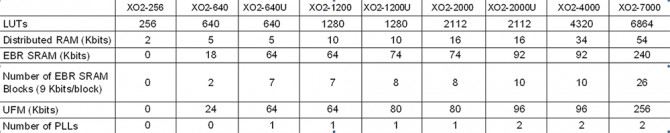

Tab. 1. Rodzina układów MachXO2

Rodzina MachXO2 obejmuje w sumie 6 układów o pojemnościach od 256 do 6864 tablic LUT (tabela 1), produkowanym w oparciu o proces technologiczny 65 nm. Każdy z układów dostępny jest w dwóch wersjach: o bardzo niskim poborze mocy (ZE) oraz o wysokiej wydajności (HC, HE). Układy ZE i HC wymagają zasilania rdzenia napięciem 1,2V, podczas gdy układy HE posiadają wewnętrzny regulator napięcia i pracują z napięciem rdzenia 2,5V lub 3,3V. Statyczny pobór mocy przez układy MachXO2 serii ZE może sięgać tylko 19 uW (mikrowatów)! Oprócz całej gamy obudów BGA, wszystkie układy MachXO2 dostępne są również w przyjaznych dla montażu obudowach TQFP.

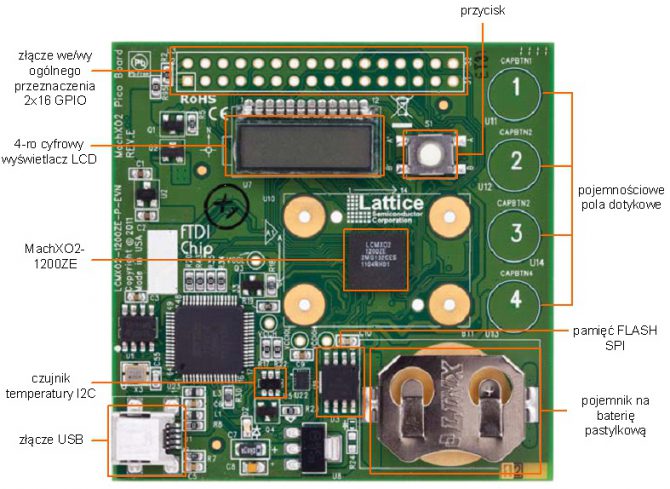

Zestaw ewaluacyjny MachXO2 Pico

Wraz z wprowadzeniem na rynek układów MachXO2, firma Lattice zaoferowała również dwa zestawy ewaluacyjne zbudowane na bazie tych układów. Jednym z takich zestawów jest prezentowany tutaj MachXO2 Pico Development Kit. Jak sugeruje nazwa jest to stosunkowo prosty zestaw, niemniej jednak w pełni umożliwiający praktyczne zapoznanie się z najważniejszymi cechami układów MachXO2. Zasadniczymi komponentami zestawu są:

- układ MachXO2 LCMXO2-1200ZE w obudowie csBGA o 132 wyprowadzeniach,

- 4 Mb pamięć Flash SPI,

- układ pomiaru poboru mocy z przetwornikiem Delta-Sigma,

- czujnik temperatury I2C,

- 4-ro cyfrowy wyświetlacz LCD,

- 4 pojemnościowe pola dotykowe,

- złącze zewnętrzne z 32 wyprowadzonymi liniami we/wy układu PLD,

- konwerter RS-232/USB.

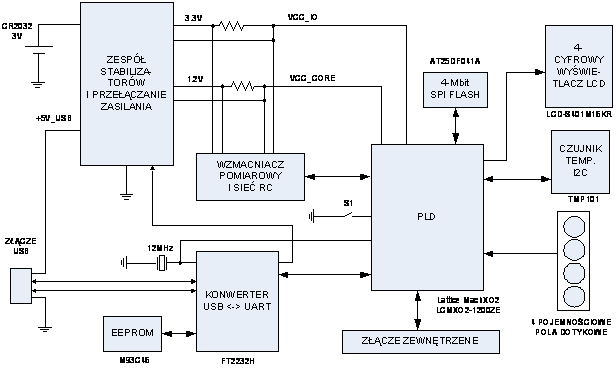

Uproszczony schemat blokowy zestawu pokazano na rysunku 7. Zestaw zasilany jest poprzez złącze USB lub, w przypadku braku zasilania głównego – za pomocą dodatkowej baterii 3V. W obwód zasilania rdzenia oraz buforów wejścia/wyjścia układu PLD wpięte są rezystory pomiarowe, za pomocą których dokonywany jest pomiar pobieranego prądu. Spadek napięcia na tych rezystorach, wzmacniany przez wzmacniacze pomiarowe, trafia do przetwornika delta-sigma zbudowanego z wykorzystaniem logiki programowalnej układu PLD oraz zewnętrznej sieci elementów RC. Zasadniczym elementem pozwalającym na wizualizację działania zestawu jest 4-cyfrowy analogowy wyświetlacz LCD. Zestaw nie zawiera diod LED ogólnego przeznaczenia, ale można je dołączyć za pośrednictwem zewnętrznego złącza o 32 wyprowadzeniach. Zamiast typowych przycisków w zestawie zastosowano pojemnościowe pola dotykowe, które na płytce drukowanej stanowią pola miedzi o kształcie okręgów, pokryte maską przeciwlutową. Rozmieszczenie najważniejszych elementów na płytce drukowanej zestawu przedstawia rysunek 8.

Programowanie (konfiguracja) układu PLD odbywa się poprzez złącze USB za pośrednictwem wbudowanego konwertera RS232/USB oraz oprogramowania (ispVM System) dostarczanego przez Lattice. Poprzez konwerter RS232/USB możliwa jest również komunikacja zestawu z komputerem PC za pośrednictwem zwykłego portu UART.

Przygotowanie zestawu do pracy w środowisku Windows

Współpraca zestawu MachXO2 Pico z komputerem PC i narzędziami projektowymi wymaga jedynie zainstalowania odpowiednich sterowników. Są one dostępne do pobrania na stronie producenta oraz znajdują się w materiałach dodatkowych do niniejszego kursu. Kolejność czynności instalacyjnych jest następująca: najpierw należy podłączyć zestaw do komputera PC za pomocą przewodu USB, a następnie w oknie instalacji nowego sprzętu należy wybrać opcję instalacji sterownika z określonej lokalizacji, wskazując folder w którym znajdują się pobrane pliki sterownika. W momencie nawiązania połączenia poprzez port USB na płytce zestawu zapala się niebieska dioda LED, sygnalizująca załączenie zasilania układu PLD i peryferii.

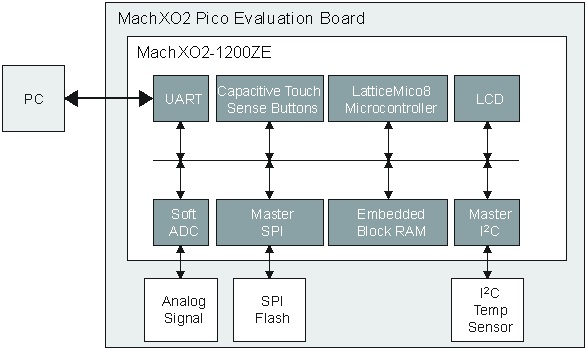

Zestaw MachXO2 Pico dostarczany jest z zaprogramowanym (skonfigurowanym) układem PLD, zawierającym demonstracyjną aplikację, ilustrującą sposób działania ważniejszych komponentów zestawu (odpowiedni plik konfiguracyjny w formacie JEDEC, a także pełne kody źródłowe aplikacji, można pobrać ze strony producenta). Aplikacja ta jest w istocie tzw. zintegrowanym systemem cyfrowym SoC (System On-Chip), którego ogólny schemat blokowy pokazano na rysunku 9.

Sercem systemu jest prosty, 8-bitowy „miękki” mikrokontroler LatticeMico8 (dostępny do pobrania bezpłatnie na stronie firmy Lattice). Mikrokontroler współpracuje z wbudowaną pamięcią RAM, blokami sterownika wyświetlacza LCD, portu UART, odczytu stanu pojemnościowych pól dotykowych, przetwornika analogowo-cyfrowego oraz poprzez blok EFB, z kontrolerami SPI oraz I2C. Jako elementy zewnętrzne, do systemu SoC dołączona jest pamięć Flash SPI, czujnik temperatury I2C, pojemnościowe pola dotykowe, wyświetlacz LCD a także doprowadzone są analogowe sygnały ze wzmacniaczy pomiarowych i drabinki RC.

Aplikacja demonstracyjna ilustruje zastosowanie mikrokontrolera LatticeMico8 wraz z dołączonymi peryferiami jako prostego systemu o niskim poborze mocy, pozwalającego na pomiar napięci/prądu, pomiar temperatury otoczenia, zapis i odczyt danych do/z pamięci nieulotnej, komunikację poprzez port UART, użycie pojemnościowych pól dotykowych i wyświetlacza LCD. Interakcja użytkownika z systemem możliwa jest przy pomocy pojemnościowych pól dotykowych lub typowego programu terminalowego (np. HyperTerminal) na komputerze PC.

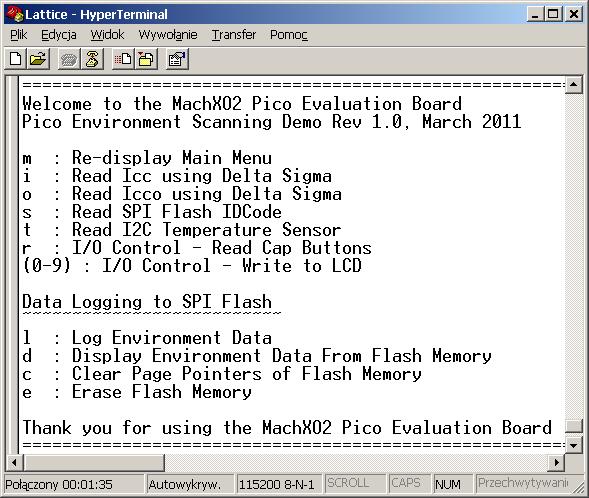

Niezbędny do skonfigurowania HyperTerminala numer portu szeregowego można odczytać, posługując się Menadżerem Urządzeń, w zakładce „Porty (COM i LPT)”, pod pozycją „USB Serial Port”. Parametry transmisji są następując: szybkość 115200 b/s, 8 bitów danych, brak bitu parzystości, brak sprzętowej kontroli przepływu danych, 1 bit stopu.

Po włączeniu zasilania (podłączeniu zestawu do złącza USB komputera PC) na wyświetlaczu LCD pojawiają się symbole tworzące napis „PICO”. Jeżeli na komputerze PC uruchomiony jest program HyperTerminal, wówczas naciśnięcie na klawiaturze PC klawisza „m” powoduje wyświetlenie w oknie HyperTerminala, menu pokazanego na rysunku 10. Wciskając teraz odpowiednie klawisze, wyszczególnione w menu, można wykonać przypisane do nich operacje, np.: odczyt poboru prądu, odczyt temperatury itp. Podobny efekt można uzyskać przykładając palec do jednego z czterech pól dotykowych zestawu, przy czym wartości zmierzonego prądu lub temperatury pojawiają się tylko na wyświetlaczu LCD i nie są wysyłane łączem szeregowym. Jeżeli w ciągu kilkunastu sekund system zanotuje brak jakiejkolwiek aktywności użytkownika wówczas automatycznie wprowadzany jest tryb o bardzo niskim poborze mocy (gaśnie wyświetlacz LCD). Wyjście z tego trybu i powrót do normalnej pracy możliwy jest po wciśnięciu przycisku znajdującego się na płytce zestawu. Naciśnięcie tego przycisku w czasie normalnej pracy wprowadza system w stan o bardzo niskim poborze mocy.

Środowisko projektowe Lattice Diamond

Synteza i implementacja projektów wykorzystujących układy programowalne wymaga odpowiedniego wsparcia ze strony narzędzi programowych. W przypadku układów FPGA (w tym również rodziny MachXO2), Lattice oferuje nowe, flagowe środowisko projektowe o nazwie Diamond. Jest ono dostępne zarówno dla systemów Windows jak i Linux. Oprogramowanie można pobrać ze strony producenta (http://www.latticesemi.com), wraz z dwoma rodzajami licencji na użytkowanie: bezpłatną i płatną. W tym pierwszym przypadku korzystanie z oprogramowania Diamond jest całkowicie darmowe, jednak wspierane są tylko niektóre rodziny układów Lattice, takie jak LatticeXP, LatticeECP &EC, LatticeECP2, LatticeXP2, a także MachXO i MachXO2.

Lattice Diamond jest kompletnym środowiskiem projektowym, za pomocą którego można przeprowadzić wszystkie fazy projektowania, począwszy od specyfikacji projektu aż do programowania (konfiguracji) docelowego układu programowalnego. W szczególności wspierane są takie procesy jak: specyfikacja projektu (możliwa jest mieszana specyfikacja z wykorzystaniem języków HDL Verilog oraz VHDL, listy połączeń EDIF i edytora schematów), synteza logiczna, implementacja, symulacja, programowanie a także analiza działania systemu uruchomionego w docelowym układzie programowalnym (on-chip debug hardware analysis).

Uwaga! Druga część artykułu jest dostępna pod adresem.

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii  Mieszacze aktywne – ćwiczenie z serii ADALM

Mieszacze aktywne – ćwiczenie z serii ADALM