[maXimator] Projekt cyfrowego termometru z sensorem analogowym i 7-segmentowym wyświetlaczem LED

W artykule przedstawiamy kompletną aplikację zestawu maXimator z FPGA z rodziny MAX10, w której spełnia on rolę cyfrowego termometru, wyświetlającego temperaturę otoczenia zmierzoną za pomocą sensora STLM20. Wynik pomiaru jest wyświetlany na 4-cyfrowym, multipleksowanym wyświetlaczu LED, który wraz z sensorem temperatury są zamontowane na shieldzie wchodzącym w skład zestawu. W projekcie zastosowano m.in. wbudowany w FPGA MAX10 przetwornik ADC, który służy do konwersji sygnału analogowego do postaci cyfrowej.

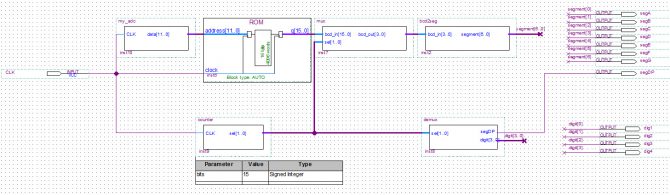

Działanie projektu zaimplementowanego w FPGA z rodziny Intel MAX10 najlepiej wyjaśni schemat blokowy pokazany na rysunku 1. Na wejście jednego z kanałów ADC wbudowanego w FPGA jest podawany sygnał napięciowy z wyjścia sensora STLM20. Przetwornik przetwarza napięcie na 12-bitową wartość cyfrową, następnie za pomocą techniki tablicowania (lookup table) odczytywana wartość jest konwertowana na wartość wyrażoną w stopniach Celsjusza i wyświetlana na multipleksowanym wyświetlaczu 7-segmentowym.

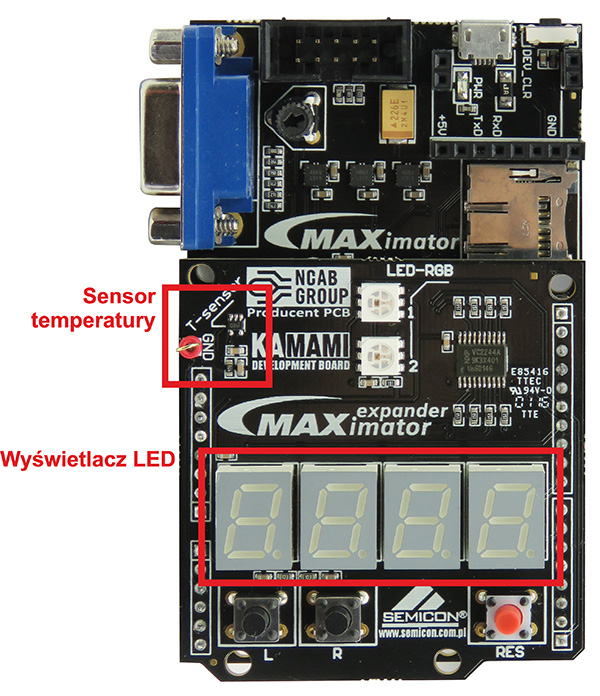

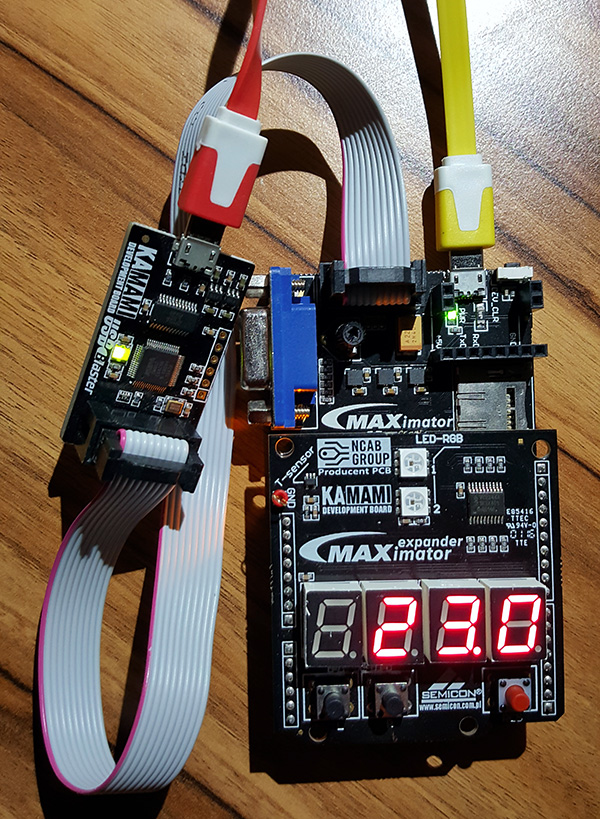

Wyświetlacz LED oraz analogowy sensor temperatury znajdują się na ekspanderze (shieldzie – fotografia 2), który wraz z programatorem JTAG jest jednym z elementów wyposażenia promocyjnej wersji maXimatora.

Fot. 2. Rozmieszczenie elementów używanych w projekcie na shieldzie zestawu maXimator

W tabeli 1 zestawiono wyprowadzenia FPGA z zestawu maXimator, które zostały wykorzystane w prezentowanym projekcie.

Tab. 1. Wyprowadzenia FPGA (MAX10), które wykorzystano w prezentowanym projekcie

| Nazwa | Kierunek | Funkcja |

| ADC1_15 | Wejście | Wejście sygnału analogowego, podłączone do czujnika temperatury. Wejście jest ustawiane w bloku my_adc |

| CLK0p | Wejście | Sygnał zegarowy 10 MHz |

| Wyprowadzenia: L16, J15, J16, H15, H16, G15, G16, F16 | Wyjście | Piny podłączone do wyświetlacza 7-segmentowego odpowiadające odpowiednio za segmenty: A, B, C, D, E, F, G, DP |

| Wyprowadzenia: E15,E16,D15,D16 | Wyjście | Piny podłączone do wyświetlacza 7-segmentowego odpowiadające za wybranie aktywnej cyfry (jednej z czterech) |

Blok my_adc przekazuje cyfrową wartość odpowiadającą zmierzonej temperaturze do bloku ROM, który przelicza ją na wartość w skali Celsjusza zapisaną w kodzie BCD. Moduł mux wybiera pojedynczą cyfrę z kodu BCD przekazuje ją do bloku bcd2seg, który zapisuje cyfrę w notacji 7-segmentowej. Moduł counter opóźnia multipleksowanie oraz służy do wybierania liczb do wyświetlenia. Moduł demux, na podstawie wartości otrzymanej z bloku counter wybiera odpowiedni wyświetlacz, na którym wyświetlona zostaje cyfra.

Funkcje poszczególnych bloków i ich sygnały są następujące:

my_adc

Moduł przetwarza wartość analogową z czujnika temperatury na wartość cyfrową. Wykorzystano w nim komponent ADC wygenerowany przy pomocy narzędzia Qsys programu Quartus Prime Lite. W module można ustawić, który kanał ma być wejściem analogowym przetwornika. W projekcie jest to kanał nr 15 – ADC1_15, co wynika ze sposobu podłączenia sensora STLM20 do wyprowadzeń FPGA. Wejścia i wyjścia tego modułu opisano w tabeli 2.

Tab. 2. Wejścia i wyjścia modułu my_adc

| Nazwa | Kierunek | Ilość bitów | Funkcja |

| CLK | Wejście | 1 | Sygnał zegarowy |

| data | Wyjście | 12 | Przetworzona wartość cyfrowa |

ROM

Jest to moduł pamięci ROM, zainicjalizowanej ręcznie utworzonym plikiem LUT.mif. Moduł odpowiada za przetworzenie wartości otrzymanej z czujnika temperatury na wartość w skali Celsjusza w kodzie BCD. Przeliczenie jest zrealizowane za pomocą techniki tablicowania (Lookup Table). Moduł został wygenerowany przy pomocy IP Core’a ROM: 1-PORT dostępnego w programie Quartus Prime Lite. Ze względu na znaczne wahania wartości odczytanej z czujnika temperatury w pliku LUT.mif nie została zamieszczona część dziesiętna wartości przedstawiającej temperaturę (dla każdej wartości część dziesiętna jest równa zero).

Wejścia i wyjścia modułu ROM opisano w tabeli 3.

Tab. 3. Wejścia i wyjścia modułu ROM

| Nazwa | Kierunek | Ilość bitów | Funkcja |

| address | Wejście | 12 | Cyfrowa wartość temperatury |

| Q | Wyjście | 16 | Wartość temperatury w skali Celsjusza, zapisana w kodzie BCD |

mux

Jest to multiplekser, który wybiera z kodu BCD pojedynczą cyfrę do wyświetlenia. O wyborze cyfry decyduje wejściowy sygnał sel. Wejścia i wyjścia tego modułu opisano w tabeli 4.

Tab. 4. Wejścia i wyjścia modułu ROM

| Nazwa | Kierunek | Ilość bitów | Funkcja |

| bcd_in | Wejście | 16 | Temperatura zapisana w kodzie BCD |

| sel | Wejście | 2 | Decyduje o wyborze fragmentu z wejściowego kodu BCD |

| bcd_out | Wyjście | 4 | Pojedyncza cyfra zapisana w kodzie BCD |

bcd2seg

Moduł otrzymaną cyfrę w kodzie BCD zapisuje w notacji 7-segmentowej. Wejścia i wyjścia tego modułu opisano w tabeli 5.

Tab. 5. Wejścia i wyjścia modułu bcd2seg

| Nazwa | Kierunek | Ilość bitów | Funkcja |

| bcd_in | Wejście | 4 | Cyfra w kodzie BCD |

| segment | Wyjście | 7 | Cyfra w zapisie 7-segmentowym |

counter

Licznik n-bitowy. Ilość bitów ustawia się w parametrze bits. Funkcją licznika jest opóźnienie multipleksowania oraz wybór cyfry do wyświetlenia. Wejścia i wyjścia tego modułu opisano w tabeli 6.

Tab. 6. Wejścia i wyjścia modułu counter

| Nazwa | Kierunek | Ilość bitów | Funkcja |

| CLK | Wejście | 1 | Sygnał zegarowy |

| sel | Wyjście | 2 | Sygnał sterujący wyborem cyfry |

demux

Demultiplekser wybiera cyfrę do wyświetlenia, dodatkowo włącza kropkę oddzielającą część dziesiętną wartość temperatury. Wejścia i wyjścia tego modułu opisano w tabeli 7.

Tab. 7. Wejścia i wyjścia modułu demux

| Nazwa | Kierunek | Ilość bitów | Funkcja |

| sel | Wejście | 2 | Sygnał sterujący wyborem cyfry |

| digit | Wyjście | 4 | Sygnał wybierający cyfrę do wyświetlenia |

| segDP | Wyjście | 1 | Segment wyświetlacza odpowiedzialny za kropkę |

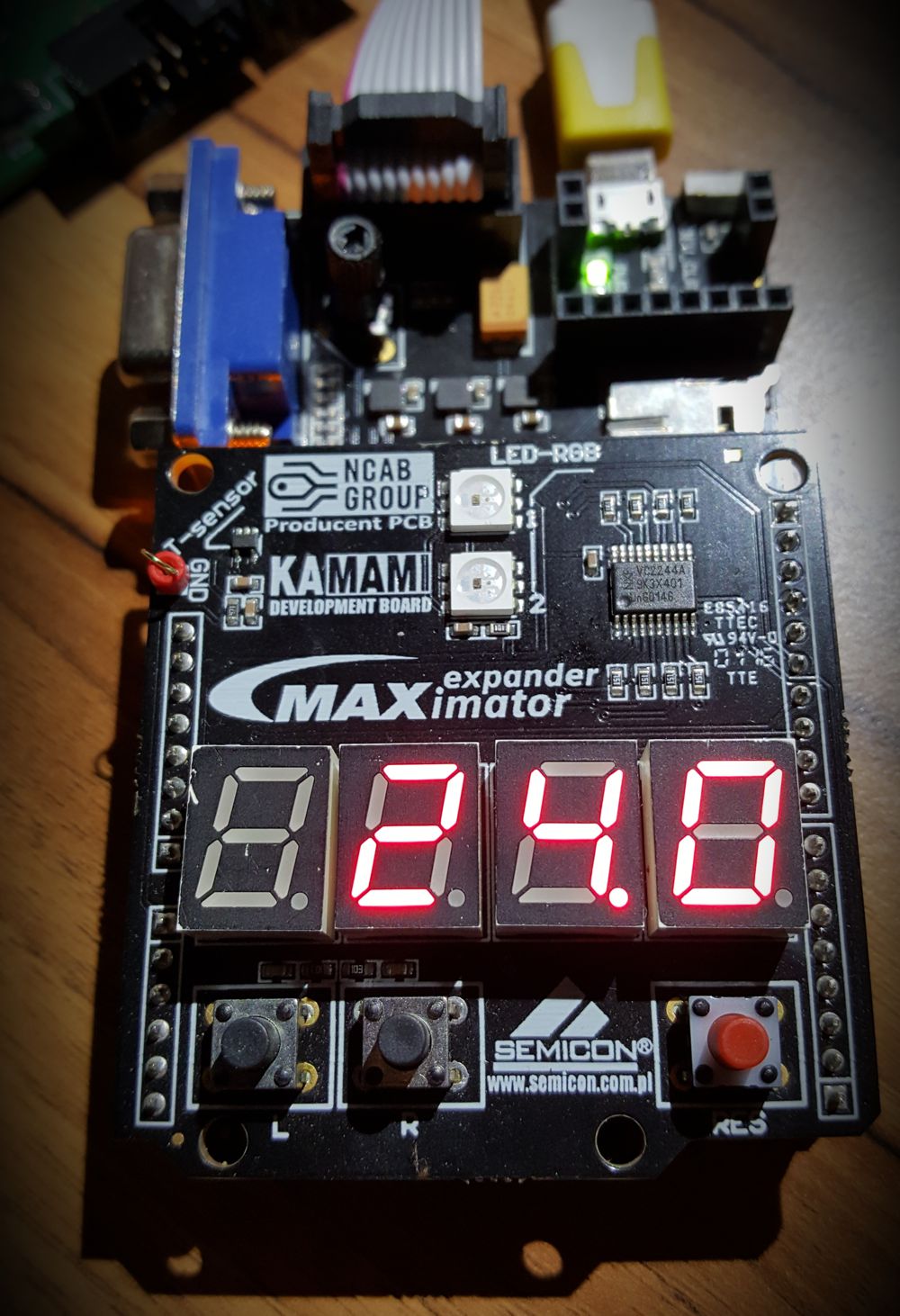

Prezentowany projekt jest dość prosty do wykonania, różni się od typowych implementacji realizowanych w FPGA przede wszystkim faktem wykorzystania wbudowanego w układ przetwornika ADC (wyposażenie rzadko spotykane w FPGA). Na fotografii 3 przedstawiono przykładowy wynik pomiaru temperatury wykonanego za pomocą maXimatora i zastosowanego w shieldzie sensora temperatury STLM20.

Przykład został zaimplementowany w zestawie maXimator za pomocą bezpłatnego narzędzia Quartus Prime Lite (do pobrania na stronie www.altera.com), komplet plików jest dostępny do pobrania na stronie maximator-fpga.org.

Projekt powstał w Katedrze Elektroniki Wydziału Informatyki, Elektroniki i Telekomunikacji AGH, pod opieką merytoryczną dr inż. Pawła Rajdy i dr inż. Jerzego Kasperka.

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii