Procesor IP MIPS I6500-F dla systemów krytycznych pod względem bezpieczeństwa

Nowy procesor, który zapoczątkował serię układów FortifAI, łączy wysoką wydajność i bezpieczeństwo funkcjonalne. Jest przeznaczony dla systemów wykorzystujących sztuczną inteligencję.

Firma Imagination Technologies przedstawiło nowe rozwiązani w postaci skalowalnego, 64-bitowego procesora w architekturze MIPS. Projekt przeszedł właśnie trudne testy, spełniając wymagania dotyczące bezpieczeństwa funkcjonalnego zgodnie ze standardami ISO 26262 oraz IEC 61508. Układ MIPS I6500-F jest rozwiązaniem w postaci procesora programowego (IP), który pozwala na obsługę wymagających obliczeniowo zadań w systemach krytycznych dla bezpieczeństwa, takich jak autonomiczne pojazdy, przemysłowe urządzenia IoT oraz roboty.

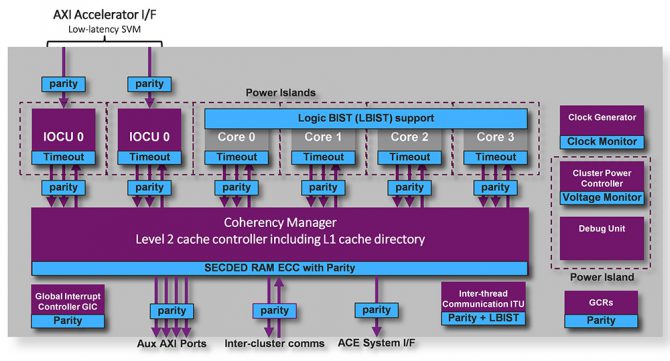

Układ I6500-F zapewnia możliwości większe, niż inne rdzenie IP FuSA – wyższą wydajność, możliwość realizacji wielordzeniowych systemów i możliwość skalowania do 64 heterogenicznych klastrów zawierających wielowątkowe, wielordzeniowe procesory MIPS i inne układy akceleracji.

Bezpieczeństwo funkcjonalne (FuSa) jest podstawowym wymaganiem, które muszą spełniać systemy krytyczne dla bezpieczeństwa – w tym procesor IP zarządzający układem SoC. W zastosowaniach takich, jak autonomiczne pojazdy i przemysłowe systemy kontroli w inteligentnych fabrykach, wymagane są coraz większe możliwości obliczeniowe, które przekraczają możliwości dostępnych obecnie rdzeni IP gwarantujących bezpieczeństwo funkcjonalne. Teraz użytkownicy będą mogli wykorzystać dużą wydajność obliczeniową I6500-F, aby w efektywny sposób zintegrować bardziej inteligentne rozwiązania w urządzeniach krytycznych dla bezpieczeństwa. Należą do nich techniki AI, takie jak sieci neuronowe typu CNN oraz DNN.

Rozwój zaawansowanych zabezpieczeń

Imagination implementuje technologie zapewniające podstawę bezpieczeństwa w oferowanych układach typu MIPS. Wykorzystuje dotychczasowe osiągnięcia w rozwoju rdzeni IP – w tym układów z serii MIPS 5600. Układy te są wykorzystywane w projektach o krytycznym znaczeniu dla bezpieczeństwa opartych na nadmiarowości, pracujących w środowisku przemysłowym wymagającym wysokiej niezawodności.

Nowa oferta jest też związana z kontynuacją współpracy w rozwojów systemów bezpieczeństwa z firmą Mobileye. Opracowany przez Mobileye układ SoC QyeQ4 dla systemów wspomagania kierowcy (ADAS) wykorzystuje procesory MIPS interAptiv oraz M5150 z oprogramowaniem pozwalającym na samodzielne testowanie rdzenia. Zostały on zaprojektowany, aby spełnić wymagania klasy bezpieczeństwa ASIL B. Z kolei układ SoC następnej generacji EyeQ5 dla autonomicznych pojazdów, oparty na procesorze I6500-F, zostanie wyprodukowany w procesie technologicznym FinFET 7 nm. EyeQ5 będzie stanowić otwartą platformę oprogramowania, na bazie której użytkownicy będą mogli realizować własne algorytmy. Jest to możliwe dzięki rozwiązaniom zastosowanym w architekturze MIPS – na przykład wirtualizacji sprzętu. Układy SoC Mobileye dla systemów ADAS są już dostępne w sprzedaży.

Rozwiązanie dla wymagających systemów samochodowych

Imagination opracowała metodologię oraz procesy projektowania i zapewnienia bezpieczeństwa, których skuteczność została udowodniona i udokumentowana zgodnie z wymaganiami normy ISO 26262. Opisuje ona zasady planowania bezpieczeństwa, procedury weryfikacji i metody potwierdzenia bezpieczeństwa.

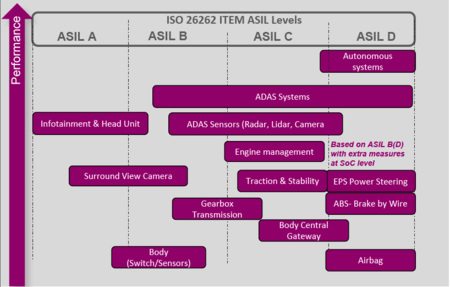

Układ I6500-F został zaprojektowany, aby spełnić wymagania ASIL poziomu B(D). Dzięki temu układ ten może zostać wykorzystany w systemach samochodowych do poziomu ASIL D. Układ IP został zaprojektowany jako SEooC (Safety Element out of Context), zapewniając bezpieczeństwo podczas całego okresu życia. Powstał we współpracy z głównymi partnerami oraz niezależną firmą weryfikującą bezpieczeństwo – ResilTech. W takim rozwiązaniu projekt gwarantujący bezpieczeństwo I6500-F podczas całego cyklu życia jest zapewniony przez dostawcę komponentów, zgodnie z 1. wersją standardu ISO 26262 z roku 2011. Układ wykorzystuje też wybrane fragmenty obecnej 2. edycji standardu ISO 26262, który już dostępny w opublikowanej wersji roboczej (DIS).

Układ I6500-F reprezentuje nową klasę procesorów MIPS zaprojektowanych, aby wprowadzić rozwiązanie FortifAI do inteligentnych systemów następnej generacji. Procesor zapewnia bardzo wysoką efektywność systemu i skalowalne możliwości obliczeniowe, a także wysoki poziom bezpieczeństwa funkcjonalnego. Układ wykorzystuje rozwiązanie SEooC zapewniające bezpieczeństwo funkcjonalne, ułatwienia dla procesu certyfikacji i wielowątkowość pozwalającą na realizację heterogenicznych, wielordzeniowych architektur opartych na I6500-F. Dzięki tym cechom pozwoli szybciej wprowadzić na rynek autonomiczne samochody wykorzystujące AI, co będzie możliwe za sprawą układów SoC zgodnych z normą ASIL-D. Procesor stanowi odpowiedź na zapotrzebowanie rynku motoryzacji i pozwoli na rozwój technologii samojezdnych pojazdów poziomu 4/5.

Układ MIPS I6500-F jest oparty na popularnym wielordzeniowym, 64-bitowym procesorze MIPS I6500, który umożliwia obsługę wiele klastrów i skalowanie na potrzeby zarówno systemów wbudowanych, jak i systemów chmurowych. Oba rdzenie IP pozwalają na spójną implementację konfiguracji optymalizujących rdzenie procesora w ramach klastra („Heterogenous Inside”) i wiele konfiguracji klastrów CPU oraz akceleratorów GPU („Heterogenous Outisde”). Dzięki dodatkowym funkcjom, takim jak wielowątkowość (SMT) oraz wirtualizacja sprzętu (VZ), układy IP oferują wiele zalet – na przykład możliwość natychmiastowego przełączenia kontekstu w aplikacjach wymagających odpowiedzi w czasie rzeczywistym. Układy są również zgodne z rozwiązaniem OmniShield – dzięki separacji architektury mogą zapewnić wiarygodną podstawę bezpieczeństwa.

Projekt MIPS I6500-F powstał dzięki systemowi zarządzania jakością, który pozwolił naprawić błędy systematyczne. Obsługa wbudowanych testów automatycznych (LBIST) w czasie rzeczywistym i szerokie wykorzystanie nadmiarowości w krytycznych rejestrach oraz we wbudowanych pamięciach rdzeni pozwala na wykrycie skoków napięcia oraz trwałych uszkodzeń układu. Nadmiarowość jest obecna również w podukładzie Coherence Manager (CM3) oraz IO Coherence Unit (IOCU), które wspólnie zapewniają kompletną ochronę wielordzeniowego klastra I6500-F.

Dokumentacja

Układ I6500-F będzie dostępny w kompletnym pakiecie bezpieczeństwa obejmującym między innymi raport bezpieczeństwa FMEDA sporządzony przez niezależną firmę ResilTech, który pomoże klientom spełnić wymagania normy bezpieczeństwa IDO 26262. Imagination dostarczy również pakiet pomocy „Safety Consultancy Support”, który ułatwi klientom integrację i przygotowanie analizy bezpieczeństwa na poziomie SoC, aby uzyskać zgodność z normą ISO 26262.

Dostępność

Licencje na układ IP I6500-F są już dostępne. Szczegóły można uzyskać pod adresem info@imgtec.com.

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485