Mikrokontrolery Renesas o niskim poborze mocy idealne do aplikacji Energy Harvesting

Artykuł prezentuje zalety pierwszego mikrokontrolera firmy Renesas, który został opracowany w technologii SOTB. Układ R7F0E017 szczególnie dobrze sprawdzi się w aplikacjach Energy Harvesting.

W następstwie katastrofy nuklearnej w Fukushimie, japoński rząd ustanowił inicjatywę LEAP (ang. Low Power Electronics Association and Project). Jej celem jest opracowanie nowych technologii o bardzo niskim poborze mocy, aby na szeroką skalę zmniejszyć zużycie energii w aplikacjach rynku konsumenckiego i przemysłowego.

Jedną z pierwszych technologii, która może zostać wykorzystana w tym programie, jest nowy proces technologiczny dla półprzewodników, który pozwoli na opracowanie całej gamy innowacyjnych układów półprzewodnikowych o bardzo niskim poborze mocy.

Proces ten znany jest pod angielską nazwą Silicon on Thin Buried Oxide (SOTB). Został on opracowany na podstawie technologii FD-SOI, która jest powszechnie stosowana do produkcji układów SoC i standardowych układów scalonych (ASSP). Urządzenia wykorzystujące technologię procesu FD-SOI oferują wysoki poziom integracji i wysokie częstotliwości taktowania. Mimo, że mogą oferować imponujące wartości Icc/MHz, zwykle nie są uważane za energooszczędne i nie mają integracji z wbudowaną pamięcią.

Technologia SOTB została specjalnie opracowana, aby wspierać projektowanie mikrokontrolerów następnej generacji o bardzo niskim poborze mocy, mających na celu dostarczanie wydajnych rozwiązań służących do aplikacji Energy Harvesting.

Kontrolery wbudowane tworzone za pomocą nowego procesu SOTB będą mogły łączyć w sobie wysoką wydajność procesora, wysoki poziom integracji pamięci i niezwykle niski poziom poboru prądu, zarówno dla urządzenia w stanie włączenia, jak i w stanie gotowości. Dzięki temu są idealne do połączonych aplikacji, które będą pobierały energię ze środowiska.

Większość dzisiejszych mikrokontrolerów opracowano przy użyciu jednej z wielu odmian procesów CMOS. Procesy te mają długą historię w branży półprzewodników i są niezwykle dobrze rozumiane, zarówno pod względem korzyści, jak i słabości wynikających ze specyfiki procesów. Kiedy chcemy opracować nowy mikrokontroler dla konkretnej aplikacji, musimy rozsądnie dobrać proces, w zależności od wymaganych właściwości elektrycznych urządzenia.

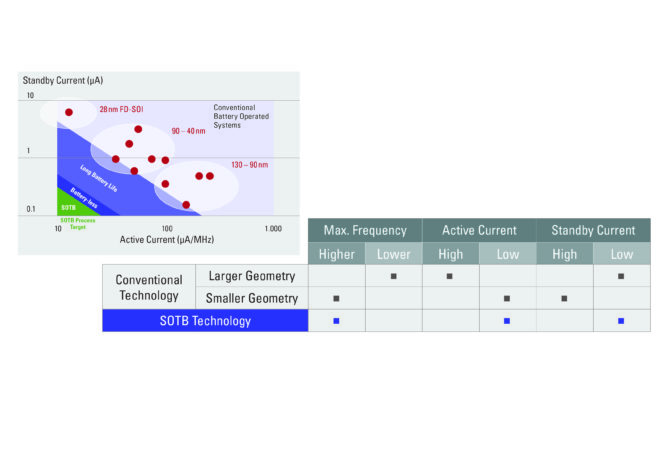

Rysunek 1 pokazuje porównanie pomiędzy SOTB i wieloma innymi procesami wykorzystywanymi do produkcji aktualnie dostępnych na rynku mikrokontrolerów, przy różnych wielkościach procesu.

Rysunek 1. Mapa technologii procesowych minimalizujących prądy czynne i upływowe

Rysunek 1. Mapa technologii procesowych minimalizujących prądy czynne i upływowe

Przy projektowaniu układu, do wyboru są zaawansowane procesy technologiczne, zwykle o wielkości charakterystycznej 40 nm lub jeszcze mniejszej. Dzięki temu mamy możliwość oferowania produktów o wysokim poziomie integracji urządzeń peryferyjnych, w tym dużych pamięci flash (on-chip) o pojemności powyżej 2 MB. Układy umożliwiają też pracę przy wysokich częstotliwościach zegara, nierzadko przekraczającej 200 MHz. Jednakże, podczas gdy aktywny prąd przełączania takiego procesu jest zwykle bardzo niski (około 50…100 µA/MHz), prąd upływu z każdej bramki przy tak małej szerokości procesu jest bardzo wysoki. Powoduje to wyjątkowo wysokie prądy czuwania, zwykle 10…100 µA lub nawet więcej.

W wielu aplikacjach, zwłaszcza tych, które wykorzystują baterię lub wymagają technik pozyskiwania energii z otoczenia, prawdopodobnie najważniejszym parametrem jest prąd upływu w trybie gotowości. Jeśli jest to kluczowy wymóg dla projektu, zazwyczaj należy wybrać proces o większej szerokości linii. Ogranicza to moduły zarówno pod względem wydajności, jak i poziomu integracji pamięci i innych urządzeń peryferyjnych. Typowe częstotliwości zegara w tym przypadku są mniejsze niż 80 MHz, a pamięci ograniczone są zwykle do poniżej 512 KB.

Zazwyczaj układy wytworzone w tych procesach mogą mieć tryby aktywne z poborem prądu w zakresie 250…500 µA/MHz, podczas gdy prądy upływu może mieścić się w zakresie kilkuset nA.

Nowy proces SOTB może oferować niski pobór prądu w trybie aktywnym (poniżej 20 µA/MHz) i prądy upływu do 150 nA, jednocześnie umożliwiając rozwój urządzeń o wysokich częstotliwościach zegara, a także dużych, wbudowanych pamięciach Flash i SRAM.

To połączenie możliwości integracji i niskiego poboru mocy sprawia, że urządzenia wytworzone w tym procesie będą idealne w aplikacjach związanych z pozyskiwaniem energii z otoczenia. Prawdopodobnie zmniejszy to także całkowite zapotrzebowanie na energię nawet 10-krotnie w porównaniu z urządzeniem wykorzystującym tradycyjny proces CMOS.

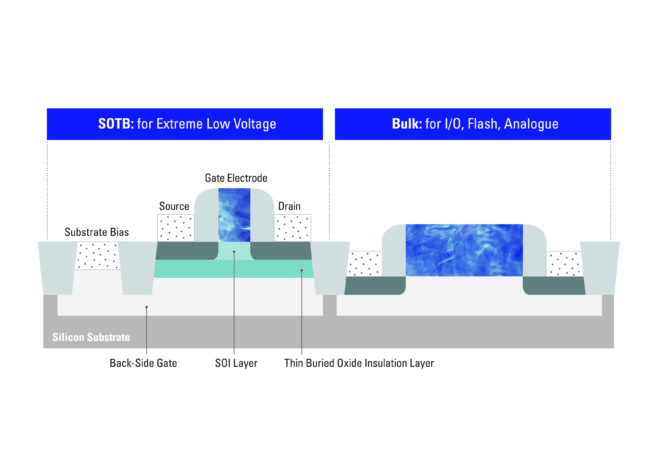

Jednym z ogromnych przełomów w rozwoju tej technologii jest możliwość realizacji hybrydowej struktury krzemowej. Łączy to mocne strony nowego procesu SOTB i istniejącej, standardowej technologii krzemowej w tej samej konstrukcji. Pozwala więc wykorzystać zalety obu technologii w tym samym urządzeniu i wytworzyć mikrokontrolery z wbudowaną pamięcią Flash.

Zastosowanie struktury hybrydowej oznacza, że możemy użyć nowej technologii SOTB o niskim poborze mocy w obszarze jądra. Kluczowe elementy logiczne, takie jak procesor i urządzenia peryferyjne, mogą zostać zaimplementowane w sposób pozwalający na jak najniższy pobór mocy. Przy tym nadal możemy korzystać ze standardowej technologii krzemowej dla takich funkcji jak wejścia/wyjścia i komponenty analogowe, gdzie może być wymagane wysokie napięcie. Oznacza to, że projektanci systemów wbudowanych mogą z łatwością pracować z nowymi mikrokontrolerami, ponieważ będą one miały podobne charakterystyki elektryczne do znanych już układów.

Rysunek 2 ilustruje tę hybrydową architekturę.

Rysunek 2. Struktura hybrydowa SOTB

Rysunek 2. Struktura hybrydowa SOTB

Ten schemat pokazuje również niektóre zalety technologii SOTB. W tradycyjnej konstrukcji krzemowej CMOS musimy wprowadzić atomy domieszek do krzemu podczas procesu produkcyjnego, co umożliwia tranzystorowi przewodzenie w razie potrzeby. Liczba atomów wstrzykiwanych do każdego elementu jest niezwykle trudna do kontrolowania, więc charakterystyka progowa bramki może się znacznie różnić w urządzeniu. Jest to szczególnie problematyczne przy mniejszych procesach technologicznych, gdy liczba zaangażowanych atomów jest niezwykle mała, czasami w ilości 100 pojedynczych atomów. Oznacza to, że może występować znaczna zmienność liczby atomów domieszki w bramce, co powoduje dużą zmienność charakterystyki przełączania w układzie.

Dzięki technologii SOTB można uniknąć tego problemu, wykorzystując konstrukcję kanału bez domieszek. Charakterystyka bramki jest zależna od bardzo cienkiej warstwy tlenkowej wewnątrz elementu. W nowoczesnych procesach technologicznych jest to wyjątkowo dobrze kontrolowane, a także powtarzalne w całym układzie.

Oznacza to, że zmienność napięcia progowego między każdą bramką jest znacznie mniejsza niż w przypadku tradycyjnej konstrukcji krzemowej. Jak zobaczymy za chwilę, to zmniejszenie różnic napięcia progowego w urządzeniu SOTB pozwala nam znacznie zmniejszyć napięcie robocze, a tym samym energię zużywaną do przełączania elementów. Zmniejszenie zmian napięcia progowego między bramkami urządzenia ma również kilka innych znaczących korzyści, takich jak np. zmniejszenie szumu generowanego pomiędzy dopasowanymi parami tranzystorów w urządzeniu.

Redukcja szumów ma również wpływ na parametry analogowe urządzenia. Ze względu na niższy poziom szumu wewnętrznego, parametry analogowe zostały znacznie polepszone, dzięki czemu zintegrowane komponenty analogowe zapewniają wyższą wydajność niż w przypadku standardowej konstrukcji CMOS.

Cienka warstwa krzemu na izolacji (SOI) ma również inne zalety, ponieważ zapewnia dodatkową ochronę przed błędami spowodowanymi promieniowaniem kosmicznym. W związku z tym współczynnik błędów oprogramowania na tych urządzeniach jest znacznie niższy w porównaniu do podobnych urządzeń w tym samym procesie.

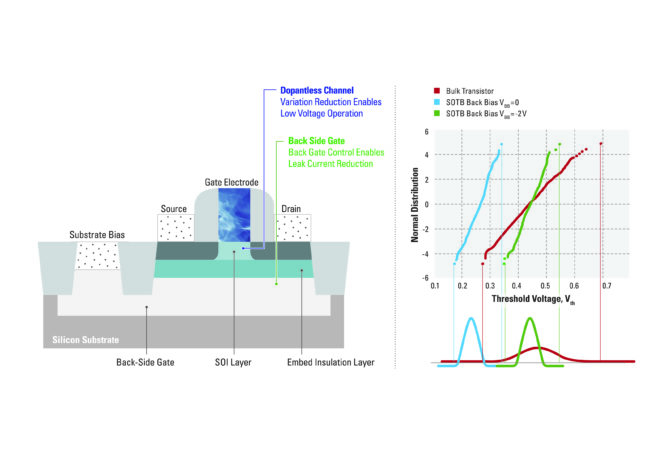

Rysunek 3 ilustruje kolejną zaletę technologii SOTB: możliwość zastosowania ujemnego napięcia polaryzacji do każdego elementu. Pozwala to manipulować progami przełączania każdej bramki w układzie, indywidualnie lub też całościowo.

Rysunek 3. Porównanie progów w klasycznych procesach i SOTB

Rysunek 3. Porównanie progów w klasycznych procesach i SOTB

Rysunek 3 pokazuje porównanie pomiędzy układem SOTB, a urządzeniem wykonanym w standardowym procesie CMOS. Ilustruje również konstrukcję elementu SOTB z tylną bramką, wykorzystywaną do kontroli upływu, warstwą SOI i kanałem bez domieszki. Umożliwia to zwiększenie powtarzalności elementów, a także pozwala uzyskać wyjątkowo niski pobór prądu w stanie aktywnym.

Wykres po lewej stronie rysunku 3 pokazuje napięcia progowe dla standardowej bramki CMOS i bramki SOTB. Czerwona linia na tym wykresie pokazuje zakres charakterystyki przełączania dla typowego urządzenia zaimplementowanego w klasycznym procesie krzemowym. W tym przypadku pokazujemy zmianę progu przełączania między 1 milionem poszczególnych tranzystorów na chipie testowym. Schemat pokazuje, że najlepsze bramki przełączą się przy napięciu około 0,3 V, a ze względu na nieodłączny rozrzut procesu, najgorsze bramki przestawią się w okolicy 0,7 V. W celu zagwarantowania działania każdej bramki w urządzeniu, musimy zatem działać przy napięciach znacznie powyżej 1,0 V. Ma to oczywiście bezpośredni wpływ na moc pobieraną przez moduł.

Niebieska linia na rysunku 4 pokazuje charakterystykę bramki SOTB z ogromnym zmniejszeniem rozrzutu i wąskim zakresem parametrów przełączania, które można osiągnąć za pomocą tego procesu. Układy oparte na procesie SOTB mogą bezpiecznie pracować przy znacznie niższych napięciach i gwarantują, że każda bramka będzie działała poprawnie, co spowoduje znaczne zmniejszenie zużycia energii w stanie aktywnym.

Zielona linia na rysunku 4 pokazuje wynik zastosowanej polaryzacji ujemnej. Możemy kontrolować upływ prądu na poszczególnych elementach. Innymi słowy, można wysterować część lub cały układ na wyjątkowo niski pobór prądu upływu, co znacznie zmniejsza pobór mocy w trybie czuwania.

W wyniku tego nowego procesu możemy opracować nową generację mikrokontrolerów. Będą one łączyć najlepsze cechy zarówno technologii o mniejszej geometrii: wysoki poziom integracji i niski prąd w trybie aktywnym, a także technologii o większej geometrii – niski prąd upływu.

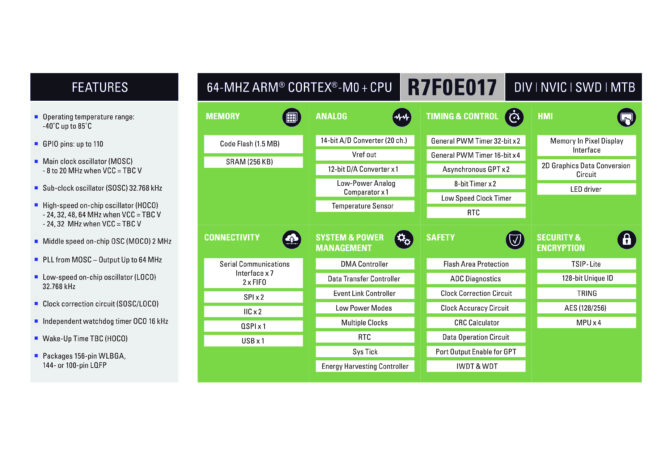

Renesas zakończył opracowywanie pierwszego mikrokontrolera w procesie SOTB. Zastosowanie procesu SOTB pozwala stworzyć urządzenie o unikalnej kombinacji wydajności, integracji i zużycia energii. Pierwsze urządzenie łączy rdzeń ARM Cortex-M0+, z częstotliwością do 64 MHz, z wysokim poziomem integracji peryferii i pamięcią flash o pojemności do 1,5 MB, a także pamięcią SRAM o pojemności do 256 KB w jednym chipie.

Zastosowanie technologii SOTB w nowym ukladzie zaowocowało wyjątkowymi cechami dla niskiego poboru mocy. Pierwsze urządzenie ma następujące właściwości, a przyszłe urządzenia wykorzystujące ten sam proces, mogą oferować jeszcze niższe zużycie mocy.

- Prąd w stanie aktywnym: 20 μA / MHz

- Prąd w stanie gotowości: 200 nA

- Działanie ADC: 3 μA przy 32 kHz

- Pamięć SRAM 256 KB z prądem gotowości: 1 nA/KB

Pierwszym układem stosującym nowy proces SOTB jest Renesas R7F0E017. Schemat blokowy na rysunku 4 zawiera przegląd jego funkcji.

Rysunek 4: Pierwszy mikrokontroler wykorzystujący proces SOTB

Rysunek 4: Pierwszy mikrokontroler wykorzystujący proces SOTB

Nowy Renesas R7F0E017, z unikalną kombinacją dużej pamięci Flash i SRAM na chipie oraz bardzo niskim zużyciem energii, będzie idealny dla szerokiej gamy aplikacji. Należą do nich również aplikacje, które nie mogą korzystać z baterii lub zdalnego źródła zasilania, a energia musi być dostarczana z otoczenia.

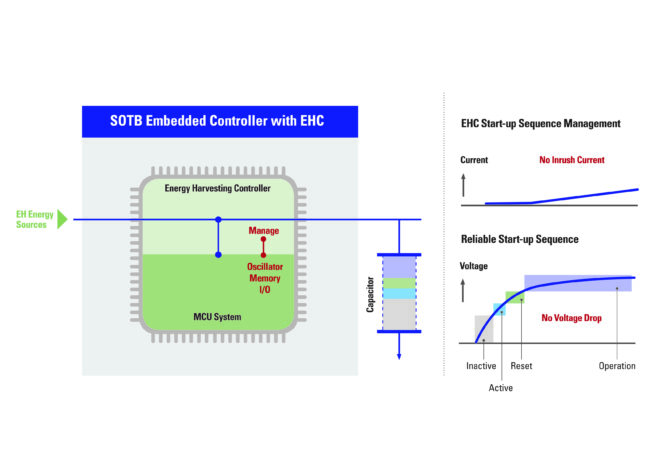

Po raz pierwszy wbudowany kontroler SOTB pozwoli potężnym, połączonym z siecią aplikacjom na pozyskiwanie energii ze środowiska. Z tego powodu zawiera zintegrowany kontroler pozyskiwania energii.

To unikalne urządzenie peryferyjne zostało zaprojektowane, aby umożliwić mikrokontrolerowi start za pomocą źródła pozyskiwania energii, a także zarządzanie zewnętrznymi akumulatorami lub superkondensatorami w celu zapewnienia rezerwy zasilania.

Istnieje wiele problemów, które należy rozwiązać, projektując aplikację Energy Harvesting. Na przykład, jednym z największych problemów podczas używania normalnego mikrokontrolera jest zarządzanie prądem rozruchowym, ponieważ źródło energii zazwyczaj może dostarczać tylko niewielką ilość prądu w danym momencie. Jednak normalny mikrokontroler zwykle podczas fazy rozruchu wykorzystuje znacznie więcej prądu, niż jest dostępne ze źródła energii.

Kontroler poboru energii na R7F0E017 zarządza prądem rozruchowym wraz z całą sekwencją rozruchu, dzięki czemu mikrokontroler uruchamia się niezawodnie i bezpiecznie.

Rysunek 5 pokazuje działanie kontrolera pozyskiwania energii, zaimplementowanego na R7F0E017.

Rysunek 5. Działanie kontrolera Energy Harvesting

Rysunek 5. Działanie kontrolera Energy Harvesting

R7F0E017 jest w stanie bezpiecznie pracować za pomocą źródła pobierającego energię z otoczenia dzięki działaniu wbudowanego układu peryferyjnego. Mikrokontroler może pracować z szeroką gamą potencjalnych źródeł energii, w tym energią słoneczną, wibracji, różnicy ciśnień i temperatur oraz wielu innych. Zintegrowany kontroler poboru energii, wspierany przez kilka niedrogich komponentów zewnętrznych jest w stanie w pełni zarządzać cykliczną sekwencją rozruchu mikrokontrolera, wykorzystując jedynie prąd z niskoenergetycznego źródła pobierającego energię. Sterownik zbierający energię posiada wewnętrzne zabezpieczenie „prądem rozruchowym” i może pracować na bardzo niskim poziomie napięcia, aby uniknąć wadliwego działania podczas fazy rozruchu.

Zastosowanie technologii SOTB (Silicon on Thin Buried Oxide) umożliwia firmie Renesas na dostarczanie urządzeń o unikalnych właściwościach, które czynią je idealnymi do zastosowań w aplikacjach pobierających energię ze środowiska. Połączenie niskiego zużycia energii – zarówno w trybie aktywnym, jak i gotowości – wraz z dużą pamięcią układów i wysokowydajnym procesorem pozwala użytkownikom tworzyć zaawansowane rozwiązania dla aplikacji następnej generacji. Zapewni to rozwiązania dla aplikacji, których jeszcze nie możemy sobie wyobrazić.

Próbki R7F0E017, wraz z kompletnym zestawem narzędzi programistycznych, będą dostępne dla klientów w wersji beta na początku 2019 r., natomiast próbki ogólne będą dostępne w drugiej połowie 2019 r.

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485