[RAQ] Przetwornik SAR o zakresie dynamiki 125 dB

Pytanie:

Czy 16-bitowy przetwornik SAR może osiągnąć dynamikę 125 dB przy próbkowaniu 600 kSPS?

Odpowiedź:

Tak, 89 dB + 18 dB + 20 dB ≥ 125 dB.

Wprowadzenie

W rozwiązaniach wymagających dużego zakresu dynamiki często stosowany jest przetwornik sigma-delta. Zastosowania te dotyczą głównie analizy chemicznej, opieki zdrowotnej i kontroli wagi. Wiele z tych przetworników nie nadaje się do szybkiej konwersji. Rysunek 1 opisuje układ łączący wysoki zakres dynamiki z wysokim współczynnikiem konwersji.

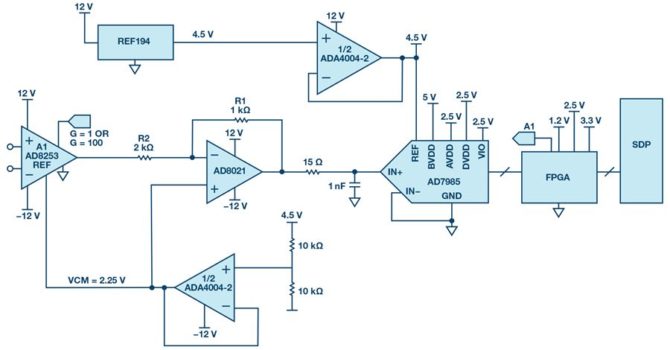

Rysunek 1. Przetwornik SAR z automatyczną regulacją wzmocnienia

Rysunek 1. Przetwornik SAR z automatyczną regulacją wzmocnienia

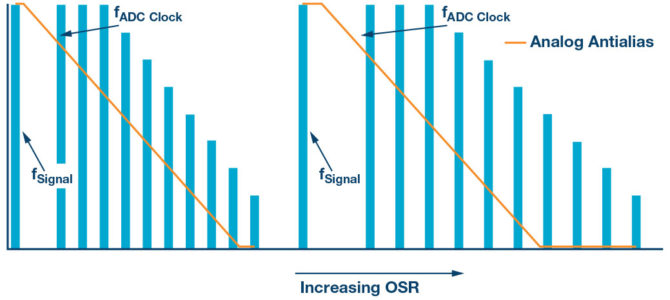

Obwód na rysunku 1 przedstawia 16-bitowy przetwornik SAR z szybkością próbkowania 2,5 MSPS i programowalnym wzmacniaczem, który ustawia wzmocnienie na 1 lub 100. Dzięki nadpróbkowaniu i cyfrowemu przetwarzaniu sygnału w FPGA, obwód ten osiąga zakres dynamiki wyższy niż 125 dB i nadal zachowuje bardzo niski poziom szumów. Wysoki zakres dynamiki uzyskuje się poprzez automatyczne przełączanie wzmocnienia AD8253 i poprzez nadpróbkowanie, kiedy sygnał jest próbkowany ze znacznie większą szybkością niż częstotliwość Nyquista. Z reguły podwojenie częstotliwości próbkowania poprawia stosunek sygnału do szumu (SNR) o około 3 dB w pierwotnym paśmie sygnału. W układzie na rysunku 1 zaimplementowano filtrowanie cyfrowe na FPGA tak, by usunąć szumy powyżej interesującego nas pasma. Zasada działania pokazana jest na rysunku 2.

By osiągnąć maksymalny zakres dynamiki, wzmacniacz instrumentalny jest wykorzystywany do stukrotnego wzmocnienia bardzo niskich sygnałów wejściowych. Kilka uwag dotyczących szumów w układzie przedstawiono poniżej:

Dla zakresu dynamicznego >126 dB, oczekujemy maksymalnego poziomu szumów 1 µV rms przy sygnale wejściowym 3 V (6 Vp-p). AD7985 to 16-bitowy przetwornik SAR z szybkością próbkowania 2,5 MSPS. Jeśli pracuje z szybkością 600 kSPS (przy małej mocy strat 11 mW) oraz nadpróbkowuje ze współczynnikiem 72, daje to częstotliwość próbkowania około 8 kSPS, a zatem pasmo 4 kHz. Z tych parametrów uzyskuje się maksymalną gęstość szumów (ND) 15,8 nV/√Hz. Wartość ta jest ważna przy wyborze właściwego wzmacniacza instrumentalnego. Wartość SNR w przetworniku ADC wynosi zazwyczaj 89 dB, podczas gdy nadpróbkowanie o współczynnik 72 daje dodatkowe 18 dB. W związku z tym do osiągnięcia poziomu 126 dB potrzebujemy jeszcze około 20 dB, co należy osiągnąć za pomocą wzmacniacza instrumentalnego. AD8253 oferuje szumy na poziomie 11 nV/√Hz przy wzmocnieniu 100. AD8021, używany jako sterownik przetwornika ADC oraz do regulacji poziomu, dodaje kolejne 2,1 nV/√Hz szumu.

Rysunek 2. Zwiększenie nadpróbkowania usuwa część szumu

Rysunek 2. Zwiększenie nadpróbkowania usuwa część szumu

Analogowy tor sygnałowy jest uzupełniony napięciem odniesienia REF194, a także ADA4004-2 jako buforem odniesienia i sterownikiem do generowania napięcia offsetu.

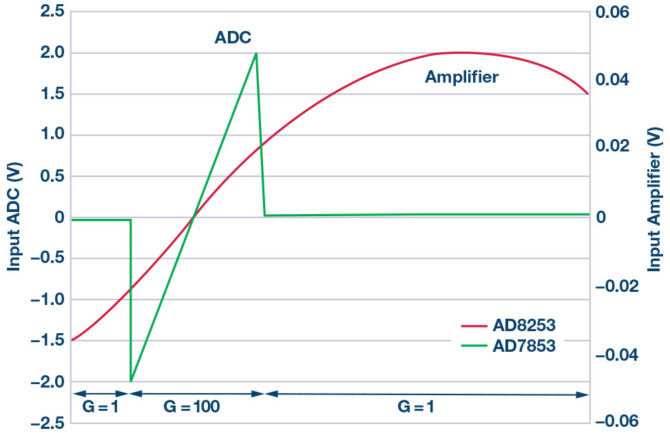

Oprócz elementów toru analogowego, ważny w działaniu obwodu jest układ FPGA (lub procesor). Jego kluczowe zadania to przełączanie wzmocnienia we wzmacniaczu instrumentalnym pomiędzy 1 a 100. Do tego celu zaprogramowano pewną liczbę wartości progowych, aby uniemożliwić przesterowanie ADC. Dzięki temu AD8253 pracuje ze wzmocnieniem 100 przy napięciach wejściowych do około 20 mV, co daje do maksimum 2,0 V na wejściu ADC. Następnie FPGA redukuje (bez opóźnienia) wzmocnienie AD8253 do 1, aby zapobiec przesterowaniu (patrz rysunek 3).

Rysunek 3. Przykład przełącznika wzmocnienia

Rysunek 3. Przykład przełącznika wzmocnienia

Warianty układu mogą być obsługiwane za pomocą innych przetworników ADC, takich jak AD7980 (16-bitowy, 1 MSPS), AD7982 (18-bitowy, 1 MSPS) lub AD7986 (18-bit, 2 MSPS). Podobnie, zamiast AD8253 ze wzmocnieniami 1, 10, 100 i 1000, można użyć wzmacniacza takiego jak AD8251 z niższymi wartościami wzmocnienia: 1, 2, 4 i 8. Możliwe są również zmiany w wyborze układu napięcia odniesienia.

Kompletny system rozwojowy można znaleźć pod adresem analog.com/CN0260.

Projekty inteligentnych sterowników przetwornic buck z tranzystorami GaN — część 1: Zagadnienia i pomiary

Projekty inteligentnych sterowników przetwornic buck z tranzystorami GaN — część 1: Zagadnienia i pomiary  Prof. Ryszard Tadeusiewicz: Sztuczna inteligencja wykorzystująca seks w komputerze

Prof. Ryszard Tadeusiewicz: Sztuczna inteligencja wykorzystująca seks w komputerze  Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)