[WARSZAWA, KRAKÓW] Seminarium „Akceleracja obliczeń na układach programowalnych”

EBV Elektronik i Xilinx zapraszają na seminarium dotyczące szybkich obliczeń na układach programowalnych. Wydarzenie odbędzie się w dniach 22.10 w Warszawie oraz 23.10 w Krakowie. Uczestnicy seminarium zapoznają się z technologiami umożliwiającymi akcelerację obliczeń na układach programowalnych (FPGA, SoC, ACAP) firmy Xilinx.

W czasie seminarium zaprezentowane zostaną:

- nowe zintegrowane środowisko programistyczne dla aplikacji C, C++, OpenCL, Python, (obsługuje zarówno gotowe karty Alveo jak i układy SoC, ACAP),

- nową architekturę układów – ACAP,

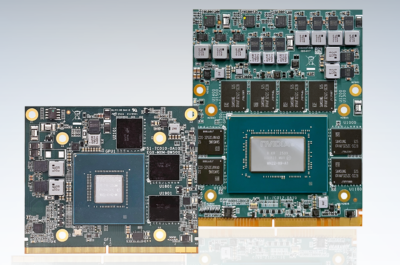

- gotowe karty oraz moduły „Embedded” – te dostępne już w sprzedaży (4 karty) oraz te planowane (Xilinx planuje wprowadzać na rynek ok. 3 nowe karty/rok),

- uruchomienie na układach Xilinxa własnego modelu sieci neuronowej opracowanego w środowisku TensorFlow lub Caffe,

- wiele przykładów akceleracji obliczeń realizowanych na gotowych kartach z układami FPGA (Hadoop, Apache Spark, CFD, SmartNIC, Crypto, GZIP, Monte Carlo, OpenCV, CNN itd.),

- jak wykorzystać możliwości FPGA z poziomu Python-a w układach Zynq SoC. (projekt PYNQ)

Wiele z tych rozwiązań nigdy wcześniej nie było prezentowanych w Europie.

Większość jest dostępna lub będzie jeszcze w tym roku (nowy software, układy Versal, karty Alveo, biblioteki akcelerowanych funkcji) .

Seminarium jest adresowane do:

- Programistów

- Projektantów oprogramowania do analizy baz danych

- Inżynierów pracujących nad rozwiązaniami z zakresu sztucznej inteligencji / uczenia maszynowego (szczególnie analizy obrazu)

- Programistów aplikacji „Embedded”

- Projektantów sprzętu

- Architektów systemów

- Wszystkich zainteresowanych najnowszą technologią umożliwiającą wydajne obliczenia i przetwarzanie dużych strumieni danych

Więcej informacji o wydarzeniu znajduje się na stronie seminarium.

Seminarium jest bezpłatne.

Linki do rejestracji:

Microchip rozszerza zakres usług bezpieczeństwa w ramach Trust Platform

Microchip rozszerza zakres usług bezpieczeństwa w ramach Trust Platform  ADLINK wprowadza moduły MXM oparte na architekturze NVIDIA Blackwell

ADLINK wprowadza moduły MXM oparte na architekturze NVIDIA Blackwell  Polski przemysł obronny stoi dziś w punkcie zwrotnym

Polski przemysł obronny stoi dziś w punkcie zwrotnym