Dobór odpowiedniego rezystora podciągającego/zwierającego do masy dla wyjść z otwartym drenem

Wiele układów scalonych zawiera wyprowadzenia cyfrowe, które wskazują status reszty systemu. Należą one do dwóch typów: otwarty dren (otwarty kolektor dla wyjść bipolarnych) lub push-pull (znany również jako układ przeciwsobny). Wyjścia typu otwarty dren są często wykorzystane, ponieważ mają kilka zalet w stosunku do konfiguracji przeciwsobnej. W przeciwieństwie do tej konfiguracji wyjścia typu otwarty dren mogą być łączone bezpośrednio, tworząc funkcję logiczną OR. Otwarty dren zapewnia również projektantowi większą swobodę, ponieważ może osiągnąć dowolny poziom napięcia dostępny w systemie – na przykład jako wejście procesora, który wymaga niższego poziomu napięcia, niż uzyskiwany w konfiguracji przeciwsobnej.

Przykładowe nazwy wyprowadzeń typu otwarty dren to Power Good (PG) czy Low Battery (LBO) w przypadku zasilaczy impulsowych, Reset oraz Power Fail (PFO) w monitorach zasilania (supply voltage supervisor, SVS), a także Low Battery, Power Fail i Reset w układach zasilania. Wszystkie wyjścia z otwartym drenem wymagają użycia zewnętrznego rezystora podciągającego (pull-up) lub zwierającego do masy (pull-down), który utrzyma wyjście w określonym stanie logicznym. Niniejszy artykuł opisuje wykorzystanie rezystora podciągającego, czynniki wpływające na wybór jednego z rozwiązań pull-up lub pull-down oraz sposób wyznaczania dopuszczalnego zakresu wartości rezystora.

Wprowadzenie

Układ SVS monitoruje napięcie zasilania systemu i wysyła sygnał resetujący, jeśli napięcie to spadnie poniżej określonego progu. Sygnał resetujący pojawia się na wyjściu z otwartym drenem, które wymaga rezystora podciągającego lub zwierającego do masy. Sam układ SVS też może mieć wyjście PFO typu otwarty dren. Pokazuje ono czy określone napięcie systemu spadło poniżej zadanego progu.

W przypadku zasilacza wyjście PG jest typowo używane do wysterowania wejścia włączającego inny układ scalony. Wyjście PG znajduje się w stanie niskim, gdy nominalne napięcie na wyjściu układu spada poniżej określonego ułamka wartości nominalnej. Następnie wyjście PG jest przywracane do stanu wysokiego przez zewnętrzny rezystor podciągający, gdy napięcie osiągnie zadany poziom. Zasilacze mogą również mieć wyjścia LBO, które wysyłają sygnał, gdy napięcie wejścia LBI spadnie poniżej określonego progu.

Kryteria wyboru rezystora

Pierwszą rzeczą, na którą należy zwrócić uwagę jest wybór rezystora podciągającego lub zwierającego do masy. Wybór zależy od tego, czy w przypadku wystąpienia zgłoszenia układ scalony wysterowuje wyjście stanem wysokim czy niskim. Przykładowo przetwornica obniżająca napięcie TPS62067 ma wyjście PG, które osiąga stan niski w przypadku, gdy napięcie wyjściowe nie jest poprawnie regulowane. Zatem wyjście PG wymaga rezystora podciągającego (pull-up). Wymusza on stan wysoki na wyprowadzeniu, gdy układ go nie wysterowuje – co oznacza, że zasilacz pracuje poprawnie. Z drugiej strony monitor napięcia TL7759 ma wyjście resetujące, które ustawia w stan wysoki, aby zakomunikować, że napięcie zasilania spadło poniżej zadanego progu. To wyjście resetujące wymaga rezystora zwierającego do masy (pull-down), który wymusi stan niski, gdy napięcie jest powyżej zadanego progu.

Aby określić wartość rezystora podciągającego lub zwierającego do masy, należy uwzględnić kilka czynników. Należą do nich: prąd upływu wyjścia, prąd upływu wejścia, do którego jest podłączone wyjście z otwartym drenem, napięcie podciągające podłączone do wyjścia, napięcie stanu niskiego lub wysokiego zarówno pinu wyjściowego jak i wejściowego, a także prąd testowy zapewniający niski lub wysoki poziom logiczny. Pierwszy przykład wykorzystuje przetwornicę obniżającą napięcie TPS62067 i pokazuje, kiedy potrzebny jest rezystor podciągający oraz jak wyznaczyć jego wartość. Drugi przykład wykorzystuje monitor napięcia TL7759 i pokazuje, kiedy stosować rezystor zwierający do masy i jak obliczyć zakres jego wartości.

Obliczenie wartości rezystora podciągającego

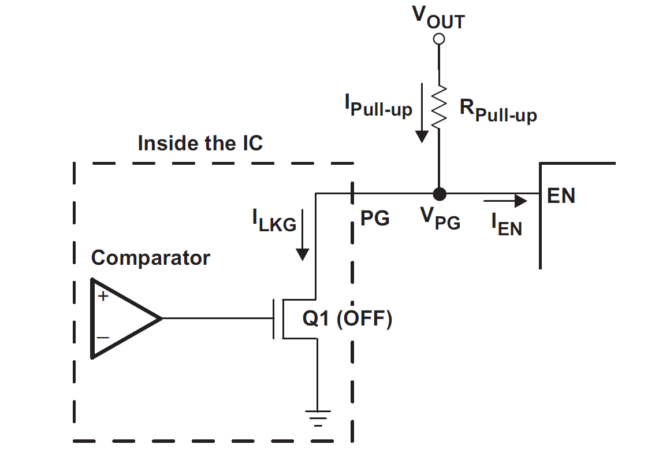

Rysunek 1 przedstawia typowy układ wyjścia PG. Wyjście PG jest podłączone do napięcia wyjściowego Vout przez rezystor podciągający RPull-up oraz do wejścia włączającego (EN) kolejnego układu.

Rysunek 1. Typowy schemat zastępczy dla wyjścia PG (stan wysoki przy nieaktywnym wyjściu PG)

Rysunek 1. Typowy schemat zastępczy dla wyjścia PG (stan wysoki przy nieaktywnym wyjściu PG)

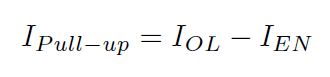

Obwód na rysunku 1 zostanie przeanalizowany, aby znaleźć maksymalną wartość rezystora RPull-up, gdy napięcie jest poprawne (power good), a tranzystor Q1 Jest wyłączony. Pomimo wyłączenia tranzystora Q1 płynie przez niego pewien prąd upływu podany w karcie katalogowej. Prąd o podanej wartości ILKG jest jednocześnie prądem upływu pinu PG. Prąd upływu powoduje spadek napięcia na rezystorze podciągającym. Zatem napięcie na wyprowadzeniu PG i dołączonym do niego wejściu EN jest mniejsze, niż Vout. Do wyznaczenie maksymalnej wartości opornika Rpull-up została użyta maksymalna wartość prądu ILKG, ponieważ będzie ona powodować największy spadek napięcia na rezystorze RPull-up. Ponieważ wyjście PG jest połączone z wejściem EN kolejnego układu, również do wejścia EN będzie wpływał prąd. Tą wartość można znaleźć w karcie katalogowej układu scalonego – jest oznaczona jako IEN na rysunku 1. Wzór 1 pozwala wyznaczyć wartość prądu rezystora IPull-up z prawa Kirchoffa:

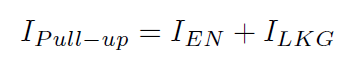

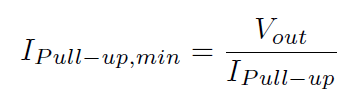

Maksymalną wartość rezystora podciągającego można wyznaczyć ze wzoru 2. W tej sytuacji napięcie na wyprowadzeniu PG VPG jest równe napięciu na wejściu EN VIH. VIH jest minimalnym napięciem, które zostanie odczytane jako stan wysoki.

Maksymalną wartość rezystora podciągającego można wyznaczyć ze wzoru 2. W tej sytuacji napięcie na wyprowadzeniu PG VPG jest równe napięciu na wejściu EN VIH. VIH jest minimalnym napięciem, które zostanie odczytane jako stan wysoki.

Jest to wartość maksymalna, ponieważ wybór większego opornika spowoduje większy spadek napięcia na rezystorze RPull-up. Wówczas napięcie VPG byłoby niższe od minimalnej wartości VIH. Innymi słowy, podłączony układ nie rozpoznałby napięcia PG jako stanu wysokiego.

Jest to wartość maksymalna, ponieważ wybór większego opornika spowoduje większy spadek napięcia na rezystorze RPull-up. Wówczas napięcie VPG byłoby niższe od minimalnej wartości VIH. Innymi słowy, podłączony układ nie rozpoznałby napięcia PG jako stanu wysokiego.

Wartość minimalna

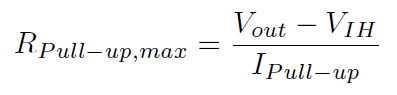

Rysunek 2 pokazuje ten sam obwód, co poprzednio, gdy tranzystor Q1 jest włączony, a wyjście PG jest w stanie niskim. Oznacza to, że napięcie wyjściowe jest poniżej dopuszczalnego poziomu i zasilacz nie pracuje poprawnie.

Rysunek 2. Typowy schemat zastępczy dla PG w stanie niskim

Rysunek 2. Typowy schemat zastępczy dla PG w stanie niskim

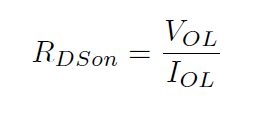

Do wyznaczenia minimalnej wartości RPull-up przyjęto założenie, że tranzystor Q1 jest włączony, co widać na rysunku 2. Zatem napięcie VPG jest zwarte do masy. W rzeczywistości tranzystor Q1 ma rezystancję RDSon, która powoduje pewien spadek napięcia – zatem napięcie PG jest nieco powyżej potencjału masy. Gdy tranzystor Q1 jest łączony, napięcie PG musi być wystarczająco niskie, aby dołączony układ scalony odczytał je jako stan niski.

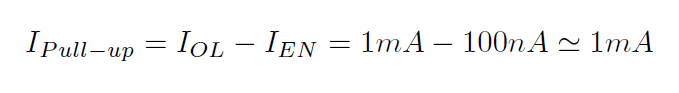

Aby wyznaczyć prąd rezystora podciągającego wymagana jest znajomość prądu IOL. Wartość ta znajduje się w karcie katalogowej układu i stanowi prąd używany podczas testów dla napięcia wyjściowego w stanie niskim VOL. Ustalając maksymalny prąd płynący przez Q1 równy prądowi testowemu opisanemu w karcie katalogowej uzyskujemy pewność, że VOL nie przekroczy maksymalnej dopuszczalnej wartości napięcia przy tym prądzie. Można stosować prądy do maksymalnej dopuszczalnej wartości pobieranej przez PG. Tym niemniej mogłyby one doprowadzić do powstania napięcia VOL powyżej określonej wartości maksymalnej.

W przypadku układu TPS62067, prąd dla napięcia testowego VOL i maksymalny prąd pobierany przez PG są równe. Nie musi tak być jednak zawsze.

Wzory

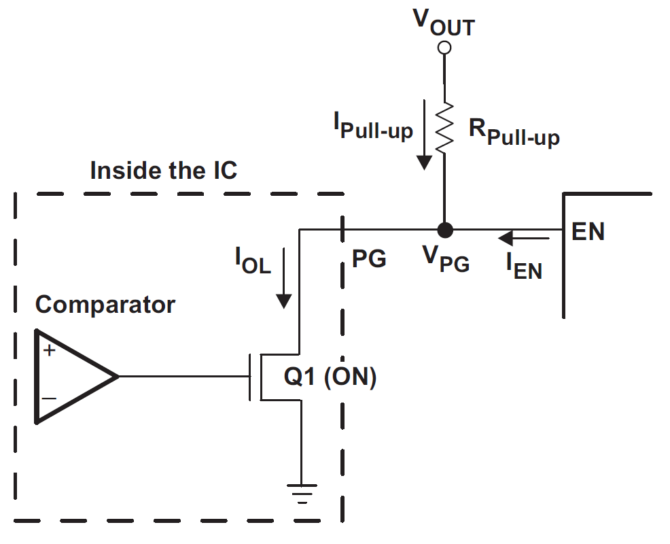

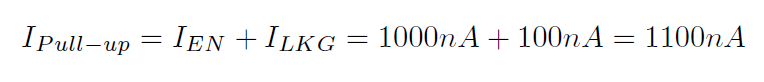

Wzór 3 korzysta z prawa Kirhoffa, aby na podstawie prądu testowego układu scalonego oraz prądu upływu wyznaczyć prąd płynący przez rezystor podciągający.

Napięcie na rezystorze podciągającym jest równe Vout minus VPG. Karta katalogowa wymienia maksymalną wartość VPG oznaczoną jako VOL i zazwyczaj równą 0,3 lub 0,4 V. Może ona być równa 0 V, co przekłada się na wyższy prąd płynący przez rezystor niż dla maksymalnego dopuszczalnego napięcia. Zatem minimalna wartość rezystora podciągającego jest opisana wzorem 4:

Napięcie na rezystorze podciągającym jest równe Vout minus VPG. Karta katalogowa wymienia maksymalną wartość VPG oznaczoną jako VOL i zazwyczaj równą 0,3 lub 0,4 V. Może ona być równa 0 V, co przekłada się na wyższy prąd płynący przez rezystor niż dla maksymalnego dopuszczalnego napięcia. Zatem minimalna wartość rezystora podciągającego jest opisana wzorem 4:

Wynikiem obliczeń jest wartość minimalna, ponieważ wybór mniejszej wartości RPull-up skutkuje większym prądem płynącym przez tranzystor Q1, niż prąd w warunkach testowych. Jeśli przez Q1 płynie prąd o wyższej wartości, spadek napięcia na tranzystorze Q1 jest większy i niepewny. Wzory 2 oraz 4 określają zakres dopuszczalnych wartości rezystora podciągającego RPull-up na wyjściu pinu PG.

Wynikiem obliczeń jest wartość minimalna, ponieważ wybór mniejszej wartości RPull-up skutkuje większym prądem płynącym przez tranzystor Q1, niż prąd w warunkach testowych. Jeśli przez Q1 płynie prąd o wyższej wartości, spadek napięcia na tranzystorze Q1 jest większy i niepewny. Wzory 2 oraz 4 określają zakres dopuszczalnych wartości rezystora podciągającego RPull-up na wyjściu pinu PG.

W sytuacji, gdy stan wyjścia PG jest niski, maksymalne dopuszczalne napięcie VPG zależy od tego, czy VOL jest wyższe, czy niższe od VIL – maksymalnego napięcia stanu niskiego dla pinu EN dołączonego układu. Jeśli VOL jest wyższe od VIL, praca w takich warunkach nie jest pewna. Wtedy maksymalne dopuszczalne napięcie VIL jest niższe od najwyższego gwarantowanego napięcia pinu PG, VOL. W takiej sytuacji minimalna wartość rezystancji obliczona we wzorze 4 powinna być znacznie zwiększona, aby zachować margines napięcia PG. Dzięki temu napięcie wyjścia PG w stanie niskim będzie wystarczająco małe, aby zarejestrować stan niski w dołączonym układzie. Ponieważ opisane zachowanie jest pożądane, w obliczeniach przyjęto, że VOL jest niższe od VIL.

Wyznaczenie zakresu RPull-up dla układu TPS62067

W tabeli 1 wymieniono wartości dotyczące wyjścia PG zaczerpnięte z karty katalogowej układu TPS62067 (SLVS8333A), natomiast tabela 2 zawiera wartości dotyczące wejścia IC dla tego samego układu. Są one wykorzystywane do obliczenia zakresu wartości rezystora podciągającego na wyjściu PG. W tym przykładzie wyjście PG układu TPS62067 wysterowuje wejście EN innego układu TPS62067.

Tabela 1. Wyjście PG układu scalonego

| Dane katalogowe TPS62067 | |

| Parametr | Wartość |

| Układ | TPS62067 |

| Pin | Power Good (PG) |

| IOL | 1 mA |

| ILKG(max) | 100 nA |

| VOL(max) | 0,3 V |

Tabela 2. Wejście EN układu scalonego

| Dane katalogowe TPS62067 | |

| Parametr | Wartość |

| Układ | TPS62067 |

| Pin | Enable (EN) |

| VIH(min) | 1,0 V |

| IEN(max) | 1000 nA |

| VIL(max) | 0,4 V |

Metoda obliczeń

Najpierw za pomocą wzoru 1 i wartości IEN oraz ILKG wyznaczamy prąd IPull-up płynący przez rezystor podciągający.

Po wyznaczeniu prądu IPull-up można obliczyć maksymalną wartość RPull-up, korzystając ze wzoru 2. Została użyta przykładowa wartość napięcia wyjściowego Vout równa 1,8 V.

Po wyznaczeniu prądu IPull-up można obliczyć maksymalną wartość RPull-up, korzystając ze wzoru 2. Została użyta przykładowa wartość napięcia wyjściowego Vout równa 1,8 V.

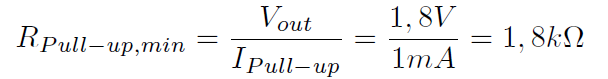

Kolejnym krokiem jest wyznaczenie minimalnej wartości rezystora podciągającego. Wzór 3 pozwala określić prąd płynący przez ten rezystor:

Kolejnym krokiem jest wyznaczenie minimalnej wartości rezystora podciągającego. Wzór 3 pozwala określić prąd płynący przez ten rezystor:

Ta wartość pozwala określić minimalną wartość rezystora RPull-up ze wzoru 4.

Ta wartość pozwala określić minimalną wartość rezystora RPull-up ze wzoru 4.

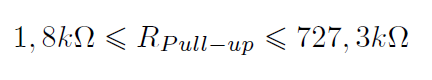

Zatem otrzymany zakres wartości rezystora podciągającego to:

Zatem otrzymany zakres wartości rezystora podciągającego to:

Obliczenie zakresu wartości rezystora zwierającego do masy

Obliczenie zakresu wartości rezystora zwierającego do masy

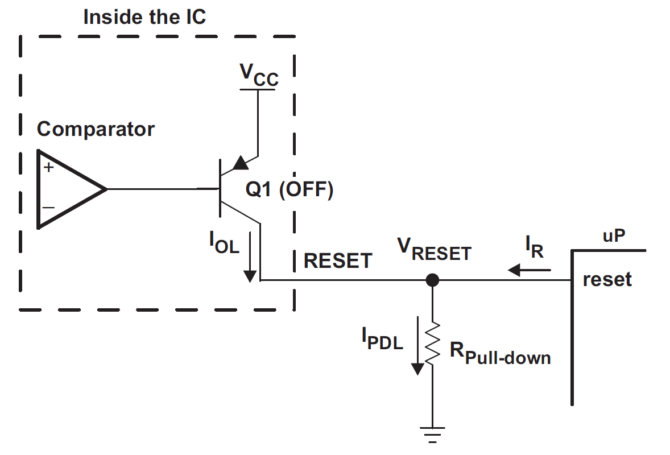

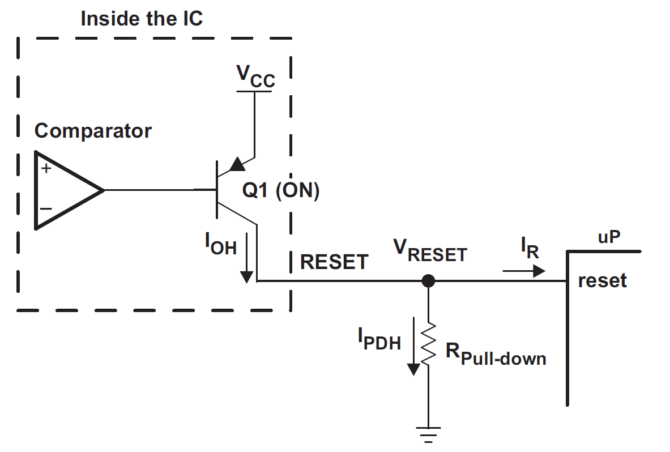

Rysunek 3 przedstawia wyjście resetujące układu połączone z masą poprzez rezystor zwierający RPull-down. Pin resetu podłączono do wejścia resetującego mikrokontrolera lub mikroprocesora.

Rysunek 3. Równoważny schemat obwodu resetującego (wyjście nieaktywne w stanie niskim)

Rysunek 3. Równoważny schemat obwodu resetującego (wyjście nieaktywne w stanie niskim)

Obwód na rysunku 3 pozwala wyznaczyć maksymalną wartość RPull-down, gdy wyjście resetujące jest w stanie niskim, a tranzystor Q1 jest wyłączony. Pomimo wyłączenia tranzystora płynie przez niego pewien prąd upływu podany w karcie katalogowej jako IOL. Jest to prąd płynący w stanie niskim przy włączonym sygnale reset, który powoduje spadek napięcia na rezystorze podciągającym. Z tego powodu napięcie na wyjściu resetującym oraz napięcie na dołączonym wejściu jest większe od zera. Występuje również prąd płynący przez wejście resetujące procesora. Jego wartość można znaleźć w karcie katalogowej procesora – to prąd upływu wejścia resetującego oznaczony jako IR na rysunku 3.

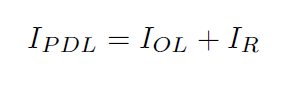

Wzór 10 pozwala na podstawie prawa Kirhoffa wyznaczyć prąd płynący przez rezystor zwierający IPDL, gdy wyjście resetujące jest zwarte do masy.

Napięcie VIL można znaleźć w karcie katalogowej procesora – jest to maksymalna wartość odpowiadająca stanowi niskiemu na wejście resetującym. Oznacza to maksymalną wartość, którą procesor rozpozna jako stan niski sygnału resetującego. Wzór 11 wykorzystuje prawo Ohma, aby wyznaczyć maksymalną wartość opornika RPull-down.

Napięcie VIL można znaleźć w karcie katalogowej procesora – jest to maksymalna wartość odpowiadająca stanowi niskiemu na wejście resetującym. Oznacza to maksymalną wartość, którą procesor rozpozna jako stan niski sygnału resetującego. Wzór 11 wykorzystuje prawo Ohma, aby wyznaczyć maksymalną wartość opornika RPull-down.

Wartość minimalna

Rysunek 4 jest taki sam, jak rysunek 3. Jedyną różnicą jest to, że tranzystor Q1 jest włączony, a wyjście resetujące jest w stanie wysokim. Oznacza to, że napięcie widziane przez układ monitora jest mniejsze od określonego progu, a procesor należy zresetować.

Rysunek 4. Równoważny schemat obwodu resetującego (wyjście nieaktywne w stanie wysokim)

Rysunek 4. Równoważny schemat obwodu resetującego (wyjście nieaktywne w stanie wysokim)

Wzory

Na podstawie rysunku 4 można wyznaczyć minimalną wartość opornika RPull-down. Tranzystor Q1 jest włączony, zatem punkt VRESET jest zwarty do zasilania VCC. W rzeczywistości na tranzystorze odkłada się napięcie nasycenia, przez co VRESET jest niższe od VCC. Napięcie VRESET musi być wystarczająco wysokie, aby zostało odczytane jako stan wysoki przez wejście dołączonego układu. Karta katalogowa układu scalonego zawiera wartość napięcia wyjściowego odpowiadającą stanowi wysokiemu VOH przy pewnym prądzie testowym IOH. Zapewnia to poprawną pracę – VOH nigdy nie spadnie poniżej określonego minimum. Można pracować z prądami do maksymalnej wartości określonej przez IOH. Tym niemniej mogą one powodować spadek wartości VOH poniżej wymaganego minimum. Wzór 12 wykorzystuje prawo Kirhoffa. Na podstawie prądu testowego układu i prądu upływu kolejnego dołączonego układu pozwala wyznaczyć prąd płynący przez rezystor zwierający do masy.

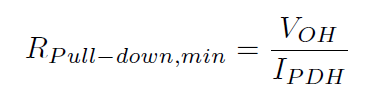

Po obliczeniu wartości IPDH można skorzystać ze wzoru 13, aby wyznaczyć minimalna wartość rezystora zwierającego do masy.

Po obliczeniu wartości IPDH można skorzystać ze wzoru 13, aby wyznaczyć minimalna wartość rezystora zwierającego do masy.

Gdy wyjście resetujące jest w stanie wysokim, minimalne dopuszczalne napięcie VRESET zależy od tego, czy VOH jest wyższe, czy niższe niż VIH – minimalne napięcie rozpoznawane przez wejście resetujące jako stan wysoki. Jeśli napięcie VOH jest wyższe niż VIH, poprawna praca nie jest możliwa. Minimalne wymagane napięcie VIH jest bowiem wyższe, niż dane najniższe napięcie na wyjściu resetującym VOH. W takiej sytuacji minimalna wartość rezystora wyliczona ze wzoru 13 powinna być znacznie zwiększona, aby zachować margines napięcia resetującego. Dzięki temu napięcie na wyjściu resetującym będzie wystarczająco wysokie, aby zostać zarejestrowane jako stan wysoki przez podłączony układ. Ponieważ wymagana jest pewna praca, w obliczeniach przyjęto, że VOH jest wyższe, niż VIH.

Gdy wyjście resetujące jest w stanie wysokim, minimalne dopuszczalne napięcie VRESET zależy od tego, czy VOH jest wyższe, czy niższe niż VIH – minimalne napięcie rozpoznawane przez wejście resetujące jako stan wysoki. Jeśli napięcie VOH jest wyższe niż VIH, poprawna praca nie jest możliwa. Minimalne wymagane napięcie VIH jest bowiem wyższe, niż dane najniższe napięcie na wyjściu resetującym VOH. W takiej sytuacji minimalna wartość rezystora wyliczona ze wzoru 13 powinna być znacznie zwiększona, aby zachować margines napięcia resetującego. Dzięki temu napięcie na wyjściu resetującym będzie wystarczająco wysokie, aby zostać zarejestrowane jako stan wysoki przez podłączony układ. Ponieważ wymagana jest pewna praca, w obliczeniach przyjęto, że VOH jest wyższe, niż VIH.

Wyznaczenie zakresu RPull-down dla układu TL7759

Tabela 3 zawiera wartości dotyczące wyjścia resetującego zaczerpnięte z karty katalogowej TL7759. Natomiast tabela 4 – typowe wartości IR oraz VIL dotyczące wejścia resetującego. Wartości z obu tabel wykorzystano do obliczenia zakresu wartości rezystora zwierającego wyjście resetujące do masy.

Tabela 3. Wyjście resetujące układu scalonego

| Dane katalogowe TL7759 | |

| Parametr | Wartość |

| Układ | TL7759 |

| Pin | Reset (wyjście) |

| VCC | 5 V |

| IOL(max) | 1 μA |

| IOH(min) | 4 V |

| IOH | 8 mA |

Tabela 4. Wejście resetujące układu scalonego

| Dane przykładowe | |

| Parametr | Wartość |

| Pin | Reset (wejście) |

| VIL(max) | 0,3 V |

| IR(max) | 100 nA |

| VIH(min) | 3 V |

Metoda obliczania

Najpierw za pomocą wzoru 10 oraz znanych wartości IOL oraz IR oraz wyznaczamy prąd IPDL.

Następnie wzór 11 pozwala obliczyć maksymalną wartość rezystora zwierającego do masy.

Następnie wzór 11 pozwala obliczyć maksymalną wartość rezystora zwierającego do masy.

Kolejnym krokiem jest użycie zależności 12 do wyznaczenia wartości IPDH.

Kolejnym krokiem jest użycie zależności 12 do wyznaczenia wartości IPDH.

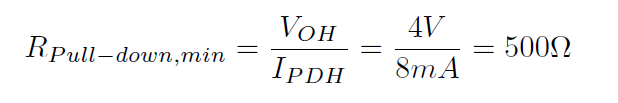

W końcu korzystamy ze wzoru 13, aby wyznaczyć minimalną wartość rezystora:

W końcu korzystamy ze wzoru 13, aby wyznaczyć minimalną wartość rezystora:

Ostateczny wynik określa zakres wartości rezystora zwierającego do masy:

Ostateczny wynik określa zakres wartości rezystora zwierającego do masy:

Inne kryteria wyboru

Inne kryteria wyboru

Powyższe przykłady wykorzystują parametry wzięte z karty katalogowej, aby zapewnić poprawną pracę – na przykład niskie napięcie wyjściowe dla określonego prądu testowego. Jeśli prąd pochłaniany przez wyjście PG jest niższy od prądu testowego, spadek napięcia na tranzystorze FET na wyjściu PG również jest niższy, a zatem niższe jest napięcie wyjściowe.

Jeśli jednak prąd pochłaniany przez pin PG jest wyższy od prądu testowego, napięcie na wyjściu PG może okazać się wyższe, niż zadane – wówczas stan logiczny nie będzie odczytany poprawnie. Z tego powodu wartość prądu testowego zawsze wyznacza maksymalny dopuszczalny prąd w powyższych obliczeniach – określa maksymalny prąd na wyjściu. Można stosować prądy poniżej maksymalnej dopuszczalnej wartości, ale wówczas napięcie na wyjściu PG lub resetującym nie musi już znaleźć się w zadanym zakresie. Aby oszacować napięcie na wyjściu PG przy prądach wyższych, niż prąd testowy, trzeba najpierw wyznaczyć rezystancję włączenia RDSon wewnętrznego tranzystora FET. Wynika ona z maksymalnego napięcia na wyjściu PG w stanie niskim VOL oraz prądu testowego IOL.

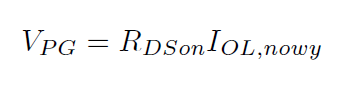

Wówczas napięcie na wyjściu PG jest po prostu iloczynem RDSon oraz nowego prądu wpływającego.

Wówczas napięcie na wyjściu PG jest po prostu iloczynem RDSon oraz nowego prądu wpływającego.

To napięcie powinno być niższe od VIL, aby uzyskać odczyt stanu niskiego. Inną możliwością jest obecność wykresu napięcia wyjścia PG lub resetu od prądu w karcie katalogowej. Wykresy te pokazują typowe zachowanie i podobnie jak obliczona wartość RDSon nie gwarantują pewnej pracy.

To napięcie powinno być niższe od VIL, aby uzyskać odczyt stanu niskiego. Inną możliwością jest obecność wykresu napięcia wyjścia PG lub resetu od prądu w karcie katalogowej. Wykresy te pokazują typowe zachowanie i podobnie jak obliczona wartość RDSon nie gwarantują pewnej pracy.

Wady i zalety doboru wartości skrajnych

Po wyznaczeniu zakresu wartości rezystora podciągającego lub zwierającego do masy warto wziąć pod uwagę inne czynniki, które wskazują na wybór określonej wartości z tego zakresu. Jednym z czynników, który skłania do wyboru większego rezystora jest pobór mocy przez tenże rezystor zasilany przez układ. Jeśli na przykład użyty jest minimalny rezystor zwierający o wartości 500 Ω, a napięcie nasycenia tranzystora bipolarnego osiąga maksymalną wartość 1 V, na rezystorze odkłada się napięcie Vcc – 1 V. Jeśli Vcc jest równe 5 V, spadek napięcia 4 V odłożony na rezystorze RPull-down powoduje przepływ prądy 8 mA, co oznacza 32 mW traconej mocy oraz dodatkowe 8 mW w sterującym tranzystorze bipolarnym. Całkowita strata mocy Vcc*Isink może w pewnych zastosowaniach być istotna, co sugeruje wybór rezystora o większej wartości.

Istnieją jednak słabe strony wyboru największego możliwego rezystora podciągającego. Większa rezystancja zwiększa impedancję, co czyni obwód bardziej wrażliwym na szumy lub przesłuchy innych sygnałów biegnących na płytce. Jest to problemem zwłaszcza w przypadku długich ścieżek z otwartym drenem prowadzonych na duże odległości.

Innym problemem przy wyborze dużego rezystora jest pojemność pasożytnicza wyjścia z otwartym drenem. Może się pojawić z powodu innych podłączonych wyjść typu otwarty dren, wejść innych układów lub sąsiednich ścieżek zawierających kondensator. Duża pojemność tworzy obwód RC, który ma pewien czas narastania i opadania. Praca gotowego układu może zostać zaburzona, jeśli czasy narastania i opadania okażą się dłuższe niż normalnie.

Podsumowanie

Wyjścia typu otwarty dren występujące w układach zasilania wymagają rezystorów podciągających lub zwierających do masy, aby utrzymać wyjście logiczne w określonym stanie. Dopuszczalny zakres wartości rezystora można wyliczyć na podstawie analizy obwodu i parametrów dostępnych w karcie katalogowej układu. Wybór odpowiedniej wartości rezystora z wyznaczonego zakresu daje pewność, że stan wyjścia jest prawidłowo odczytywany przez wejście kolejnego układu. Zakres dopuszczalnych wartości daje pewną swobodę w wyborze konkretnego opornika, co pozwala na przykład na użycie rezystorów o wartościach już występujących w projekcie. Metody i równania przedstawione w nocie aplikacyjnej pozwalają wyznaczyć dopuszczalny zakres wartości rezystorów i umożliwiają projektantowi na wybór takiej, która najlepiej pasuje do konkretnego systemu.

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485