Eksperymenty z pętlą synchronizacji fazowej (PLL)

Zamieszczamy opis prostego eksperymentu z użyciem uniwersalnego środowiska pomiarowego ADALM2000. Tematem ćwiczenia są pomiary pętli synchronizacji fazowej (PLL).

Cel

Pętla synchronizacji fazowej ma we współczesnej elektronice szerokie zastosowania. Można ją znaleźć m.in. w układach modulacji/demodulacji sygnału (głównie chodzi o modulację częstotliwości i fazy), układach synchronizacji i odzyskiwania danych, układach generowania sygnałów zegarowych, a także w układach mnożenia i syntezie częstotliwości. W ćwiczeniu skonfigurujemy prosty układ PLL, co pozwoli zrozumieć zasadę działania PLL.

Podstawy

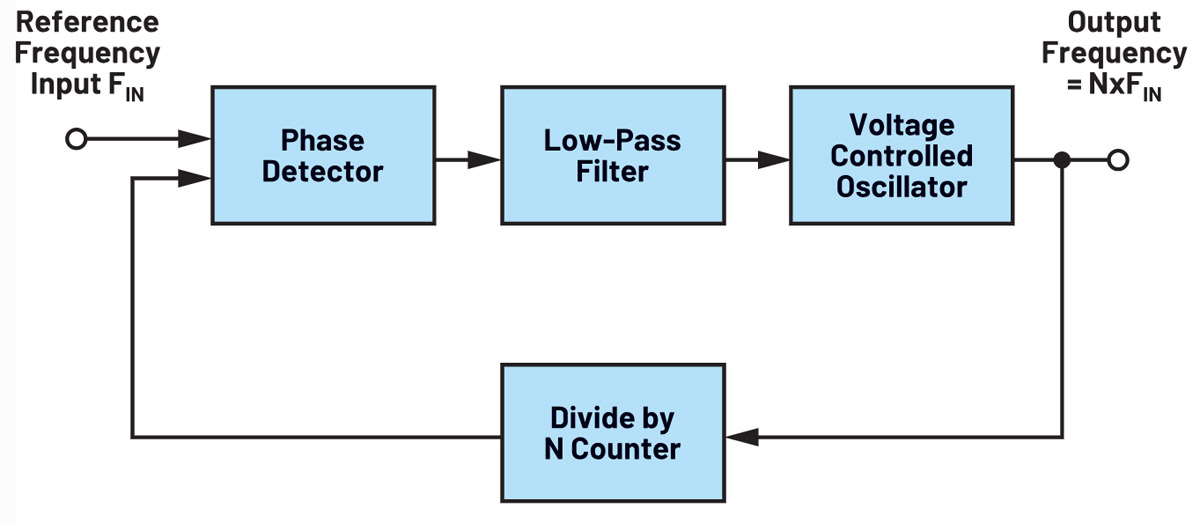

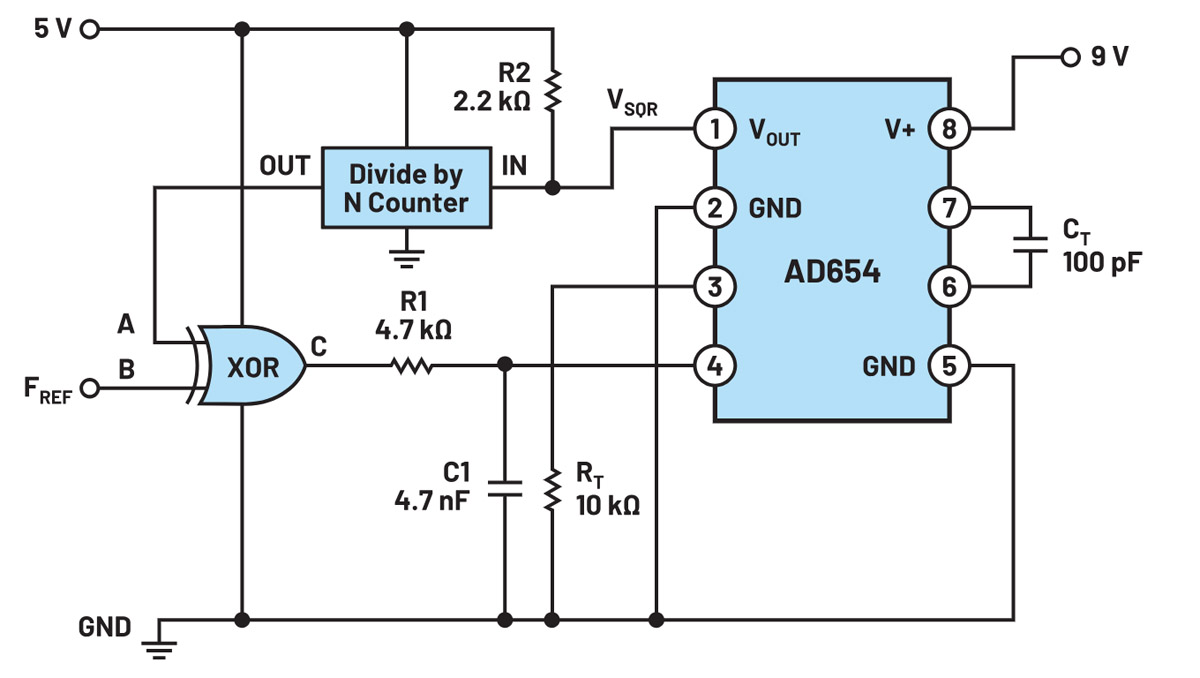

PLL to układ sprzężenia zwrotnego, który działa w celu dostosowania lub zablokowania różnicy faz między wyjściem generatora sterowanego napięciem (VCO) a wejściowym sygnałem odniesienia, jak pokazano na rys. 1. VCO to generator, którego częstotliwość wyjściowa jest funkcją pewnego wejściowego napięcia sterującego. W ogólnym przypadku, gdy VCO jest używany w pętli sprzężenia zwrotnego, takiej jak PLL, funkcja przenoszenia napięcia na częstotliwość musi być co najmniej monotoniczna. W rozpatrywanym przypadku VCO jest przetwornikiem napięcia na częstotliwość (VFC), w którym charakterystyka napięcie/częstotliwość jest liniowa. Współczynnik podziału N dzielnika częstotliwości w pętli sprzężenia zwrotnego jest na ogół liczbą całkowitą, w tym 1, co jest równoznaczne z brakiem dzielnika lub bezpośrednim połączeniem z wyjścia VCO do wejścia detektora fazy.

Rys. 1. Podstawowy schemat blokowy PLL

Teoria opisująca PLL jest bardzo obszerna i jest opisana w wielu publikacjach. Trudno w krótkim artykule opisać wszystkie zagadnienia związane z tą tematyką. Na końcu zamieszczamy kilka odniesień do literatury.

Materiały

Czytelnicy dysponującym zestawem ADALM2000 będą mogli wykonać samodzielnie opisany niżej eksperyment. Potrzebne będą do tego:

- Zestaw ADALM2000

- Płytka stykowa

- Przewody połączeniowe

- Rezystor 2,2 kΩ

- Rezystor 47 kΩ

- Rezystor 10 kΩ

- Kondensator 4,7 nF (oznaczony 472)

- Kondensator 100 pF (oznaczony 101)

- Układ CMOS CD4007

- Tranzystor ZVN2110A NMOS – 2 szt.

- Tranzystor ZVP2110A PMOS – 2 szt.

- Układ AD654 VFC

- Bateria 9 V (ze złączem)

Krok 1 Wskazówki

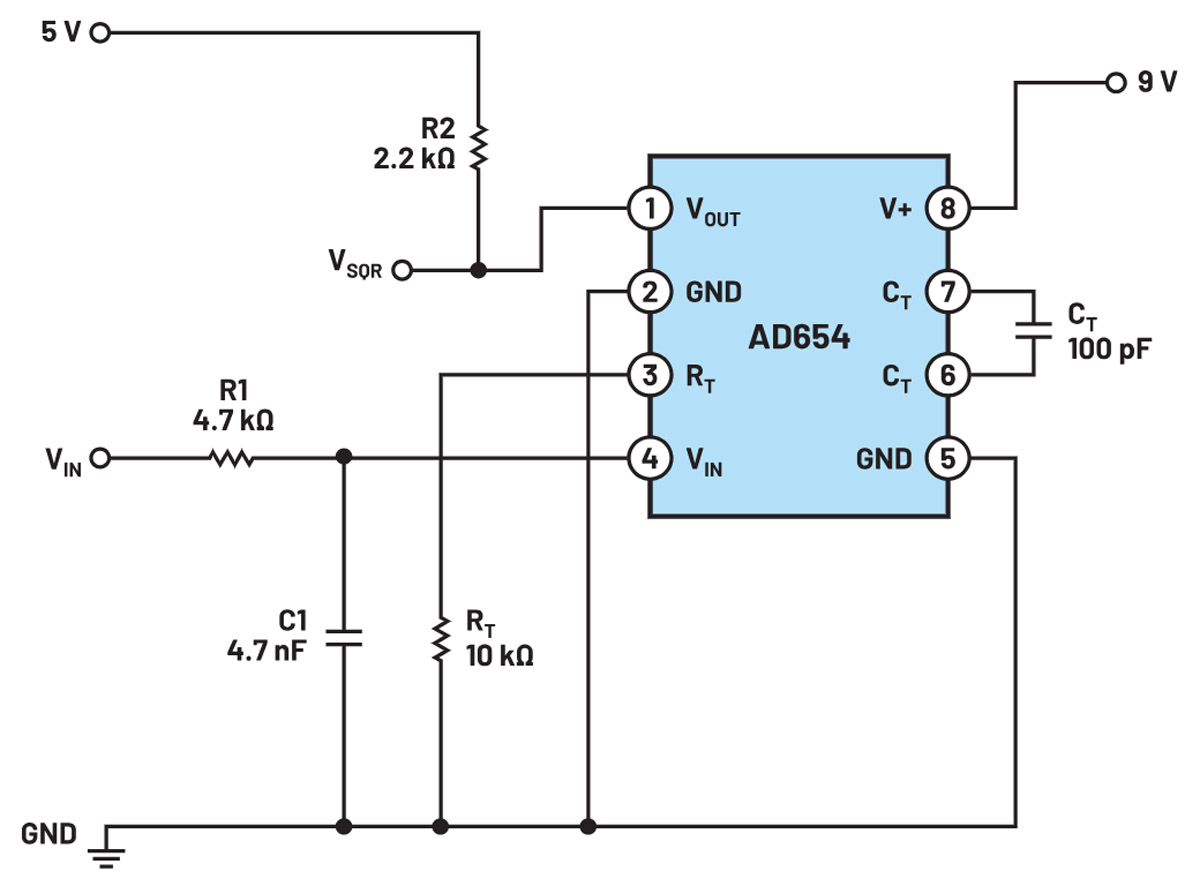

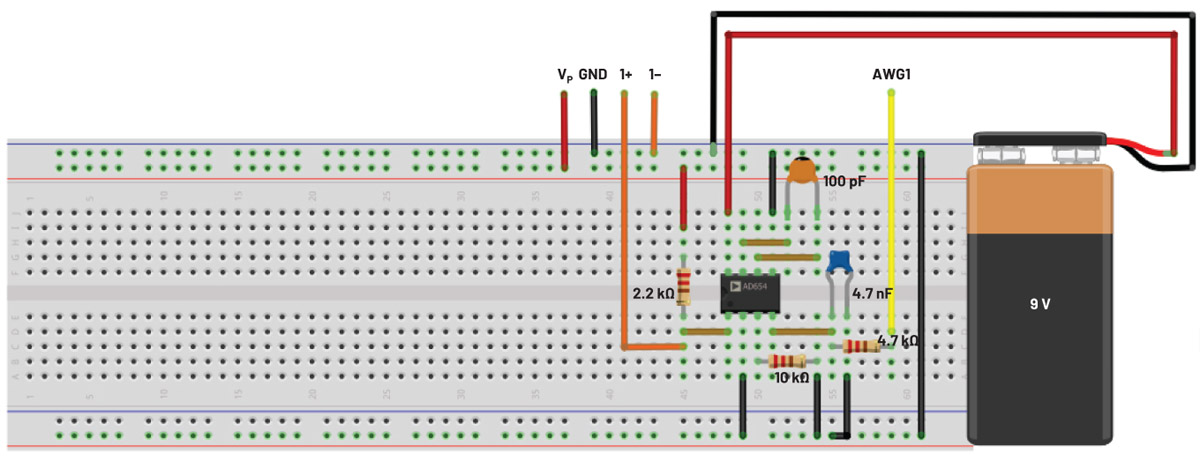

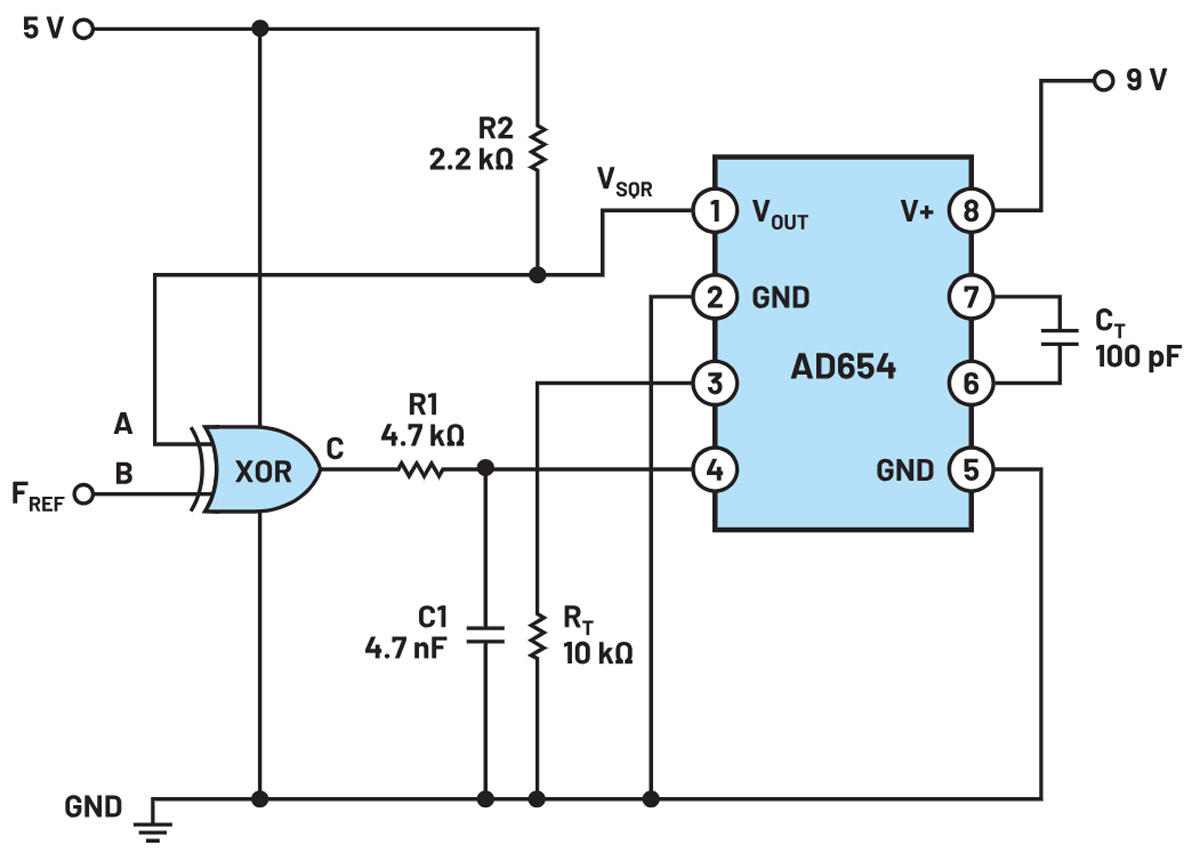

Na płytce drukowanej bez lutowania najpierw należy zmontować układ VFC oparty na AD654 pokazanym na rys. 2. Elementy należy umieścić np. z prawej strony płytki zostawiając miejsce na inne części PLL. Będą one dodane w późniejszych etapach ćwiczenia. Napięcie sterujące jest podawane przez jednobiegunowy filtr dolnoprzepustowy składający się z rezystora R1 i kondensatora C1. Jest to odpowiednik bloku filtra dolnoprzepustowego, który steruje blokiem VCO na rys. 1.

Konfiguracja sprzętu

Włączamy stałe napięcie zasilające 5 V i dołączamy do układu dodatkowo baterię 9 V. Podłączamy wyjście AWG1 do VIN, jak pokazano na rys. 2. Generator AWG1 powinien być skonfigurowany jako źródło napięcia stałego. Początkowo ustawiamy 2,5 V. Podłączamy wejście kanału CH1+ oscyloskopu do wyjścia VSQR, jak pokazano na rys. 2. Należy ponadto uziemić wejście CH1-.

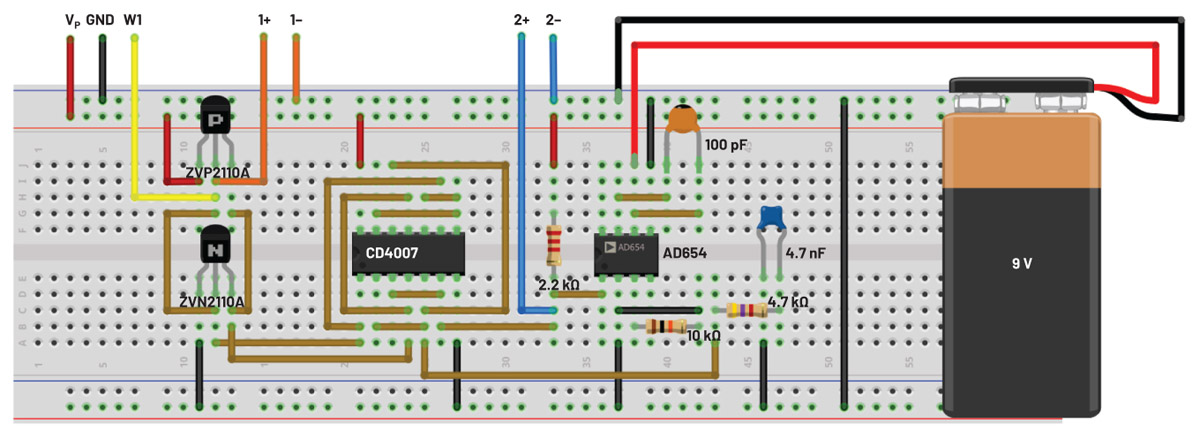

Rys. 3. Obwód VFC na płytce drukowanej

Procedura

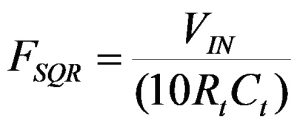

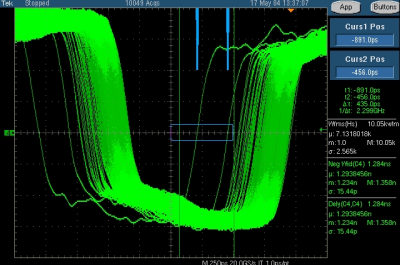

Korzystając z suwaka ustawiającego offset DC AWG 1 ustawiamy napięcie VIN od 1 V do 4 V, obserwując częstotliwość wyjścia VFC na VSQR. W tym celu należy użyć funkcji pomiaru częstotliwości na ekranie sterowania zakresem. Rt i Ct na rys. 2 ustawiają nominalną częstotliwość wyjściową VFC zgodnie z równaniem:

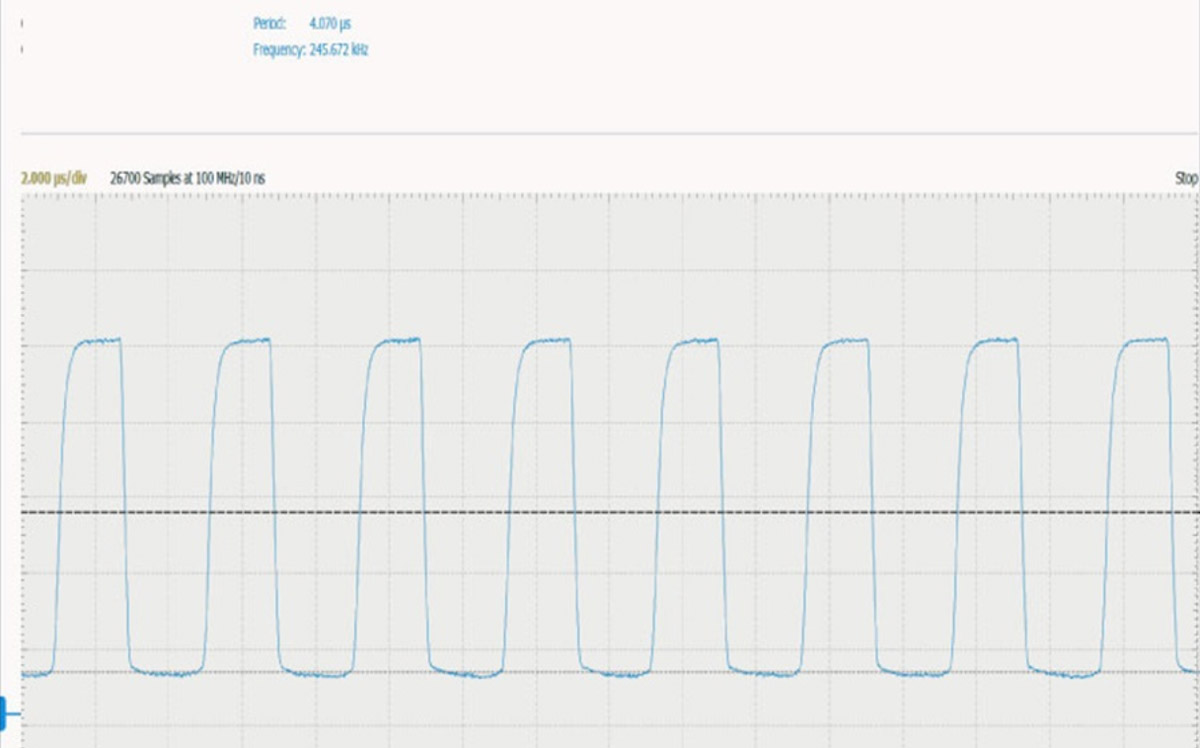

Na przykład, przy VIN ustawionej w środku zakresu na 2,5 V i podanych wartościach Rt Ct (2,5/(10 × 10 kΩ × 100 pF)), częstotliwość wyjściowa powinna być bliska 250 kHz. Należy sprawdzić, czy pomiary są zbliżone do tej wartości. Jeśli nie, należy ponownie sprawdzić połączenia i wartości elementów.

Rys. 4. Przebieg wyjściowy VFC

Krok 2 Wskazówki

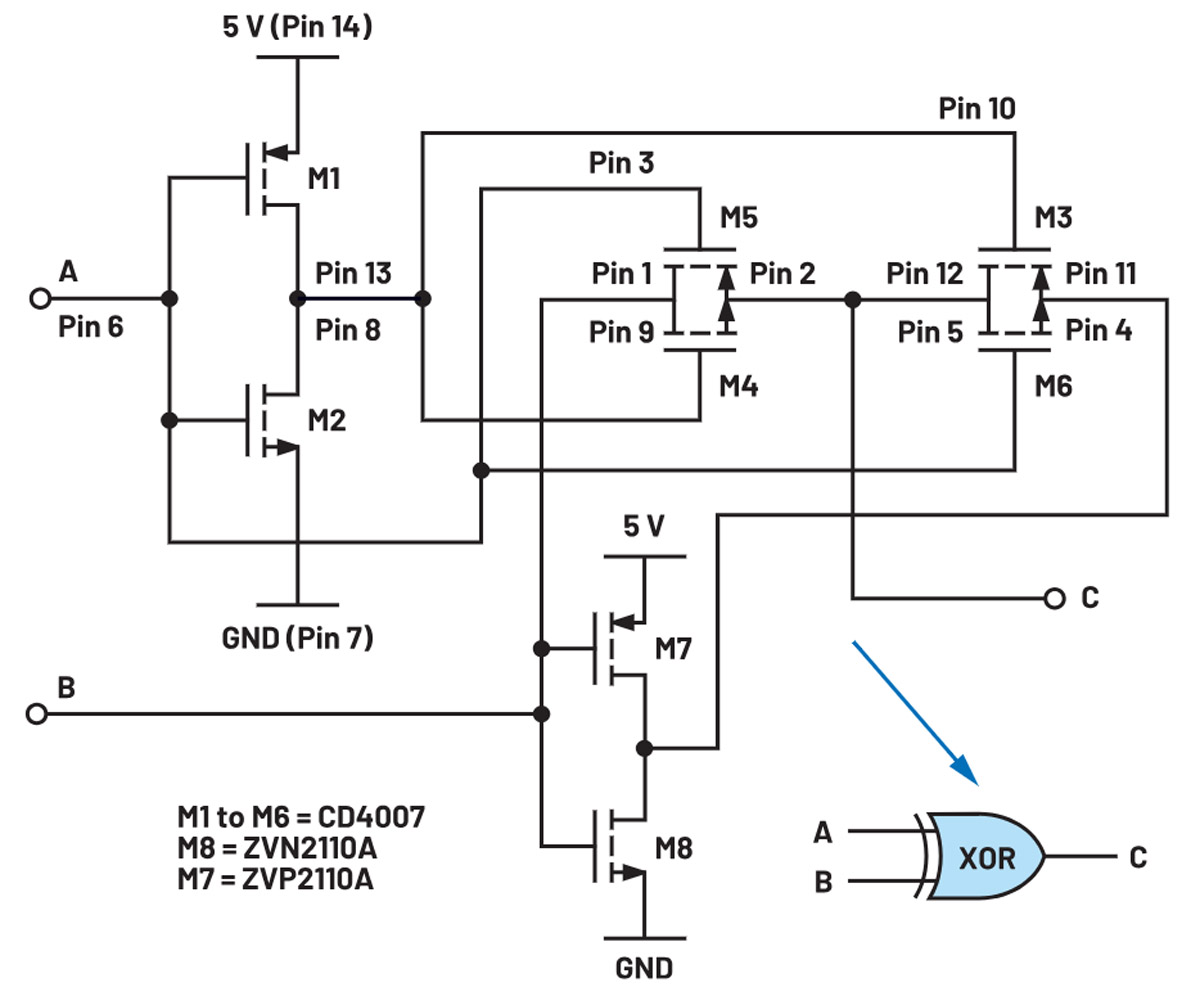

Teraz na płytce prototypowej należy zmontować obwód detektora fazy bramki XOR, jak pokazano na rys. 5. Po jej skonstruowaniu podłączamy ją do układu V-F, jak pokazano na rys. 6, tworząc tym samym kompletny układ PLL. Uwaga: przed dokonywaniem zmian w połączeniach należy odłączyć wszystkie napięcia zasilające (5 V i 9 V).

Rys. 5. Dodawanie detektora fazy XOR

Rys. 6. Kompletny układ PLL

Konfiguracja sprzętu

Włączamy zasilanie 5 V i dołączamy baterię 9 V. Podłączamy wyjście AWG1 do FREF, jak pokazano na rys. 4. Generator AWG1 ustawiamy w tryb generowania przebiegu prostokątnego o amplitudzie międzyszczytowej 5 V i offsecie 2,5 V (zmiany napięcia od 0 V do 5 V). Początkowo ustawiamy częstotliwość na wartość zmierzoną w kroku 1, gdy VIN było ustawione na 2,5 V (powinna wynosić około 250 kHz). Do wejścia FREF dołączamy wejście kanału CH1+ oscyloskopu, a do wyjścia VSQR kanał CH2+ oscyloskopu (rys. 6). Należy również uziemić wejścia CH1- i CH2-. Oscyloskop ustawiamy na wyzwalanie zboczem narastającym kanału 1 (sygnał FREF).

Rys. 7. Kompletny układ PLL na płytce stykowej

Procedura

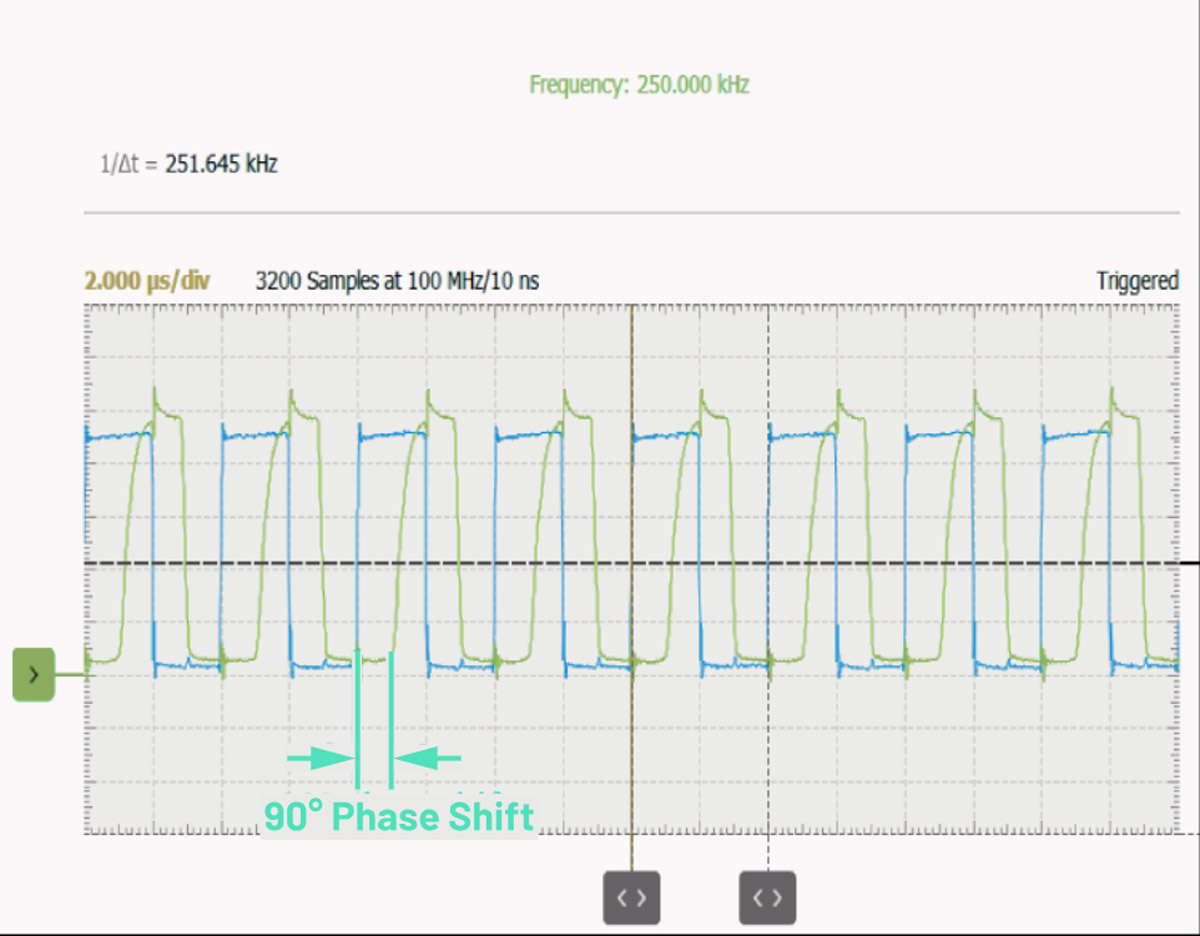

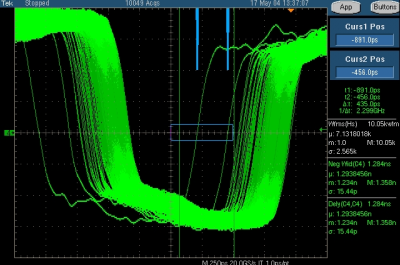

Po ustawieniu FREF na częstotliwość odpowiadającą napięciu sterującemu 2,5 V na nóżce 4 układu AD654, częstotliwość wyjściowa widoczna na VSQR powinna być zablokowana na wejściowej częstotliwości odniesienia FREF. Na ekranie oscyloskopu powinny być widoczne dwa stabilne przebiegi prostokątne (to znaczy zablokowane względem siebie), a przebieg VSQR jest przesunięty o około 90° w stosunku do FREF. Należy pamiętać, że gdy dwa wejścia detektora fazy są przesunięte w fazie o 90° filtrowane wyjście detektora fazy XOR będzie miało wartość połowy zakresu wyjściowego lub około 2,5 V.

Rys. 8. Kompletny wykres PLL FREF i VSQR.

Zwiększamy teraz i zmniejszamy częstotliwość odniesienia, FREF, w małych krokach. Pozwoli to określić minimalną i maksymalną częstotliwość, do której PLL będzie „chwytać”. Należy zwrócić uwagę na względną różnicę faz między FREF i VSQR podczas zmiany częstotliwości wejścia referencyjnego. Podczas wykonywania tej czynności trzeba zmierzyć przefiltrowane napięcie sterujące DC widoczne na nóżce 4 układu AD654 i porównać ten odczyt z wartościami zmierzonymi w kroku 1 podczas zmiany napięcia sterującego DC układu VFC.

Możemy teraz podłączyć kanał CH2+ oscyloskopu do wyjścia bramki XOR w punkcie C na rys. 6. Porównajmy widziany przebieg prostokątny z wejściami bramki XOR A (VSQR) i bramki B (FREF). Jak zmienia się kształt fali w punkcie C, gdy PLL jest zablokowany na minimalnej i maksymalnej częstotliwości chwytania w porównaniu z częstotliwością w środku zakresu chwytania?

Dodatkowy krok 3 – wskazówki

Prosty układ PLL z rys. 6 nie jest zbyt interesujący, ponieważ sygnał wyjściowy jest po prostu przesuniętą w fazie wersją sygnału wejściowego. Jeśli wstawimy blok dzielnika cyfrowego w pętli sprzężenia zwrotnego od wyjścia VFC do wejścia detektora fazy, jak widzieliśmy na rys. 1, wówczas sygnał wyjściowy będzie miał wyższą zwielokrotnioną częstotliwość. Korzystając z dowolnego dostępnego układu scalonego dzielnika cyfrowego, takiego jak CD4020, CD4040, CD4060 lub nawet SN7490 (prawie każdy układ scalony dzielnika będzie odpowiedni), otwieramy połączenie z wejściem XOR A i wstawiamy blok dzielnika, jak pokazano na rys. 9.

Rys. 9. Powielacz częstotliwości PLL

W zależności od współczynnika podziału N zbudowanego dzielnika, konieczna będzie zmiana częstotliwości wejściowej FREF o tę wartość. Na przykład, przy N = 8, jeśli FREF wynosiła wcześniej 250 kHz, nowa FREF będzie teraz wynosiła 250/8 lub 31,25 kHz. Częstotliwość impulsów na wyjściu detektora fazy bramki XOR będzie również ośmiokrotnie niższa.

Więcej informacji: analog.com/media/en/training-seminars/tutorials/MT-086.pdf

Źródło: analog.com/en/resources/analog-dialogue/studentzone/studentzone-december-2022.html

Autorzy oryginału: Antoniu Miclaus i Doug Mercer

Opracowanie: Jarosław Doliński

Opanuj jitter: pętle PLL nowej generacji

Opanuj jitter: pętle PLL nowej generacji  Jitter, pętle PLL, generacja sygnałów zegarowych – elementarz

Jitter, pętle PLL, generacja sygnałów zegarowych – elementarz  Syntezator Microwave PLLatinum LMX2594 TI – teraz w ofercie Mouser

Syntezator Microwave PLLatinum LMX2594 TI – teraz w ofercie Mouser